铁电场效应晶体管:原理、材料设计与研究进展

2012-11-14陆旭兵刘俊明

陆旭兵, 李 明, 刘俊明

(华南师范大学华南先进光电子研究院,广东广州 510006)

铁电场效应晶体管:原理、材料设计与研究进展

陆旭兵*, 李 明, 刘俊明

(华南师范大学华南先进光电子研究院,广东广州 510006)

系统阐述了铁电场效应晶体管(FeFET)的工作原理,重点介绍了铁电层和缓冲层的材料设计的基本原理、主要的铁电层材料和缓冲层材料及其所对应的FeFET的器件性能.并介绍了基于FeFET的FeCMOS逻辑电路、FeNAND闪存电路、基于氧化物半导体和有机半导体的FeFET的最新研究成果.最后对FeFET的未来研究作出展望.

非易失性存储器; 铁电场效应晶体管; 闪存; 有机半导体; 氧化物半导体

当代半导体工业使用的存储器件可以分为两大类[1].一类是易失性(volatile)的,即掉电后所储存的数据会丢失,如计算机的内存DRAM. 另外一类是非易失性(nonvolatile)的,即掉电后数据不会丢失,如计算机使用的EPROM、 EEPROM、便携式USB卡、相机SD卡所使用的闪存(flash memory)和交通系统使用的智能卡等,可以说非易失性存储器件已经成为了当代信息社会必不可少的电子产品,并且正在不断地提高我们的工作效率、改善我们的生活品质.随着集成电路技术在材料、制备工艺及设计技术等各方面的进步,商业化产品闪存的集成密度不断得到提高、价格也不断下降.随着集成电路技术按照摩尔定律不断向前发展,器件的尺寸持续缩小,相应地降低器件工作的电压、能耗等,对于目前基于电荷俘获技术的商业化闪存来讲,已经很难满足市场对更高集成密度和更低工作电压的下一代存储器件的需求.首先是它的写入电压较高(NOR:7~9 V, NAND: 17~19 V)、写入脉冲宽度较宽(10 μs),导致不仅写入消耗能量大,而且不利于快速操作;另外一个不足是反复擦写的能力不是很高,理论预期只有106数量级,实际的器件只有104次左右[1-3].为了进一步降低下一代存储器件的工作电压,提高器件的运行速度、稳定性和可靠性,最近10余年来,基于新材料和新工作原理的新型非易失性存储器件受到了广泛的关注.如铁电存储器件(Ferroelectric random access memory)(FeRAM)、磁阻存储器件(Magneto-resistive random access memory)、 相转变存储器件(Phase change random access memory)以及电阻存储器件(Resistive change random access memory)等[2-3].

作为下一代新型的存储技术之一,FeRAM具有超快的擦写速度(~100 ns)、极低的工作电压(1T1C结构: ~1 V)和优异的反复擦写能力(1012)等优点[2-3].从理论上预期,FeRAM有望克服闪存的不足之处, 不仅可以部分取代乃至提高现有非易失性存储器件的功能,而且可望拓展其在对功耗、可靠性要求较高的一些特殊领域得到应用,如移动电话及射频系统、汽车行驶记录仪等.对FeRAM的研究,是近10多年来国际工业界和学术界在半导体存储领域研究的热点之一, 从2001年起,FeRAM就已经被列入了国际半导体技术发展路线图 ITRS(International Technology Roadmap for Semiconductors)[2].美国和日本的大公司如富士通、松下、德州仪器,以及Ramtron等目前已经有基于FeRAM的智能卡、无线射频卡等商业化产品.根据器件结构及工作原理的不同,FeRAM又可以分为两大类[3]:1个晶体管1个电容器型(1T1C)和1个晶体管型(1T).目前基于1T1C结构的FeRAM已经实现了商业化生产,已知日本东芝公司于2009年初开发了“全球最大容量”128 Mbit,“全球最高速度”1.6 GB/s的FeRAM存储芯片产品.1T型的FeRAM,也即铁电场效应晶体管(Ferroelectric-gate field effect transistor),在本文中简称为FeFET,目前未实现商业化生产,但是从其器件结构及工作原理分析,FeFET不仅具有1T1C型的所有优点,而且其读出是非破坏性的,结构也较1T1C型的简单,预期比已经商业化的1T1C型FeRAM具有更高的集成密度、更低的能量消耗以及生产成本[4].根据日本富士通(Fujitsu)等国际著名半导体公司预测[5],FeRAM的最终发展趋势是FeFETs.

正是由于FeFET具有高速、低功耗、高集成密度和非破坏性读出等优点,在2010、2011年连续2年的国际半导体技术路线图中[2],FeFET与相转变存储器、磁阻存储器和电阻存储器等列为下一代的新型存储器.与目前商业化的NAND闪存比较,它有如下的优点[2-4]:1) 由于采用铁电极化来存储数据,理论上可以集成于10 nm工艺以下;2) 操作电压只需5 V左右, 大大低于NAND闪存所需要的15~20 V;3) 能耗可以降低9~16倍;4) 反复擦写能力达到108.可以说FeFET相对目前商业化的NAND闪存具有非常大的性能优势,在下一代高密度存储技术中具有非常广阔的应用前景.本文力争从铁电场效应晶体管的基本工作原理出发,对其材料设计的基本要求、目前的研究进展、存在的问题和未来的发展趋势作出一个较为全面的阐述.

1 FeFET的工作原理

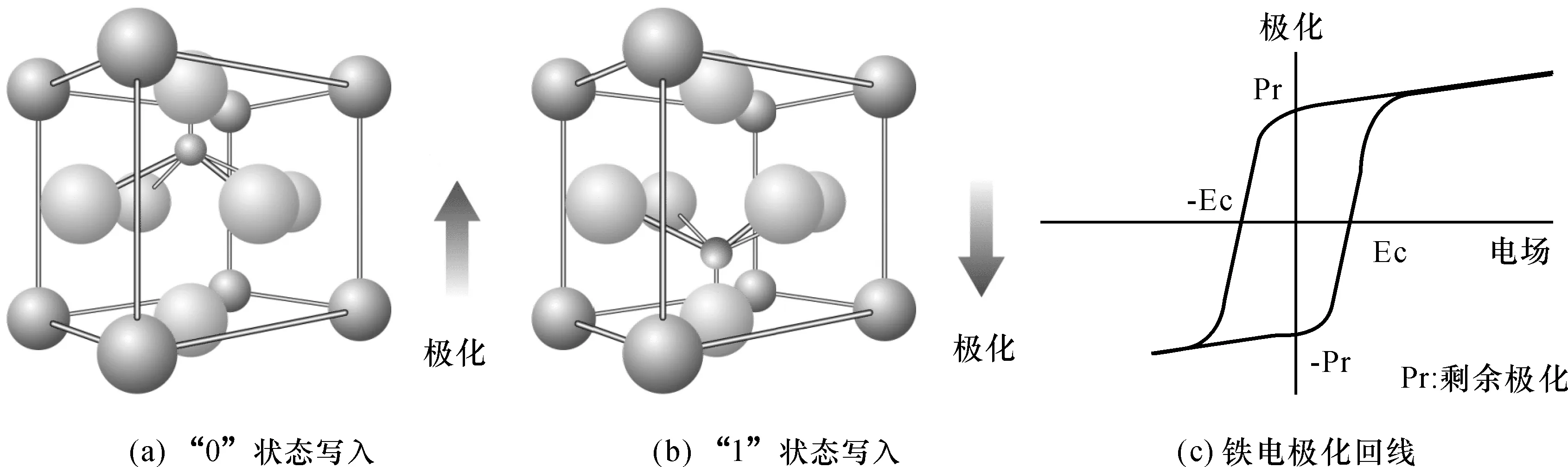

1.1 铁电材料

铁电场效应晶体管之所以能够具有存储效应,其核心的机理在于作为栅介质材料的铁电材料具有剩余极化.铁电材料是指一类具有自发极化的材料,并且自发极化可以在外加电场下翻转.当外加电场消失后,自发极化有一部分并没有随外加电场的消失而消失,这部分保留下来的极化称为剩余极化.正是因为剩余极化的存在,当外加电场消失后,晶体管中的沟道表面仍然能够保持在积累或者反型的状态,从而保留了沟道的开关状态.铁电材料典型的晶体结构如图1所示.一般来说,材料的铁电性只存在于某一温度以下,称为居里温度.在这个温度以上,材料变为顺电体.常见的铁电材料有BaTiO3、PbZrxTi1-xO3、SrBi2Ta2O9和BiFeO3等.

图1 铁电材料的晶体结构及极化翻转示意图

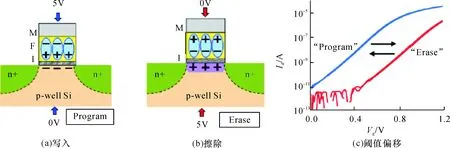

1.2 FeFET的结构及其工作原理

利用铁电材料来实现存储效应的想法最早由ROSS[6]提出,其后,MOLL等[7]首次实现具有存储性能的FeFET器件.1974年,WU等[8]首先尝试在Si衬底上制备铁电场效应晶体管.在早期的研究中,铁电薄膜直接制备于Si衬底上边,得到一个金属-铁电-半导体(Metal-Ferroelectric-Semiconductor,MFS)的器件结构,传统MOSFET中的SiO2绝缘层被铁电层替代,利用铁电极化的翻转来控制沟道电流的开关.但是直接制备于Si衬底上的FeFET的电荷长期保持性能很差,严重制约了其进一步的性能提高.研究人员发现影响电荷长期保持性能的关键原因是很难在多晶的铁电薄膜和硅衬底之间形成一个性能优异的电学界面[3-4].为了提高界面质量,一个最常用的策略是在铁电薄膜和Si衬底之间插入一绝缘的缓冲层,形成所谓的金属-铁电-绝缘-半导体(metal-ferroelectric-insulator-Si,MFIS)结构.这一绝缘层不仅能够阻止Si衬底与铁电薄膜在高温下的界面反应和相互之间的扩散,而且可以提供一个较高的势垒以降低从Si衬底到铁电薄膜的电荷注入,可以极大地提高器件的长期稳定可靠性.

图2是一个基于MFIS结构的FeFET的基本结构及擦、写工作示意图.FeFET由金属电极/铁电/缓冲层/半导体(MFIS)这样一个多层结构组成.当在栅上施加一个正的写入电压时,沟道表面形成反型层,在源漏之间形成电流的通道,对应着器件的写入过程;当在栅上施加一个负的擦除电压时,沟道表面形成积累层,在源漏之间的电流通道被截断,对应着器件的擦除过程.图2(c)展示了擦写操作所导致的器件阈值电压的偏移,对应着器件的存储窗口的大小.擦写脉冲电压的大小、宽度以及存储窗口的大小与器件所使用的铁电层材料、绝缘层材料以及各层的物理厚度、界面质量等密切相关.

图2 铁电MFIS结构示意图及工作原理

2 FeFET中的材料设计和研究进展

2.1 FeFET结构中铁电材料的探索

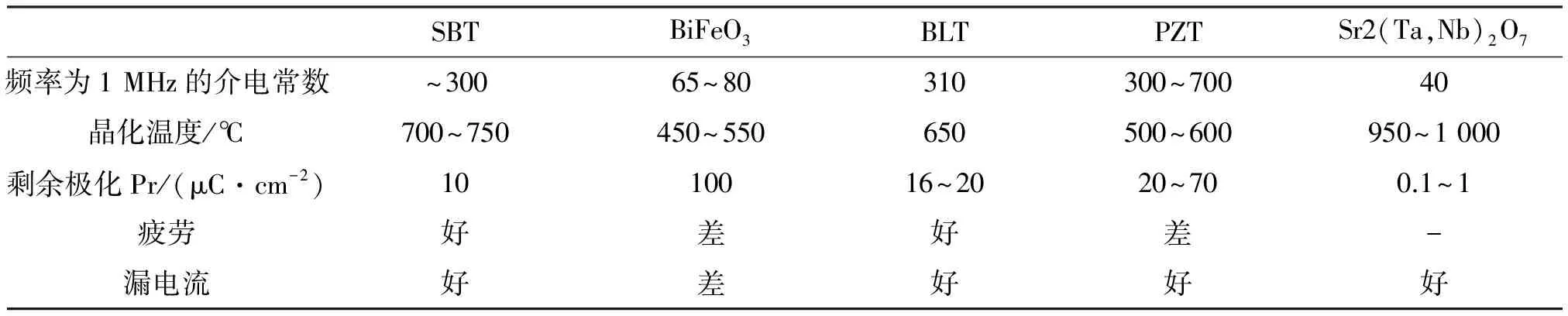

表1 FeFET中常用铁电材料性能比较Table 1 Comparisons of the basic physical and electrical properties of the typical ferroelectric materials for FeFET

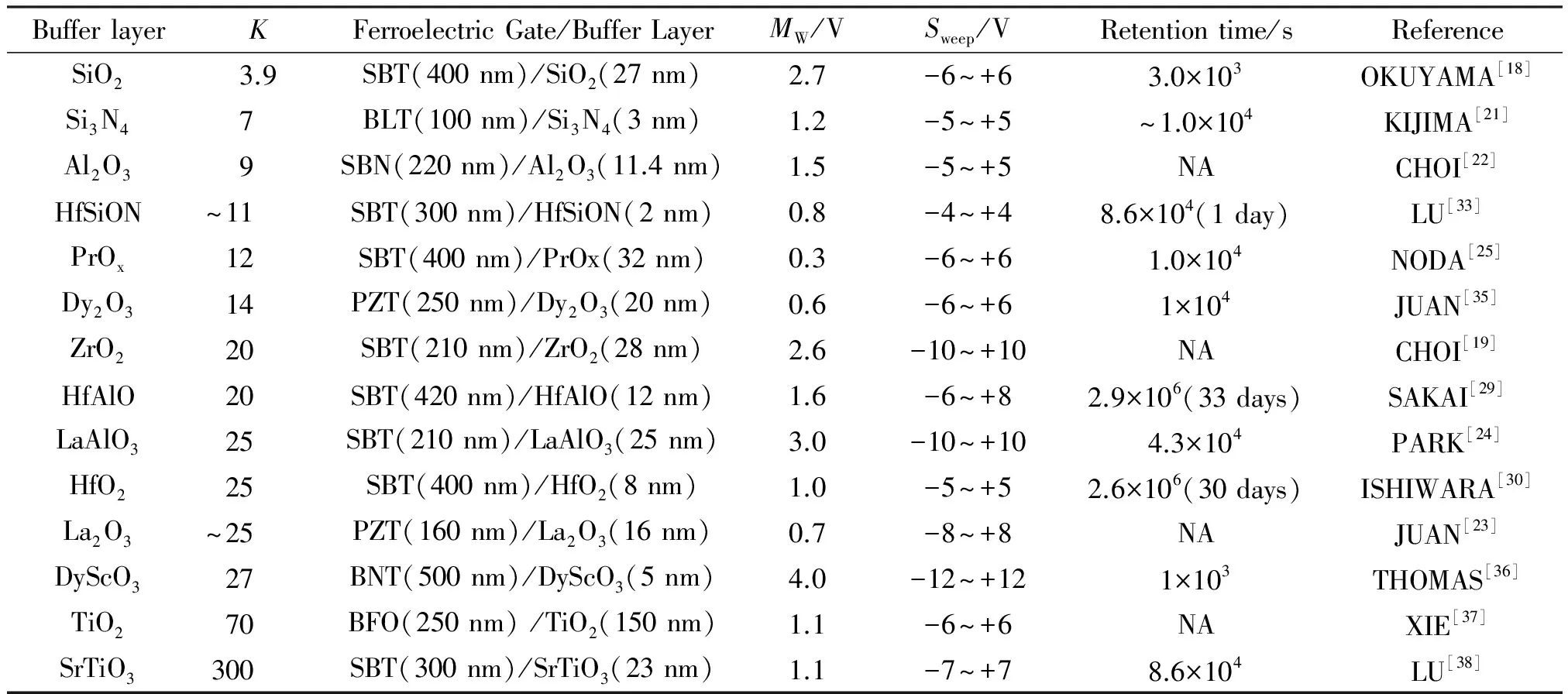

2.2 FeFET结构中的绝缘缓冲层的探索

在MFIS结构提出之初,其结构中的绝缘层通常采用的是SiO2,因为通过热氧化的方法很容易在Si衬底上制备高质量的SiO2层,SiO2/Si体系在CMOS电路中已经研究得很透彻.但是由于MFIS结构本身存在的一些固有缺陷,即去极化场和绝缘层的分压效应[11],基于SiO2的MFIS器件的性能不好,特别是保持时间很短.为了提高器件的性能,通常绝缘层采用具有高介电常数的高K栅介质材料作为缓冲层.通过对以往研究工作的总结,FeFET中的绝缘缓冲层材料不仅需要具有较高的介电常数,最好还具有高的能隙、与Si衬底之间具有良好的热稳定性和非晶或外延的结构[11].

1994年开始,研究工作者开始尝试以各种不同的制备方法来制备各种不同的高K缓冲层材料,在Si基上制备MFIS并研究其器件性能.关于各种高K材料的一些基本物理和电学性能如介电常数、能隙、与Si之间的热稳定性、能带结构以及各自的优缺点,在WILK等[12]的综述里已经有详细的介绍,这里不再贽述.对FeFET中高K缓冲层材料的研究,大致可以分为2个阶段.

2000年之前,对高K缓冲层的研究主要集中在CeO2[13]、TiO2[14]、ZrO2[15]、SrTiO3[16]和YMnO3[17]等材料.相对于没有缓冲层的MFS器件和以SiO2为缓冲层的MFIS器件,器件的性能都得到了不同程度的改善.如HIRAI[13]报道了电子束蒸发制备的CeO2为缓冲层的Al/PbTiO3(81 nm)/CeO2(18 nm)/Si结构,其器件的保持性能大大提高到了1×105s.而以SiO2为缓冲层的MFIS器件,其电荷保持时间只有3×103s[18].YMnO3具有较高的介电常数30(块体陶瓷),与Si衬底之间具有良好的热稳定性,并且钇具有分解Si表面形成的SiO2的作用.CHOI等[17]研究了Pt/SBT (200 nm)/YMnO3(25 nm)/Si结构的电学性能,在6 V的扫描电压下观测到了1.5 V的存储窗口,并且展示了比CeO2更好的阻止铁电材料与Si衬底之间相互扩散的能力.遗憾的是Choi的工作里没有报道器件保持性能的结果.对于这些早期研究的高K缓冲层材料,虽然其MFIS器件性能获得了一些令人鼓舞的结果,但是其总体的电学性能还远没有达到商业化生产的要求.究其原因,主要与这些材料的一些本征性质有关,如与Si衬底之间的导带价带偏移过小[14,16]、晶化温度低[14-15]、热稳定性[13-16]等.

2000年开始,对高K缓冲层的研究重点开始转向ZrO2[19]、Ta2O5[20]、Si3N4[21]、Al2O3[22]、La2O3[23]、LaAlO3[24]和PrOx[25]等材料,与之相应的是令人鼓舞的结果也不断出现.如CHOI等[22]研究了以Al2O3为缓冲层的Pt/SrBi2Nb2O9(SBN)(220 nm)/Al2O3(11.4 nm)/Si MFIS器件,在5 V的工作电压下获得了1.52 V的存储窗口,足以满足低压工作的需求.WON等[23]采用La2O3为缓冲层,对于Al/PbTiO3(360 nm)/La2O3(28 nm)/Si结构,当扫描电压从2 V增加到10 V时,相应的存储窗口从0.3 V增加到2.6 V.令人遗憾的是,虽然WON等[23]的器件存储窗口很大,但是他们并没有电荷保持特性的报道.PARK等[24]报道了Pt/Sr0.8Bi2.2Ta2O9(210 nm)/LaAlO3(25 nm)/Si MFIS器件,不仅在10 V的扫描电压下观测到了3.0 V的存储窗口,而且报道了约12 h的电荷长期保持能力.NODA等[25]报道了用脉冲激光沉积法制备的具有优异绝缘性能的PrOx缓冲层,其对应的MFIS器件的电荷保持性能超过了1×104s,但是不足的是其存储效应很小,在12 V的扫描电压下仅仅观测到了0.3 V的存储窗口.

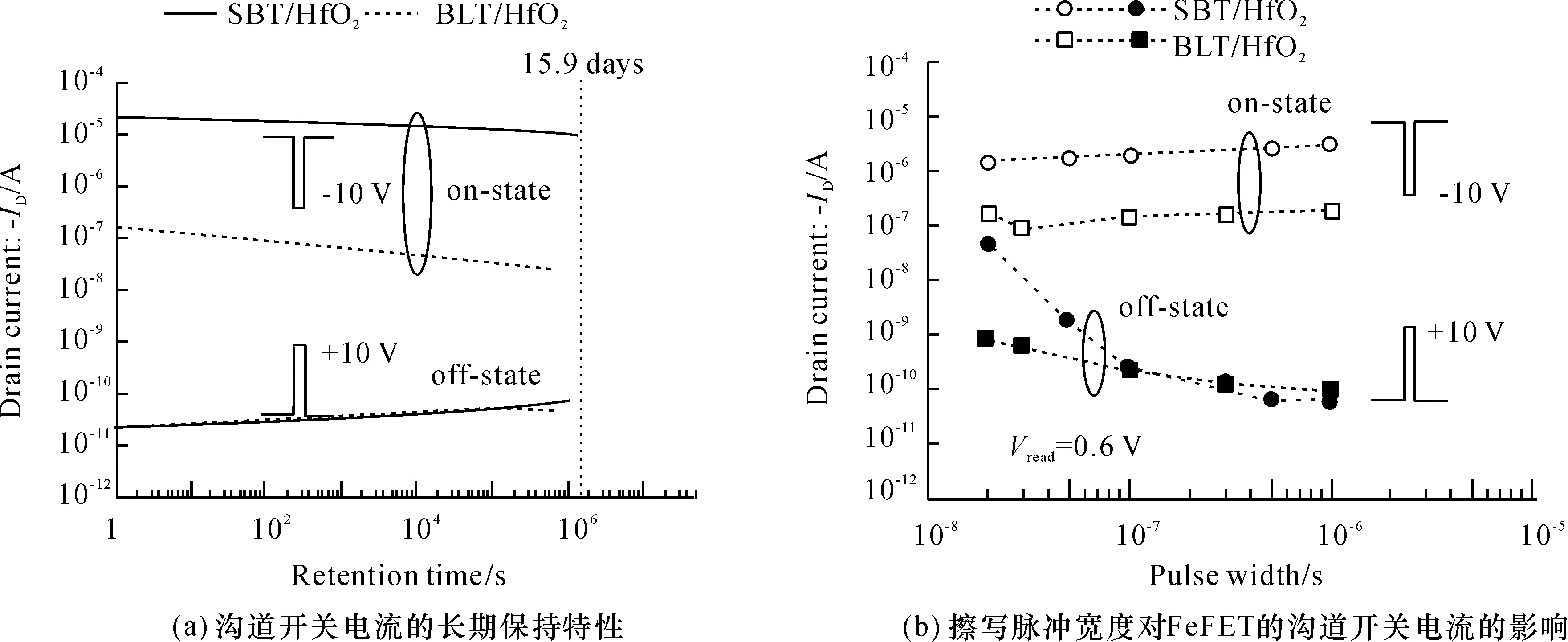

通过对上述的各种高K缓冲层材料的广泛研究,MFIS结构器件的电学性能得到了很大的改善.但是还没有找到一种真正能够将FeFET的电学性能推进到可以商业化生产水平的缓冲层材料,商业化生产需要器件的长期电荷保持能力能达到10年[26].直到2004年,通过日本产业技术综合研究所SAKAI教授组和东京工业大学ISHIWARA教授组的努力,首次将HfO2系列材料引入到MFIS结构中来,器件的电学性能特别是电荷长期保持特性得到了极大的改善,才真正使FeFET的商业化生产看到了一丝曙光.在2004年,SAKAI教授组报道了基于Pt/SrBi2Ta2O9/HfAlO/Si MFIS结构的优异的电学性能[27].在6 V的扫描电压下获得了1.6 V的存储窗口,如图3(a)所示.尤为重要的是,经过12天的保持测试,沟道的开关电流比仍然保持在106以上,如图3(b)所示.同样是在2004年,ISHIWARA教授组报道了以HfO2为缓冲层的Pt/SrBi2Ta2O9/HfO2/Si器件优异的电学性能[28].经过15.9天的长期电荷保持测试后,FeFET的沟道电流开关比仍然保持在105以上.他们也同时报道了20 ns的超快器件工作速度,相应的结果如图4所示.这是过去几十年中在FeFET的研究中2个标志性的工作.自HfO2基缓冲层材料引入后,FeFET的电学性能特别是长期保持特性得到了质的飞跃.随后SAKAI教授组于2005年采用自对准栅技术,所制备的基于HfAlO为缓冲层的FeFET在实验室阶段实现了超过33天的电荷保持能力,且沟道电流开关比保持在105以上[29].2005年,ISHIWARA教授组进一步优化了以HfO2为缓冲层的FeFET,其长期电荷保持能力也达到了30天以上[30].HfO2和HfAlO作为缓冲层在MFIS结构中虽然取得了巨大的成功,但是这2种材料也存在各自的不足.如HfO2的晶化温度较低,只有300 ℃, 容易在铁电薄膜的晶化过程中形成多晶结构,这种多晶结构易于在界面产生缺陷,使界面的陷阱电荷增加并且会导致漏电流增加.HfAlO虽然晶化温度高,但是容易在界面引入负的固定电荷[31].为了克服HfO2和HfAlO的不足之处,进一步提高器件的性能,作者在日本东京工业大学时与富士通公司合作探索了HfO2基的新型缓冲层材料[32-33].如利用超高真空的分子束沉积的方法制备了高质量的HfTaO高K薄膜,HfTaO不仅具有与HfO2相同的介电常数(~25),而且其晶化温度达到800 ℃,有效地克服了HfO2的晶化温度低的缺点[34].制备的以HfTaO作为缓冲层的MFIS结构二极管电容器和FeFET器件,都展示了优异的器件性能[32].另外一种高K材料HfSiON不仅具有比HfO2高的晶化温度(大于800 ℃),而且不会在界面引入负的固定电荷.LU等[33]系统研究了HfSiON的厚度对器件性能的影响,发现2 nm的HfSiON缓冲层能够获得最大的存储窗口,但是HfSiON的介电常数较小(约为10),限制了器件获得更大的存储窗口.为了克服HfO2和HfAlO的不足之处,在最近的几年中,人们也尝试了其他新型的高K缓冲层材料,如Dy2O3[35]、DyScO3[36]等,但是报道的器件电学性能远远比以HfO2基为缓冲层的FeFET差.可以说通过多年的探索,HfO2基高K缓冲层材料已成为FeFET研究中最合适的缓冲层材料.究其原因,HfO2是目前为止唯一能够较好满足MFIS结构中绝缘缓冲层要求的材料.如具有较高的介电常数、与Si衬底之间优异的热稳定性和界面质量,器件的漏电流性能、界面缺陷、界面低介电常数层能够得到最大限度的抑制,从而可以使器件能够低压、高速长期稳定工作.表2是近年来所研究的各种不同的高K缓冲层材料及其对应的FeFET的性能比较,可以对FeFET研究的现状有一个较为全面的了解.

图3 基于HfAlO为缓冲层的Pt/SrBi2Ta2O9/HfO2/Si FeFET的电学特性

图4 以HfO2为缓冲层的FeFET器件的长期保持特性和脉冲写入特性

表2 不同高K缓冲层及其对应的FeFET电学性能比较Table 2 Comparisons of the electrical properties of FeFETs with different high-K buffer layers

注:K为频率为1 MHz的介电常数.

2.3基于FeFET的FeCMOS和FeNAND存储电路研究

经过多年的努力,采用HfAlO为缓冲层,FeFET已经可以稳定可靠地获得优异电学性能[4,29-30],特别是单个的器件的预期电荷长期保持性能已经可以达到10年.学术界已经开始了基于FeFET的电路应用研究.目前已经在2个方向取得了重要的进展[4]:1个是基于FeFET的非挥发性逻辑电路(FeCMOS),1个是基于FeFET的NAND闪存(FeNAND).

1.1.4 心肌穿孔 心肌穿孔的发生率<1%,主要发生在右心室。心肌穿孔引起的心包填塞则是十分凶险的并发症,也是永久起搏器植入术后最严重并发症。

FeCMOS电路与常规的CMOS电路具有相同的电路结构,只不过其中的n-MOSFET和p-MOSFET分别由n沟道的FeFET和p沟道的FeFET来替代.其优点是通过对栅压的控制可以同时实现逻辑晶体管和非易失性存储记忆晶体管的功能,在下一代高速低能耗的移动电子器件中具有优良的应用前景.当栅压很小时,FeFET中的铁电材料的极化不能够实现翻转,从而没有存储效应,这样晶体管就可以作为一个没有记忆效应的普通MOSFET来使用.当栅压增加到某一阈值时,FeFET中的铁电材料开始极化翻转,输出电压出现平移.2008年AIST的SAKAI教授组已经成功实现了基于FeFET的FeCMOS反相器[39],展示了FeFET作为逻辑器件应用的可能性.详细的工作原理和更多的结果可参阅有关文献[4,39].

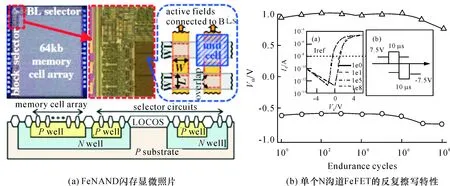

NAND闪存是目前高密度存储器市场上的主流产品,但是其工作电压过高(一般需要20 V),实际反复擦写能力只有约104次,很难满足未来低压、高可靠、高密度器件的需求.FeFET具有完全不同于常规NAND闪存的工作原理,理论预期可以克服常规NAND闪存的高工作电压和低反复擦写能力的不足.FeNAND具有与常规的NAND一样的电路结构,唯一的区别在于用FeFET来取代基于浮栅电荷写入方式的MOSFET来作为记忆效应的晶体管.最近几年,基于FeFET的FeNAND闪存电路已经取得了很多的进展.2个代表性的工作: (1) 2011年,MIYAJI等[40]报道了9.3 Gb/s高速写入速度、且能耗比常规的flash低86%的FeNAND闪存;(2)SAKAI教授组于2011年成功实现了64 kb的FeNAND闪存电路[41].其工作电压可以降低到7 V,反复擦写能力达到108,预期电荷长期保持能力达到10年[41].具体的结果见图5.结果表明:FeFET完全可以与当前的CMOS工艺兼容;已经从单个的器件研究阶段,进入到了实现产品商业化生产的电路研究阶段,基于FeNAND的优异的电学性能,展示了其在未来的主流非易失性存储器件产品中优异的应用前景.

图5 世界上第一片64 k位FeNAND的显微照片及器件电学特性结果

2.4 新型半导体沟道FeFET器件结构

一般来讲,FeFET通常指的是制备于Si基半导体上的FeFET,是目前FeFET研究的主流器件结构.除了Si基的FeFET外,还有一类基于薄膜晶体管结构的FeFET器件,采用有机半导体、氧化物半导体、石墨烯和碳纳米管为沟道.由于具有一些Si基FeFET所不具备的优点,在近年来也受到了研究工作者的关注.这种采用薄膜晶体管器件结构的FeFET,铁电层先于半导体层制备,可以避免Si基FeFET在铁电层的高温晶化过程中界面低介电常数层的产生,铁电层与半导体层的相互扩散等问题,甚至可以不需要界面绝缘缓冲层,可以有效克服去极化场效应和提高器件的擦写效率.但是有机半导体和氧化物半导体的载流子迁移率远小于Si,源漏电极与半导体层的接触电阻问题,以及这些新型的半导体与铁电层的界面问题远没有铁电/Si界面研究得清楚,使得器件性能与Si基的FeFET相比还有差距,但为FeFET的应用提供了新的思路和方向.下面主要介绍2种典型的薄膜晶体管型FeFET.

2.4.1 有机铁电场效应晶体管 有机FeFET可以分为2种类型.一种是铁电材料采用有机铁电薄膜,但是仍然制备在Si衬底上形成MFIS结构.由于有机铁电薄膜的晶化温度一般低于200 ℃,如poly(vinylidene fluoridetrifluoroethylene)(P(VDF-TrFE))的晶化温度约140 ℃,所以在Si衬底和缓冲层之间几乎不存在界面反应,使器件的操作电压大大降低.在已知的各种有机铁电材料中,PVDF及其共聚物P(VDF-TrFE)具有相对大的剩余极化、较短的极化翻转时间以及良好的热稳定性等优点,是目前有机铁电存储器中使用最广泛的有机铁电薄膜[42].这种基于有机铁电薄膜的MFIS型FeFET,虽然其工作电压很低[10],但是器件的写入速度以及其在空气中的稳定性问题仍然有待于深入探索.

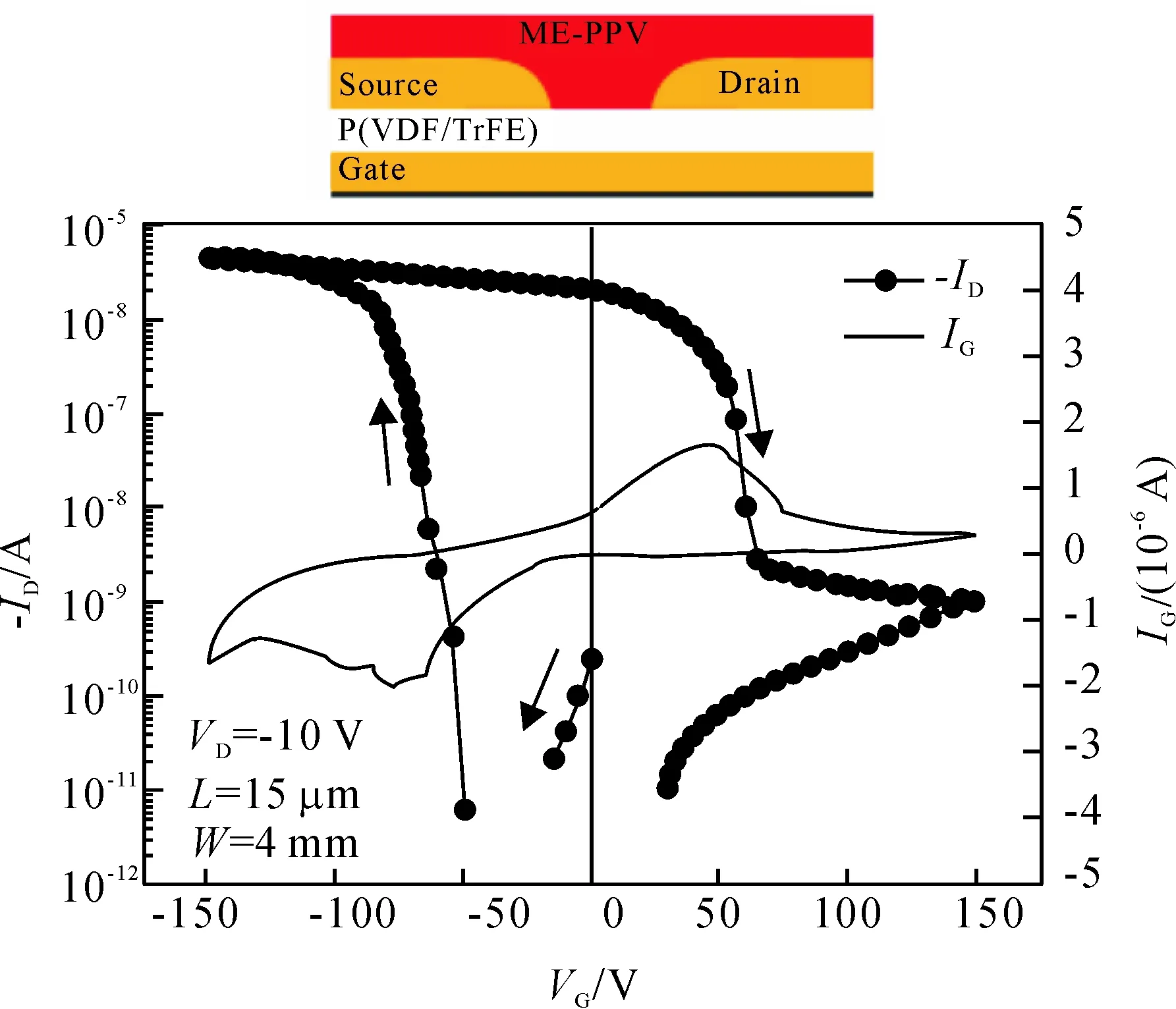

另外一种有机FeFET采用的是薄膜晶体管型结构,以有机聚合物半导体或有机小分子作为半导体层,通常采用有机铁电薄膜为铁电层.这种结构的好处是可以结合有机柔性电子器件的所有优点和铁电材料的优点,在未来的柔性电子器件中具有良好的应用前景.2005年,NABER等[43]首次研究了聚合物半导体MEH-PPV [poly(2-methoxy,5-(20-ethylhexyloxy)-p-phenylenevinylene]为沟道,以P(VDF-TrFE)为有机铁电层的有机FeFET.图6展示了Naber等人工作里的有机聚合物半导体FeFET器件示意图及其器件的转移特性.这种新型的有机FeFET也展示了优异的长期保持特性.其他类型的聚合物半导体如rr-P3HT [regioregular poly(3-hexylthiophene)]具有比MEH-PPV更高的载流子迁移率,在其后的研究中逐渐取代了MEH-PPV作为有机FeFET中的半导体沟道.有机FeFET有时也采用有机小分子半导体作为沟道,研究较多的是并五苯(pentacene),但是其与P(VDF-TrFE)之间的界面匹配不好,导致pentacene沟道载流子下降,目前报道[44]的最高载流子迁移率仅为0.1 cm2V-1s-1.

图6 有机聚合物FeFET的器件结构示意图及沟道电流-柵压转移特性

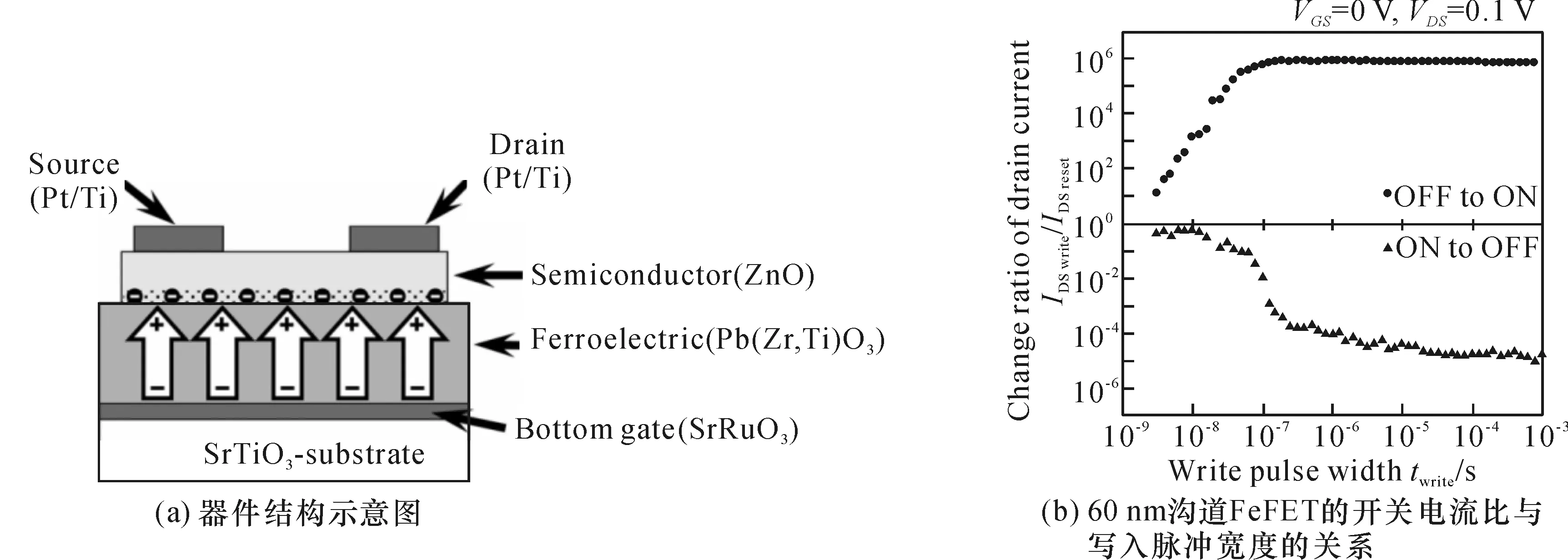

2.4.2 氧化物半导体铁电场效应晶体管 另外一种薄膜晶体管类型的FeFET是基于氧化物半导体的FeFET.这种FeFET的典型结构如图7(a)所示,是日本松下公司的KANEKO等[45]制备的基于ZnO为沟道的FeFET器件.采用单晶SrTiO3作为衬底,在其上可以很容易实现背栅电极SrRuO3和铁电层Pb(Zr,Ti)O3的异质外延.KANEKO等采用电子束光刻的方法,成功制备了ZnO沟道长度仅为60 nm的FeFET器件,是目前已知报道的最小尺寸的FeFET.对于Si基FeFET,已报道的最小的器件尺寸为560 nm[46].通过外延铁电薄膜和减小器件的尺寸,FeFET的工作速度大大提高了,写入的脉冲宽度可以达到10 ns,如图7(b)所示;最近,KANEKO等[47]制备了基于ZnO/PZT/SRO/STO双栅结构的FeNAND闪存电路,不仅在实验室阶段直接测试到了3.5月的优异长期保持特性,而且这种新型的FeNAND电路中相邻器件之间几乎没有相互的干扰.虽然氧化物半导体FeFET理论上预期有很多Si基FeFET不具有的优点,但是目前总体性能仍然没有Si基的FeFET好,如工作电压一般都在10 V左右.造成其工作电压较高的可能原因是器件中氧化物半导体与源漏电极之间很难形成良好的欧姆接触,在这里分掉了一部分栅压.氧化物半导体FeFET面临的另外一个问题是若要实现铁电层的外延,必须使用与铁电薄膜晶格匹配的钙钛矿氧化物单晶衬底,这种单晶衬底的成本很高,对大面积规模化的生产带来了挑战.

图7 基于氧化物半导体的FeFET的器件结构示意图及典型的电学特性

3 FeFET未来的研究展望

通过60多年的研究,对FeFET的工作原理、存在的问题以及蕴藏于其中的诸多物理机制,已经理解得非常透彻.幸运的是通过对基于Pt/SBT/HfAlO体系的一个系统研究,FeFET的单个器件性能已经得到质的飞跃,目前从单个器件的研究开始向基于FeFET的FeCMOS逻辑器件和FeNAND闪存电路迈进,展示了FeFET的良好的商业化生产的前景.未来的研究中,以下方面仍然有值得探索的必要.

3.1 新材料方面

(1)铁电材料.虽然SBT在FeFET中已经取得了巨大的成功,但是SBT的晶化温度很高(常用的晶化温度为750 ℃),在长时间高温晶化过程中很容易在界面生成低介电常数的氧化物层,对器件的工作电压和工作速度等性能不利.如果能降低铁电薄膜的晶化温度,则可以进一步降低器件的工作电压,提高工作速度.BFO的晶化温度较低,但是BFO漏电流很大,已有的实验结果证明其在FeFET中基本上不可取.有机铁电薄膜具有低介电常数和低晶化温度,理论上可以克服无机铁电薄膜高晶化温度和高介电常数的缺点,但是对有机铁电薄膜与Si衬底之间的界面问题、有机铁电薄膜在空气中的稳定性问题的理解还不是很深入.因此,探索新型的有机铁电薄膜材料,深入理解有机铁电薄膜与Si之间的界面特性,研究新型有机铁电薄膜与Si基的器件工艺集成都将是非常有意义的工作.

(2)新型沟道材料方面.有机柔性非易失性存储器是未来全柔性电子器件中一个新兴的研究方向,制备有机铁电薄膜与有机半导体结合起来的全柔性FeFET将是一个非常有意义的工作,目前这方面开始了初步工作,器件的性能还有很大的提升的空间.基于氧化物半导体的FeFET已经展示了某些优异的电学性能,为了进一步降低其工作电压,如何提高氧化物半导体沟道中的载流子的迁移率,降低源漏电极与沟道的接触电阻仍然值得进一步研究.目前的氧化物半导体沟道采用多晶的ZnO、ITO等材料,采用外延的氧化物沟道实现全外延氧化物半导体FeFET是一个值得期待的研究课题.

3.2 新应用方面

目前FeFET的研究集中于民用领域.有一个不太引起注意的优点:很好的抗辐射能力.适合于国防、航空航天等复杂环境中常规闪存不能应用的领域.因此对铁电薄膜和FeFET的抗辐射研究将是很有意义的课题,但是目前的研究不多,国内的湘潭大学在这个方向做出了一些初步的研究[48].

最近,ITRS2010分析指出,FeFET可以用来构建静态随机存取存储器(FeSRAM),这种新型的FeSRAM具有比常规的SRAM更低的工作电压和更低的能耗.目前的研究刚刚起步,在这个方向还有很大的拓展空间.

3.3 器件的小尺寸和高密度集成研究

目前已知报道的Si基FeFET的最小器件尺寸是0.56 μm[46],为了实现FeFET集成到16 nm及以下工艺中去,其器件尺寸也必须相应地持续缩小,对应的铁电层的物理厚度也必需相应减小.虽然从理论[49]和实验[50]上已经证明,当铁电薄膜的物理厚度减小到几个原子层时,仍然可以观测到铁电极化效应.但是对于FeFET器件,由于电荷注入效应的存在,对于具有超薄铁电层的MFIS结构,是否能够观测到存储效应,目前还不清楚.国际上已知报道的Si基MFIS结构里采用的最薄铁电层是80 nm,在±4 V的扫描电压下仅仅观测到0.2 V的存储窗口[51].对于厚度为80 nm以下铁电层的MFIS结构,是否仍然能够获得存储效应是一个疑问.因此如何在当铁电层非常薄的情况下使MFIS结构获得足够大的存储窗口对于器件的小型化尤为重要,需要从材料组合、材料及器件的制备工艺等多方面继续做出探索.目前已报道的最大的FeNAND是64 k位,未来在这个基础上需要进一步提高FeNAND的集成度,学术界和工业界需要在电路设计、小尺寸器件的制备工艺等方面继续努力.

当器件的尺寸很小、集成密度很高时,相邻器件之间的寄生电学耦合,相邻器件之间的读写干扰会干扰电路的正常工作[52].东京工业大学的ISHIWARA教授组提出了一种2T的结构力图解决这个问题,虽然提高了其抗干扰的能力,但是FeFET的器件性能也下降了.因此,如何从优化电路设计等方面提出解决小尺寸器件之间的干扰问题的新思路也是未来值得继续探讨的课题.

[1] KANG Sung-Mo,LEBLEBICI Yusuf.CMOS digital integrated circuits: Analysis and design[M]. New York:Mc Graw Hill, 2005.

[2] Semiconductor Industry Association. The international technology roadmap for semiconductors.[2012-04-25].http://public.itrs.net/.

[3] FUJISAKI Y. Current status of nonvolatile semiconductor memory technology[J].Jpn J Appl Phys,2010,49:100001.

[4] SAKAI S, TAKAHASHI M. Recent progress of ferroelectric-gate field-effect transistors and applications to nonvolatile logic and FeNAND flash memory[J].Materials, 2010,3:4950.

[5] MARUYAMA K, KONDO M, SINGH S, et al. New ferroelectric materials for embedded FRAM LSIs[J]. FUJITSU Sci Tech J, 2007, 43: 502.

[6] ROSS I M. Semiconductive translating device:USA, 2791760[P]. 1957-05-07.

[7] MOLL J L, TARUI Y. A new solid state memory resistor[J].IEEE Trans Electron Devices, 1963,10:338.

[8] WU S Y. New ferroelectric memory device metal-ferroelectric-semiconductor transistor[J]. IEEE Trans Electron Devices, 1974, 21: 499.

[9] LU X B,ISHIWARA H. Improved electrical properties of Sr0.8Bi2.2Ta2O9films by ZrSiO4doping for low voltage operations of metal-ferroelectric-insulator-Si devices[J]. J Appl Phys, 2009,105: 061626.

[10] LU X B, YOON J W, ISHIWARA H. Low-voltage operation and excellent data retention characteristics of metal-ferroelectric-insulator-Si devices based on organic ferroelectric films[J]. J Appl Phys, 2009,105:084101.

[11] LU X B. High-k gate dielectric for next generation memory device applications[M]. Weinheim: Wiley-VCH Verlag GmbH & Co, 2012:473-499.

[12] WILK G D, WALLACE R M, ANTHONY J M. High-k gate dielectrics: Current status and materials properties considerations[J]. J Appl Phys, 2001, 89: 5243.

[13] HIRAI T, TERAMOTO K, NAGASHIMA K, et al. Characterization of metal/ferroelectric/insulator/semiconductor structure with CeO2buffer layer[J]. Jpn J Appl Phys, 1995, 34:4163.

[14] BYUN C, KIM Y I, LEE W J, et al. Effect of a TiO2buffer layer on the CV properties of Pt/PbTiO3/TiO2/Si structure[J]. Jpn J Appl Phys, 1997,36: 5588.

[15] LIM M, KAL KUR T S. Electrical characteristics of PT-bismuth strontium tantalite (BST)-P-SI with zirconium oxide buffer layer[J]. Integr Ferroelectr, 1997,14:247.

[16] TOKUMITSU E,NAKAMURA R,ISHIWARA H. Nonvolatile memory operations of metal-ferroelectric-insulator-semiconductor (MFIS) FET’s using PLZT/STO/Si(100) structures[J]. IEEE Electron Device Lett, 1997,18:160.

[17] CHOI K J, SHIN W C, YANG J H, et al. Metal/ferroelectric/insulator/ semiconductor structure of Pt/SrBi2Ta2O9/YMnO3/Si using YMnO3as the buffer layer[J]. Appl Phys Lett, 1999,75:722.

[18] OKUYAMA M, NODA M, YAMASHITA K. A low-temperature preparation of ferroelectric SrxBi2+yTa2O9thin film and its application to metal-ferroelectric-insulator-semiconductor structure[J]. Mater Sci Semicond Process, 1999,2:239.

[19] CHOI H S, KIM E H, CHOI I H, et al. The effect of ZrO2buffer layer on electrical properties in Pt/SrBi2Ta2O9/ZrO2/Si ferroelectric gate oxide structure[J]. Thin Solid Films, 2001, 388:226.

[20] SZE C Y, LEE J Y M. Electrical characteristics of metal-ferroelectric (PbZrxTi1-xO3)-insulator (Ta2O5)-silicon structure for nonvolatile memory applications[J]. J Vac Sci Technol B, 2000,18:2848.

[21] KIJIMA T, FUJISAKI Y, ISHIWARA H.Fabrication and characterization of Pt/(Bi, La)4Ti3O12/Si3N4/Si metal ferroelectric insulator semiconductor structure for FET-type ferroelectric memory applications[J]. Jpn J Appl Phys, 2001,40: 2977.

[22] CHOI H S, LIM G S, LEE J H,et al.Improvement of electrical properties of ferroelectric gate oxide structure by using Al2O3thin films as buffer insulator[J]. Thin Solid Films, 2003, 444: 276.

[23] JUAN P C, LIN C L, SHIH W C, et al. Fabrication and characterization of metal-ferroelectric (PbZr0.6-Ti0.4O3)-insulator(La2O3)-semiconductor capacitors for nonvolatile 71 memory applications[J]. J App Phys, 2009,105:061625.

[24] PARK B E, ISHIWARA H. Electrical properties of LaAlO3/Si and Sr0.8Bi2.2Ta2O9/LaAlO3/Si structures[J]. Appl Phys Lett, 2001,79: 806.

[25] NODA M, KODAMA K, KITAI S,et al. Basic characteristics of metal-ferroelectric-insulator-semiconductor structure using a high-k PrOxinsulator layer[J].J Appl Phys, 2003,93:4137.

[26] BURR G W, KURDI B N, SCOTT J C, et al. Overview of candidate device technologies for storage-class memory[J]. IBM J Res Dev, 2008,52:449.

[27] SAKAI S, ILANGOVAN R. Metal-ferroelectric-insulator-semiconductor memory FET with long retention and high endurance[J]. IEEE Electron Device Lett, 2004,25:369.

[28] AIZAWA K, PARK B E, KAWASHIMA Y, et al.Impact of HfO2buffer layers on data retention characteristics of ferroelectric-gate field-effect transistors[J]. Appl Phys Lett, 2004,85:3199.

[29] TAKAHASHI M, SAKAI S.Self-aligned-gate metal/ferroelectric/insulator/semiconductor field-effect transistors with long memory retention[J].Jpn J Appl Phys, 2005,44: L800.

[30] TAKAHASHI K, AIZAWA K, PARK B E,et al. Thirty-day-long data retention in ferroelectric-gate field-effect transistors with HfO2buffer layers[J]. Jpn J Appl Phys, 2005,44:6218.

[31] BAE S H, LEE C H, CLAR R, et al. MOS characteristics of ultrathin CVD HfAlO gate dielectrics[J]. IEEE Electron Device Lett, 2003, 24: 556.

[32] LU X B, MARUYAMA K, ISHIWARA H. Metal-ferroelectric-insulator-Si devices using HfTaO buffer layers[J]. Semicond Sci Technol, 2008, 23: 045002.

[33] LU X B, ISHIWARA H. Fabrication and characterization of metal-ferroelectric-insulator-Si diodes and transistors with different HfSiON buffer layer thickness[J]. J Mater Res, 2008,23:2727.

[34] ZHU W J, TAMAGAWA T, GIBSON M, et al. Effect of Al inclusion in HfO2on the physical and electrical properties of the dielectrics[J]. IEEE Electron Device Lett, 2002, 23: 649.

[35] JUAN T P C, CHANG C Y, LEE J Y M. A new metal-ferroelectric (PbZr0.53Ti0.47O3)-insulator (Dy2O3)-semiconductor (MFIS) FET for nonvolatile memory applications[J]. IEEE Electron Device Lett, 2006, 27:217.

[36] THOMAS R, MELGAREJO R E, MURARI N M, et al. Metalorganic chemical vapor deposited DyScO3buffer layer in Pt/Bi3.25Nd0.75Ti3O12/ DyScO3/Si metal-ferroelectric-insulator-semiconductor Diodes[J]. Solid State Commun, 2009,149:2013.

[37] XIE D, HAN X, LI R, et al. Characteristics of Pt/BiFeO3/TiO2/Si capacitors with TiO2layer formed by liquid-delivery metal organic chemical vapor deposition[J]. Appl Phys Lett, 2010,97:172901.

[38] LU X B, ISHIWARA H, GU X, et al. Characteristics of metal-ferroelectric-insulator-semiconductor diodes composed of Pt electrodes and epitaxial Sr0.8Bi2.2-Ta2O9(001)/SrTiO3(100)/ Si (100) structures[J]. J Appl Phys, 2009,105:024111.

[39] TAKAHASHI M, WANG S Y, HORIUCHI T, et al. FeCMOS logic inverter circuits with nonvolatile-memory function[J]. IEICE Electron Express, 2009, 6:831-836.

[40] MIYAJI K, NODA S, HATANAKA T, et al. A 1.0 V power supply, 9.3 GB/s write speed, single-cell self-boost program scheme for high performance ferroelectric NAND flash SSD[J]. Solid State Electronics, 2011,58:34.

[41] ZHANG X Z, TAKAHASHI M, TANIGUCHI K, et al. 64 k bit ferroelectric-gate-transistor-integrated NAND flash memory with 7.5 V program and long data retention[J]. Jpn J Appl Phys, 2012,51: 04DD01.

[42] NABER R, ASADI K, BLOM P, et al. Organic nonvolatile memory devices based on ferroelectricity[J]. Adv Mater, 2010, 22:933.

[43] NABER R, TANASE C, BLOM P, et al. High-performance solution-processed polymer ferroelectric fi-eld effect transistors[J]. Nat Mater, 2005,4:243.

[44] NGUYEN C A, MHAISALKAR S G, MA J, et al. Enhanced organic ferroelectric field effect transistor characteristics with strained poly(vinylidene fluoride-trifluoroethylene) dielectric[J].Org Electron, 2008, 9: 1087.

[45] KANEKO Y, NISHITANI Y, UEDA M,et al. A 60 nm channel length ferroelectric-gate field-effect transistor capable of fast switching and multilevel programming[J]. Appl Phys Lett, 2011,99: 182902.

[46] HAI L V, TAKAHASHI M, SAKAI S. Fabrication and characterization of sub-0.6-μm ferroelectric-gate field-effect transistors[J]. Semicond Sci Technol, 2010,25:115013.

[47] KANEKO Y, TANAKA H, UEDA M, et al. A dual-channel ferroelectric-gate field-effect transistor enabling NAND-type memory characteristics[J]. IEEE Trans Electron Devices, 2011,58: 1311-1318.

[48] LI Y S, MA Y, ZHOU Y C. Polarization loss and leakage current reduction in Au/Bi3.15Nd0.85Ti3O12/Pt capacitors induced by electron radiation[J]. Appl Phys Lett, 2009,94:042903.

[49] JUNQUERA J, GHOSEZ P. Critical thickness for ferroelectricity in perovskite ultrathin films[J]. Nature, 2003,422:506.

[50] PANTEL D, GOETZE S, HESSE D,et al. Reversible electrical switching of spin polarization in multiferroic tunnel junctions[J]. Nat Mater, 2012,11: 289.

[51] TAKAHASHI K, AIZAWA K, ISHIWARA H. Optimum ferroelectric film thickness in metal-ferroelectric-insulator-semiconductor structures composed of Pt, (Bi, La)4Ti3O12, HfO2, and Si[J]. Jpn J Appl Phys, 2006,45:5098.

[52] SHIMADA Y, ARITA K, KATO Y,et al. A read-disturb-free ferroelectric gate FET memory[J]. Integr Ferroelectr, 2001,34: 1467.

Ferroelectric-GateFieldEffectTransistors:WorkingPrinciple,MaterialsDesignandRecentResearchProgress

LU Xubing*, LI Ming, LIU Junming

(South China Academy of Advanced Optoelectronics, South China Normal University,Guangzhou 510006,China)

A systematic introduction to the basic working principles of FeFET is given, which focus on the material design rules in the FeFET, the main ferroelectric materials and high-K buffer layer materials, and the electrical properties of their corresponding FeFET devices. Furthermore, the latest research progress on FeFET such as FeCMOS logic circuits, FeNAND flash memory circuits, and novel FeFET device structures based on oxide semiconductor and organic semiconductor will also be introduced. Finally the possible future research prospect on this field will be suggested.

2012-06-08

广东省高等学校人才引进专项资金项目

*通讯作者, luxubing@scnu.edu.cn

1000-5463(2012)03-0001-11

O472+.4, TN386.2

A

10.6054/j.jscnun.2012.06.001

Keywords: nonvolatile memory; ferroelectric-gate field effect transistor; flash memory; organic semiconductor; oxide semiconductor

【责任编辑 庄晓琼】