基于动态可重构的软硬件协同容错构架

2012-10-08张佳芳高志刚戴国骏

张佳芳,高志刚,戴国骏

(杭州电子科技大学计算机应用技术研究所,浙江杭州310018)

0 引言

现场可编程门阵列(Field Programmable Gate Arrays,FPGA)作为嵌入式开发平台,有着低功耗,高灵活性和可重复烧写等特性,使其在无线通信,航空航天,消费电子,工业控制等领域有着广泛的应用。然而,基于SRAM技术的FPGA对由辐射引起的单粒子翻转(Single Event Upsets,SEU)非常敏感,可导致其内存单元发生错误。根据Xilinx的设备可靠性报告[1],由于SEU的影响,Virtex4芯片的配置内存错误发生率为262 FIT/Mb,块RAM为474 FIT/Mb[2],Virtex2 pro芯片的配置内存错误发生率为437 FIT/Mb,块RAM为770 FIT/Mb。由于SEU引起的非永久性错误只需对产生错误的逻辑块进行重新配置即可消除,因此本文采用动态可重构技术,重新配置发生错误的硬件模块,修复硬件模块中的非永久性错误。在FPGA上运行系统的可靠性一直都受到很大关注,已经有很多方法被提出来加强FPGA中逻辑单元的健壮性,避免SEU引起的错误[3,4]。然而对于某些资源受限又有容错纠错需求的FPGA嵌入式系统,若使用硬件三模冗余进行容错将消耗大量的FPGA硬件资源,从而导致硬件资源的不足。本文提出一种基于动态可重构技术的软硬件协同容错纠错系统,采用两个硬件模块并行运行实时监测错误的发生,一个软件模块协助两个硬件模块,判决错误硬件模块实现系统容错,并采用动态可重构技术中的部分可重构技术,对由SEU引起的局部错误区域进行修复。整个系统用实时操作系统控制,提高对硬件错误的响应。

1 系统构架

从嵌入式系统模块化的角度出发,嵌入式系统可根据功能模块的不同,分成多个子系统模块,由各个子系统模块合作完成系统的设计目标。在各个子系统模块中,关键模块无疑是最需得到保护的,且当其发生错误后,进行纠错时不能有很大的系统中断延时,以避免系统运行崩溃。然而对于硬件资源受限的FPGA嵌入式系统,若使用硬件三模冗余实现对关键模块的保护,可能导致FPGA硬件资源不足的困境。本文采用两个关键硬件模块并行运行,调用软件模块协同硬件模块,进行检测纠错,相比三模冗余减少一个硬件模块的使用,从而减少1/3的关键模块硬件资源消耗,且不引起较大的中断延时。

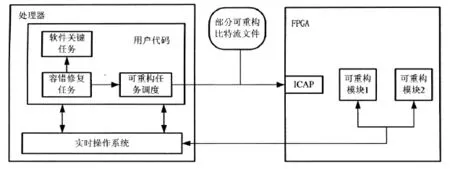

系统构架采用动态可重构技术中的部分可重构技术实现对关键模块的纠错,FPGA嵌入式系统中需保护的关键模块作为可重构模块。系统总体构架如图1所示,当嵌入式系统调用关键模块任务时,向两个可重构模块输入相同的数据,通过实时操作系统监控两个可重构模块所输出的数据是否相同以判断在可重构模块中是否有错误发生。当发生错误时,实时操作系统将收到可重构模块错误中断响应,并立即调用用户代码区的容错修复任务,对可重构模块进行检错纠错。容错修复任务控制整个容错修复流程,通过调用软件关键任务协同硬件可重构模块判决发生错误的可重构模块。在确认错误可重构模块后,容错修复任务调用可重构任务,重新烧写发生错误的可重构模块,修复由SEU引起的错误。

图1 系统总体构架

2 容错修复流程

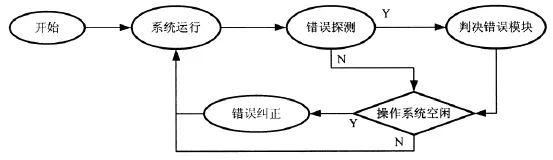

三模冗余是一种广泛应用的容错方案,但是所需硬件资源是保护模块的3倍,为节约硬件资源,本文采用一个软件关键模块替代硬件模块,协同两个硬件模判决错误的硬件模块。容错修复流程由运行在实时操作系统上的软件代码控制,能实时响应错误中断,及时修复错误区域。在这节中详细描述容错修复流程的实现,容错修复流程如图2所示。

图2 容错修复流程

容错流程描述:错误探测进程用于检测两个硬件模块输出数据是否相同,当出现不同时保存两份硬件模块输出数据,立即进入判决错误模块进程。判决错误模块进程调用软件关键任务模块,输入硬件模块发生错误时的输入数据,在得到软件关键模块数据输出后,通过比对3份数据,从而判决出哪个硬件模块发生错误。

错误纠正进程调用:在判决出发生错误的硬件模块后,仍有一个硬件模块能正确运行,嵌入式系统可采用该硬件模块继续正确运行,但缺失检错功能。因此为减少系统中断时间,可将错误纠正进程放置在操作系统空闲时进行。当操作系统进入空闲时,立即进入错误纠正进程,调用动态部分可重构任务,重新烧写因SEU导致错误的动态可重构区域,刷新配置逻辑块,纠正该错误区域,重新恢复系统检错功能。

3 硬件平台开发

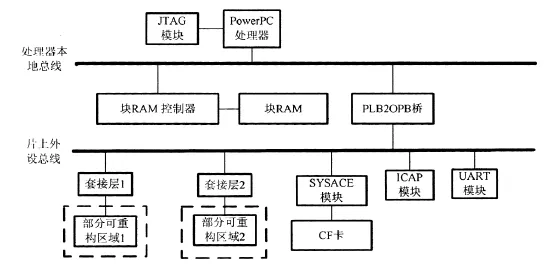

本文采用Xilinx的Virtex2 pro平台作为系统硬件搭建的平台。但是所提出的系统构架能够在其他具有动态部分可重构功能的FPGA上实现。根据所提出的系统构架,通过使用Xilinx的嵌入式开发套件中自带的IP核与根据不同任务自己开发的部分可重构任务IP核搭建硬件平,如图3所示。

图3 硬件平台

在硬件平台中采用PowerPC405作为处理器,运行实时操作系统,调度软硬件任务的运行。根据关键任务所需的功能自行设计部分可重构模块IP核,将其放置在部分可重构区域,因为使用两个硬件模块对比数据输出来检测关键模块是否出错,所以在图3中硬件平台有两个部分可重构区域。

两个部分可重构区域的数据同步,是进行关键模块错误检错的关键。在本文中采用套接层IP核,其功能是连接动态部分可重构区域与静态区域,控制两个部分可重构区域的数据输入和输出,确保两个硬件模块有相同的输入。

为实现动态部分可重构功能,将部分可重构比特流文件存储在CF卡中,当需要重新烧写部分可重构区域时,通过使用内部配置接入接口实现对指定可重构区域的重新烧写,以消除由SEU引起的错误。

4 实验

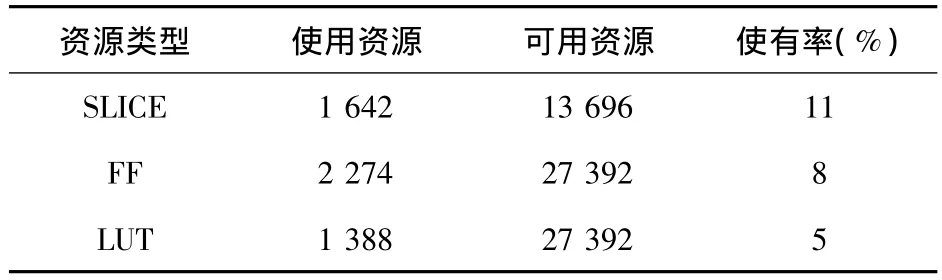

在实验中采用FIR带通滤波器作为嵌入式系统中需要保护的关键模块,μC/OS作为实时操作系统,应用所提出的系统构架在Virtex2 pro开发板上进行实验。在图3所提出的硬件平台上添加声音输入输出模块硬件模块,从该模块输入声音的采样数据通过带通数字滤波器再从该模块输出,实现数字滤波功能。FIR带通滤波器作为关键模块,需要硬件代码和软件代码都能实现该功能,因此使用Verilog语言设计FIR带通滤波器的硬件模块,使用C语言设计FIR带通滤波器的软件模块。Verilog代码进行综合后硬件资源消耗如表1所示,其中可用资源为Virtex2 pro芯片上可用的总资源。因所提出的体系构架中采用两个硬件模块,所以实际消耗的资源是表1中使用资源项的2倍。但相比三模冗余,可减少1份如表1所示的使用资源。

表1 可重构模块资源消耗

由于硬件模块出错的随机性,为了检验系统的运行性能,通过软件模拟的方式,触发容错修复系统的运行。实验中通过μC/OS操作系统,向可重构够区域1的可重构模块输入错误数据,当两个可重构模块输出数据不相等的时候,μC/OS操作系统收到一个错误中断请求,进入容错修复流程,运行FIR带通滤波器软件代码,通过两个硬件模块和软件任务输出的3份数据比对,确定可重构区域1发生错误,放弃可重构区域1的数据输出,等待μC/OS操作系统空闲时间。在μC/OS操作系统进入空闲时间时,立即运行可重构任务,对可重构区域1进行修复,恢复检错功能。实验表明系统构架的运行符合容错修复系统设计预期。

容错修复流程系统中断时间分析:在判决错误模块进程时,需要调用软件关键任务,并等待该软件任务输出数据以协助判决硬件模块。因此在这个进程中,产生的中断时间T1为软件任务的运行时间,T1的大小根据设计者设计的软件关键任务而定。错误纠正进程产生的中断时间T2为使用动态可重构技术重新烧写可重构区域的时间,中断延时与比特流文件大小呈线性正比关系[5]。但是在容错修复流程中,将错误纠正进程放置在操作系统空闲时再运行,因此在系统中实际产生的中断时间为T1,即运行软件关键任务所需时间。

通过调用μC/OS操作系统中的时间函数,测得实验中软件任务的运行时间为41ms,动态可重构时间为400ms,因为在容错修复流程中设定在系统空闲时才使用动态可重构技术修复硬件错误,所有系统实际中断的时间为41ms。相比硬件三模冗余,以较小的系统中断时间为代价,节约1/3受保护关键模块资源消耗。

5 结束语

随着FPGA的广泛应用,对基于FPGA的嵌入式系统的安全性也越来越受到重视。本文通过软硬件协同合作方式实现容错,使用动态部分可重构技术消除由SEU引起的错误,避免重新烧写整个系统来解决错误,节约纠正错误的时间,提高整个系统的可靠性与实时性。

[1]Xilinx Inc.Device Reliablity Report[EB/OL].http://www.xilinx.com/support/documentation/user_guides/ug116.pdf,2010-08-10.

[2]Austin Lesea.Continuing Experiments of Atmospheric Neutron Effects on Deep Submicron Integrated Circuits[EB/OL].http://www.xilinx.com/support/documentation/white_papers/wp286.pdf,2009 -05 -22.

[3]Brian Pratt,Michael Caffrey,Paul Graham,etal.Improving FPGA Design Robustness with Partial TMR[J].Reliability Physics Symposium Proceedings,2006,44(1):226 -232.

[4]Kastensmidt F Lima,Sterpone L,Carro L,etal.On the Optimal Design of Triple Modular Redundancy Logic for SRAM -based FPGAs[J].Design,Automation and Test in Europe,2005,2(1):1 290 -1 295.

[5]Xilinx Inc.Partial Reconfiguration User Guide[EB/OL].http://www.xilinx.com/support/documentation/sw_manuals/xilinx12_3/ug702.pdf,2010 -10 -05.