DAB+音频解码器中TNS模块优化设计及硬件实现*

2012-09-19王国裕

陈 俊,王国裕,龚 敏

(四川大学物理科学与技术学院微电子技术四川省重点实验室,成都 610064)

1 引言

相较于传统的模拟广播,数字音频广播(DAB)具有音质好、频谱利用率高、抗干扰能力强等特点,DAB的普及已经成为一种趋势。DAB标准颁布后,其音频编解码方案一直采用MPEG Audio Layer II,出于进一步提高数据压缩率、提高频谱资源利用率的目的,国际DAB组织在2007年将压缩比高的MPEG-4 HE-AAC v2引入了DAB音频标准,称为DAB+。

MPEG-2/4 AAC作为新一代的音频编解码标准,以其高压缩比、重建音频质量好等优点广泛应用于移动通讯、数字广播等数字多媒体领域。作为一种感知音频编解码方案,编码过程中在频域产生的瞬时量化噪声,在解码过程中会在时域变换块内均匀扩散。当一个变换块包含瞬变信号时,量化噪声在时域的扩散尤为突出,会超过人耳听觉心理声学模型中的时域掩蔽阈区间[2],造成人耳能够听到的噪声即预回声现象,预回声是对音质的一种严重伤害。为了避免预回声现象,在编解码过程中必须充分考虑量化噪声的时域特性,尽可能的将其置于语音信号时域掩蔽阈区间之内。增加瞬态信号编码位元、自适应窗切换、增益控制等技术被广泛的应用于各种感知音频编解码方案中,以消除预回声现象[2,3],但这些技术在编码效率、音频重建质量等方面都难以达到最优化。而时域噪声整形(TNS)技术只需在标准编解码器中加入一个处理模块,通过对频域数据进行线性预测编解码,控制量化噪声在时域的分布,从而有效地抑制预回声现象,编码效率、音频重建质量都能达到最优化。

TNS作为AAC音频编解码方案的一个重要工具,能够显著提高解码音频质量,特别是一些变化剧烈的语音信号。针对DAB接收机中DSP软件AAC+解码器功耗大的问题,文献[1]给出了低功耗的AAC LC解码器的ASIC设计方案,本文在此基础上以极低的硬件资源实现了TNS全硬件解码。AAC解码器中TNS的实现多采用软硬件协同的方式[5,6],而本文将讨论TNS原理、算法以及解码端全硬件实现、验证方案。

2 时域噪声整形原理

TNS是通过对频域参数进行开环线性预测编解码来控制量化噪声的时域分布,使得量化噪声能跟随原始语音信号的频谱包络变化,并将其置于时域掩蔽区间之内,使人耳感觉不到噪声的存在,从而消除预回声现象。其原理主要基于以下两种思想:

(1)频谱包络与时域包络的时/频对偶性:频域变化剧烈的信号,可对其时域信号进行预测编码;同理,时域变化剧烈的信号,可对其频谱信号进行预测编码;

(2)利用频域开环线性预测编码(LPC)进行时域量化噪声整形,使解码端的量化噪声自适应于原始语音信号[2,3]。下面给出利用预测编解码整形量化噪声的原理。

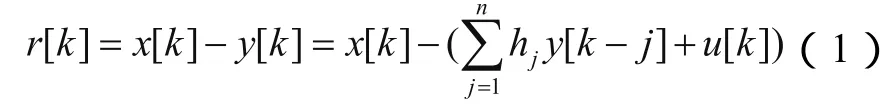

图1给出了TNS利用开环线性预测整形量化噪声的原理图,x[k]为编码端输入频谱值,y[k]为解码端输出频谱值,定义重建误差为r[k],h为线性预测参数。

定义d[k]为频谱预测残差,q[k]为量化误差,则:

由(4)式可看出,量化噪声在Z域被传输函数为H[Z]的反向滤波器所整形,使其自适应于原始输入信号包络[3],从而将量化噪声置于语音信号时域掩蔽区间之内。

图1 预测编解码整形量化噪声原理图

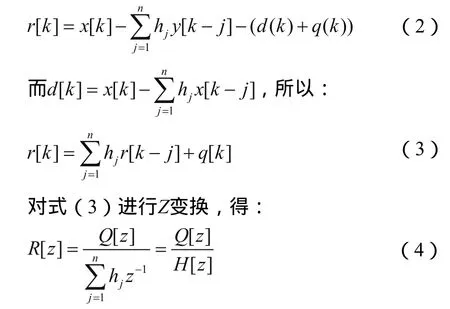

在编码端,分析滤波器组之后对频谱值进行线性预测编码,得到预测残差信号以及边界控制信息,如:滤波器级数、处理频谱范围等。在解码端,根据相应控制信息对预测残差进行TNS反向(全极点)滤波,滤波器类型为IIR,其输出方程及传输函数如式(5)和式(6)所示。其中,lpc为滤波器系数,k为滤波器级数,均由编码端决定。

3 TNS解码优化及其硬件实现

针对TNS解码算法以及AAC LC核心解码器整体硬件结构的特点[1],为实现合理利用硬件资源、降低复杂度、提高解码效率、保证系统低功耗的目的,在TNS解码硬件设计中主要基于以下方法完成设计:

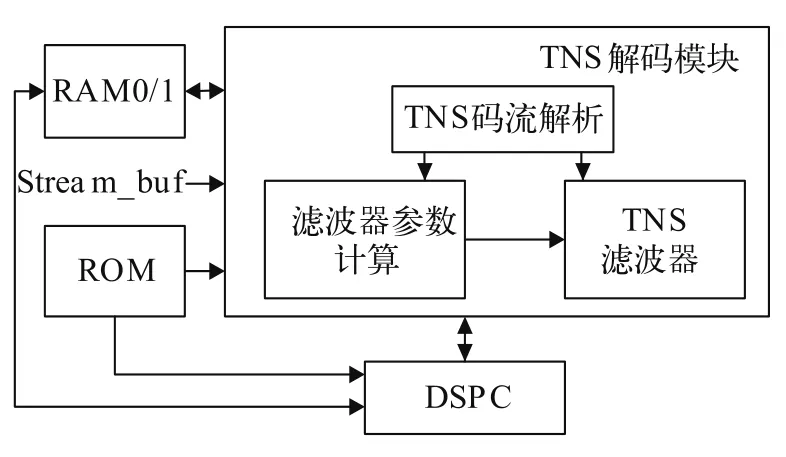

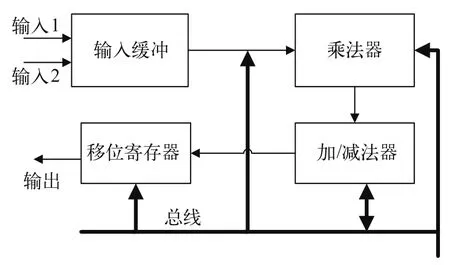

(1)为提高硬件利用率,减小电路规模,设计如图2所示的TNS解码硬件模块整体框架。TNS解码模块与 HE-AAC v2核心解码器其他模块一起共用两个大小为4096×18bits的RAM、大小为9405×18bits的ROM以及可综合的专用DSP模块DSPC。RAM作为各模块间数据交换的中枢,能有效避免复杂的连线,RAM0与RAM1分别用于存储左右声道频谱值以及解码过程中一些中间参数。ROM存放解码过程中所有需要调用的表格以及常数。DSPC是根据音频解码器特点而专门设计的一个可综合的DSP引擎,采用流水线结构,包括输入缓冲单元、乘法器、加/减运算单元以及移位寄存器,总线宽度为24bit,能在一个时钟周期内同时完成乘法、加/减以及移位操作,大大提高了运算速度,同时24bit的数据宽度也保障了运算精度,功能由存储的ROM中的运算指令所配置,其结构图如图3。

图2 TNS解码模块整体框图

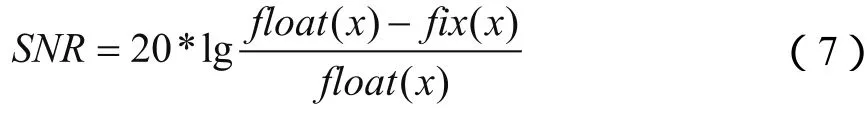

(2)由于在TNS解码模块中所有运算数据均为浮点数,为简化系统复杂度、节省硬件开销,同时保证运算精度,在硬件设计前用Matlab进行了浮点、定点模拟并计算出采用不同精度的信噪比,设定点解码结果为fix(x),浮点解码结果为float(x),系统信噪比SNR计算如式(7)所示,我们将频谱值、滤波器参数等数据都转换为宽度为18bit的定点数,其系统信噪比可达98dB以上,完全满足要求。

图3 DSPC结构图

(3)TNS解码模块包含以下三个部分:TNS码流解析、滤波器参数计算以及TNS反向(全极点)滤波器。码流解析模块从传输码流Stream_buf中解出TNS解码相应参数,包括:滤波器级数、待处理频段范围、反射系数等,并将其存入RAM0/1中。滤波器参数计算主要包括量化参数的反量化以及lpc参数的计算。反量化涉及正弦以及移位除法运算,在硬件设计中采取查表的方法实现,所有反量化结果仅占用32个ROM地址,相关参数组合作为ROM地址偏移量。

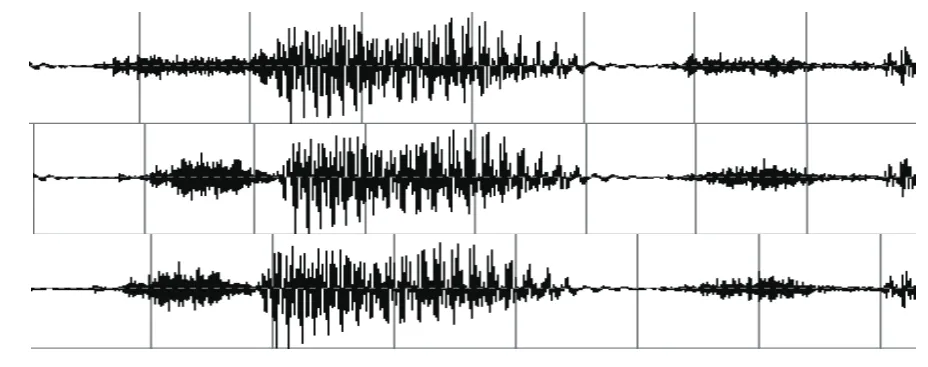

(4)在lpc参数计算过程中,会出现绝对值大于1的溢出情况,解码结果会出现严重的失真。我们近似地将整个反量化表右移1位,可保证所有计算过程不会出现溢出情况,如图4所示的实验结果表明,这种近似处理与标准算法解码结果基本一致,且避免了由于溢出所造成的噪音情况。

(5)在滤波器参数计算以及TNS反向滤波模块中,主要涉及乘加运算,结合DSPC的特点,合理设计运算指令,计算所需参数直接从RAM或ROM中送至DSPC的输入缓冲模块。TNS反向滤波器(见式(5))完成一个频谱值的运算仅需order+6(order为滤波器级数)个时钟周期,所有运算均采用同址运算,DSPC输出结果覆盖原始RAM地址的频谱值。对于AAC LC,TNS滤波器级数0<order≤12,针对不同级数分别设计TNS滤波器显然是不现实的,设计中我们采用状态机的方式,能够根据输入控制信息,完成所有级数的TNS滤波处理。

经FPGA综合,该TNS解码硬件模块,仅占用873个逻辑单元以及少许的存储单元,系统时钟达到16.384MHz,具有低硬件资源、高解码效率等特点。选取TNS作用效果明显的测试矢量(单声道、采样率24k、比特率40kbps),进行了硬件仿真结果与软件解码结果对比。如图4所示,该硬件解码结果(下)与采用标准算法的软件解码结果(中)差别细微,主观音质无差异,相对于不进行TNS解码处理的解码结果(上)量化噪声的均匀分布,其量化噪声自适应于原始语音信号,都能够很好地抑制预回声现象。

图4 标准软件算法与硬件解码结果对比

4 FPGA验证与测试

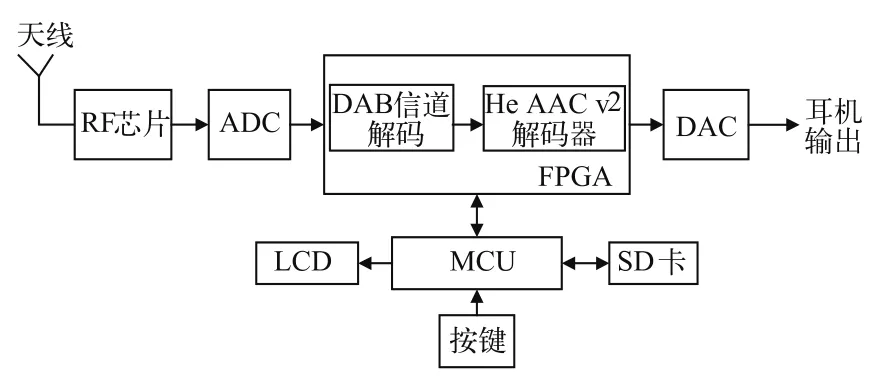

该TNS解码模块作为DAB+基带芯片信源解码的一部分,选取TNS作用效果明显的DAB+节目作为测试矢量进行FPGA验证与测试,本文采用用两套验证测试方案:

(1)测试矢量来自SD卡,经MCU送入音频解码器,对音频解码模块进行单独测试;

(2)基于DAB接收机整机方案,利用实验室自建的DAB发射系统发射DAB+节目,接收DAB信号进行实时解码。

FPGA验证测试方案如图5所示,采用Altera EP3C120 FPGA开发板以及片外MCU、RF芯片、SD卡等组建验证测试系统,并设置按键作为TNS解码模块的开关信号。实验结果表明,TNS对于一些变化剧烈的语音信号音质提高发挥了很大的作用,硬件解码音质令人满意。

图5 FPGA验证测试方案

5 结论

本文所设计的TNS硬件解码模块在DAB+基带芯片信源解码器中成功实现,充分利用了已有硬件资源,实现充分共享,在保证了其提高音质功能的同时,又从硬件资源、解码效率等方面实现了硬件系统的低功耗。较之文献[5,6]所采用的软硬件协同方式实现TNS解码,本设计不但采用全硬件方式实现,且所占用硬件资源更少;文献[4]所提出的AAC解码器纯ASIC设计将TNS解码模块作为HSSP(硬件共享处理器)的一部分,与M/S、IS等四个模块实现充分共享乘法器、加法器等硬件资源,而本文所提出的整体结构与HE-AAC v2所有功能模块共享存储单元、DSPC等硬件资源,整体上更具优越性,进一步提高了硬件资源利用率,由于所有解码运算均共享DSPC,从而大大节省了乘法、加法器资源。

[1]陆明莹,张丽丽,王国裕,等.低功耗、便携式数字音频广播接收机中AAC LC解码器的设计优化[J].电子信息学报,2011,33(5):1229-1232.

[2]Ted Painter,Andreas Spanias,etc.Perceptual Coding of Digital Audio[J].Procedings of the IEEE,2000,88(4): 451-515.

[3]Chi-MinLiu,Han-WenHsu,etc.Compression Artifacts in Perceptual Audio Coding[J].IEEE Transactions on Audio,2008,16:681-695.

[4]Tsung-Han Tsai,Chun-Nan Liu.Low-Power System Design for MPEG-2/4 AAC Audio Decoder Using Pure ASIC Approach[J].IEEE Transactions on Circuits and Systems,2009,56(1):144-155.

[5]赵喜林,林涛.AAC音频解码器中TNS模块的设计及其ASIC实现[J].微电子学与计算机, 2006.

[6]徐生俊,周玉洁.TNS解码在AAC解码SOC系统中的实现与优化[J].信息技术,2005.