核电多样性驱动系统硬件设计

2012-07-26杨烨

杨 烨

(上海自动化仪表股份有限公司技术中心,上海 200072)

0 引言

在AP1000核电站控制系统中,根据不同的核安全分级,采用安全级和非安全级两个不同的平台实现安全控制功能。安全级平台即保护和安全检测系统(protection and safety monitoring system,PMS),实现反应堆保护系统的功能;非安全级平台即电厂控制系统(plant control system,PLS),实现核岛/常规岛/电厂配套设施 (balance of plant,BoP)大多数的控制功能。将这些可能受到共因故障影响的安全功能组合在一起,就组成了多样性驱动系统 (diverse actuation system,DAS)。DAS是独立于这两个平台外的一个孤立系统。当保护和安全检测系统出现概率极低的共因故障时,DAS系统用来触发反应堆紧急停堆和汽轮机停机,降低堆芯熔化和安全壳超压的概率。

本文介绍了上海自动化仪表股份有限公司技术中心研发的DAS系统主要模块的硬件设计。在开发过程中,选用现场可编程门阵列(field programmable gate array,FPGA)实现从模拟信号采集到继电器输出等一系列功能,避免了软件V&V认证,大大加快了开发进度。由FPGA硬件搭建的系统具有响应速度快、采样精度高和抗干扰能力强等优点,是当今国际上功能安全系统设计的主流方案。

1 产品工作原理及系统概述

由于DAS系统是保护和安全检测系统PMS和电厂控制系统PLS的备用性系统,因此它采用不同于PMS和PLS软硬件结构,这也是AP1000核电站控制系统在提高安全性措施方面除了非能动设计以外的一项重要措施[1]。

保护和安全检测系统(PMS)采用Emerson Ovation系统,基于英特尔X86/Pentium硬件平台,操作系统选用 VxWorks,C语言编程,Emerson Control Builder software软件平台。控制系统(PLS)采用ABB AC160系统,摩托罗拉68系列硬件平台,VRTX开发系统,AMPL语言,ABB Function Chart Builder software软件平台。而DAS系统是一个完全基于硬件的系统,没有软件控制,主芯片采用 FPGA[2],硬件描述语言选用VHDL。虽然多样性驱动系统执行的是安全功能,但是它本身仍属于非安全级。

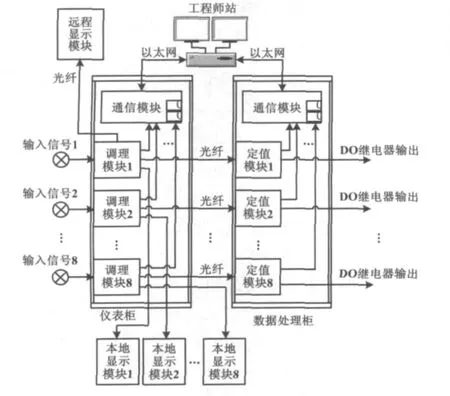

一个典型的DAS系统包括仪表柜中的8块调理模块和对应的通信模块、数据处理柜中的8块定值模块和对应的通信模块、若干本地显示模块和远程显示模块以及工程师站。DAS系统结构图如图1所示。

图1 DAS系统结构图Fig.1 Structure of DAS

DAS系统采用单通道输入,共包含16个模拟信号输入。输入信号如表1所示。

表1 DAS系统输入信号Tab.1 Input signals of DAS

仪表柜部分主要负责输入信号处理、显示和通信等功能。其中,调理模块接收探测器信号(包括4~20 mA电流、1~5 V电压、TC、RTD信号);对输入信号进行必要的隔离、滤波和A/D转换等处理,转换成工程量值后,既可通过RS-485串口分别传送至本地显示模块和通信模块,又可通过光纤传送至定值模块和远程显示模块。

数据处理柜主要由定值模块和通信模块组成。定值模块分别接收来自调理模块和通信模块的信号,并将这两个信号进行比较。比较结果经过必要的延时和逻辑处理后,驱动专设安全设施(engineered safety features,ESF),缓解事故工况。同时,定值以及定值状态等信息也被送到通信模块中,经由适当的隔离、调理等处理后,通过通信口送到工程师站。通信模块与定值模块或者调理模块之间通过RS-485串口实现点对点连接,与工程师站之间通过以太网相连接。

工程师站主要负责DAS系统的组态和监控两大功能:配置调整定值模块的比较值并下发到相应的通信卡,接收调理模块和定值模块上传的数据,监控定值状态。

2 各模块概述

2.1 调理模块

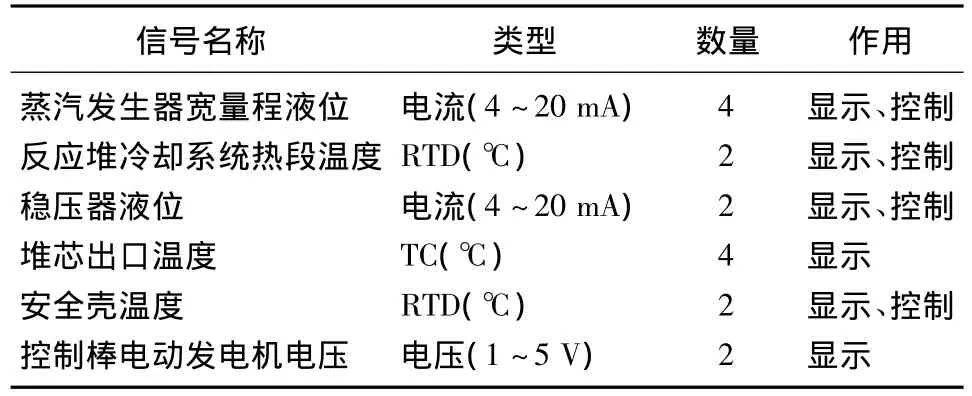

调理模块的主要功能是将输入的模拟信号转换为数字信号并发送到其他模块,硬件设计中采用的模数转换芯片是ADI公司的AD7792。AD7792为∑-Δ结构[3],采用SPI串口通信方式,考虑到模拟信号输入精度和稳定性,采样有效位数选择16位,采样周期为20 ms。调理模块上的FPGA是Altera公司 CycloneII系列的EP2C5,FBGA256封装。根据输入的模拟信号类型的不同,调理模块可以分为三大类:电流/电压型调理模块、RTD型调理模块和TC型调理模块。电流/电压型调理模块可以接收4~20 mA的电流信号和1~5 V的电压信号,采样输入精度达到量程范围的0.1%。RTD型调理模块可以接收Pt100和Cu50的三线制热电阻信号,采样输入精度分别为0.1%和0.3%。TC型调理模块可以接收T、K、E、N型热电偶信号,带冷端补偿功能和断路检测功能,采样输入精度分别为0.2%和0.3%。调理模块基本工作原理框图如图2所示。

图2 调理模块原理图Fig.2 Principle of the conditioning module

图2中,各类型的模拟信号进入调理模块,经预处理和AD7792芯片,转换出32位原始码值,再通过SPI串行通信协议,进入FPGA。在FPGA中,原始码值首先通过码值转换模块转换为补码形式,同时将Flash中存储的标定系数k、b和量程转换系数A、B读出,通过两次kx+b的线性处理,把补码形式的原始码值转换成2字节整数位和1字节小数点位的定点数工程量值信号。这3个字节的数据再经UART发送模块输出:一路通过光电转换模块,以光纤为媒介送往定值模块,称之为安全通道;另一路通过RS-485驱动芯片,以双绞线为媒介送往本地显示模块和通信模块[4],称之为非安全通道。在调试模式下,调理模块可以通过RS-485接收通信模块发出的标定系数和量程转换系数,并写入Flash。当调理模块断电后再次上电启动时,可以直接从Flash中读出这些参数并进行运算。

SPI收发模块采用状态机设计[5]。FPGA作为主端,AD7792作为从端,即FPGA向AD7792输出数据线Dout、时钟线 sclk和片选线 ssel,AD7792向 FPGA输入数据线Din。SPI收发模块主要包括波特率发生器(baud.v)、发送模块(transfer.v)和接收模块(receive.v)三部分。

波特率发生器通过计数器,将主时钟24 MHz分频为12 MHz,作为发送模块和接收模块的时钟。如果需要降低SPI串口通信的波特率,只需要修改分频参数即可;如果需要提高SPI串口通信的波特率,可以利用FPGA内部的PLL资源提高时钟频率。在发送模块和接收模块内部还有1个16位的计数器,用于限定输出1位数据的时间长度。因此,输出或者输入的串行数据每一位的宽度为 1.33 μs,波特率为750 kbit/s[6]。

发送模块本质上是一个并转串的移位寄存器,初始化完成后FPGA向AD7792传送的SPI信号线Dout、sclk和ssel都为高电平。当开始发送数据时,第1个时钟周期先将ssel拉低;第2到第9个时钟周期依次将待输出的8位数据线输出到Dout,同时输出8个周期的sclk;第10个时钟周期将ssel拉高,结束一帧数据的发送。

接收模块和发送模块的原理基本类似,只不过数据方向是从Din到内部数据输入缓存区。此外,开始接收每一位的数据之前必须先预留半个时钟周期的时间,使得读取数据的时间在数据位的中间,保证数据的稳定性[7]。

至于UART串行通信收发模块的设计,由于设计方案比较成熟,在开发过程中参考了一些现有的IP core,仅增加了帧数据发送功能和10 B输出缓存,且UART收发模块和SPI收发模块在设计原理上基本一致,因此,该设计就不做详细介绍了。FPGA内其余功能模块,如码值转换、线性处理、Flash读写等因为设计较为简单,本文中也不做详细介绍。

2.2 定值模块

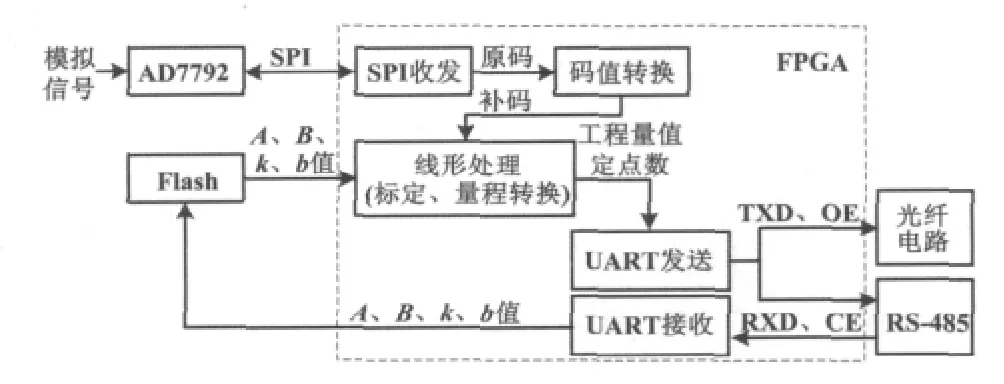

定值模块的主要功能是通过光纤或者RS-485接收从调理模块来的数字信号,并与工程师站下发的定值信号进行带死区比较处理,通过固态继电器输出。其基本工作原理框图如图3所示。

图3 定值模块原理图Fig.3 Principle diagram of set-point module

调理模块处理后的3 B定点数工程量值信号被送入定值模块,经光纤接收电路后进入FPGA,由UART接收模块转换成无小数点的16位工程量PV值。同时,定值模块从RS-485串口接收由工程师站通过通信模块发送的设定参数,包括设定值SP和ΔSP、延时参数、旁路参数等。工程师站配置的设定值、延时参数、旁路参数等数据全部写入Flash。当定值模块上电后,可以从Flash中读出这些参数,并进行比较和配置,即使没有工程师站,也能使定值模块正常运行。设定值以及各种参数通过UART发送模块和RS-485回送到通信模块供工程师站监视用。PV值和SP值可以通过定值卡面板上的选通开关显示具体数值。

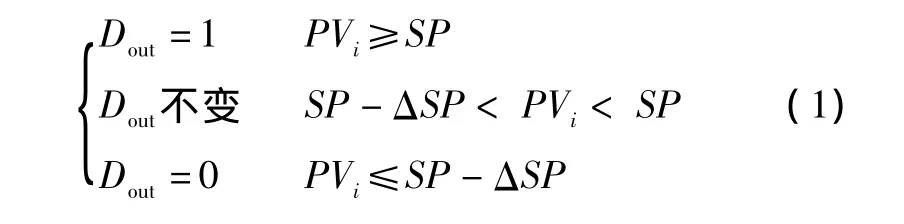

定值模块中的数据处理是将PV值与SP和ΔSP进行带死区定值比较,得到Dout信号,并经过必要的延时和旁路选通逻辑后,输出最终的DO信号给继电器。由于定制模块接收到的PV值有电流、电压和温度3种工程量类型,所以SP和ΔSP也定义为相应的类型,并且小数点位数相同,以便于比较。定值比较公式如下,其中,PVi为不同时刻采集到的PV值。

将上述公式反映在坐标图中,则有:①在t0~t1时间段内,PVi≤SP-ΔSP,输出的 Dout为0(即继电器输出没有动作);②在t1~t2时间段内,SP-ΔSP<PVi<SP,输出的Dout保持不变,仍为0;③在t2~t3时间段内,PVi≥SP,输出的 Dout为1,即继电器输出动作;④在t3~t4时间段内,SP - ΔSP <PVi<SP,输出的 Dout为保持,即输出为1;⑤在 t4之后,PVi≤SP - ΔSP,输出的Dout为0。定值比较曲线如图4所示。

图4 定值比较曲线图Fig.4 Curves of set-point comparison

因为调理卡的种类有电流、电压、TC、RTD四种,所以图中所示定值卡采集到的PV工程量值的单位相应有毫安、伏和摄氏度。

在定值模块的FPGA设计过程中,主要设计了比较、延时和旁路这3部分。由于是定点数,因此比较部分设计相对而言比较简单,通过直接比较整数部分即可得到Dout结果。延时参数共5 bits,代表从0~31 s的延时长度,而板上主时钟为24 MHz,所以开发时在FPGA内做了一个较大的计数器,根据延时长度,将Dout延时输出。如果在延时时间内Dout发生变化,继电器输出不会产生变化。

在本设计中,旁路参数包括旁路选择开关和旁路数据输出,共2 bits,开发过程中设计了一个二选一的选通器,根据旁路选择开关的状态来选择输出Dout还是旁路数据。

2.3 通信模块

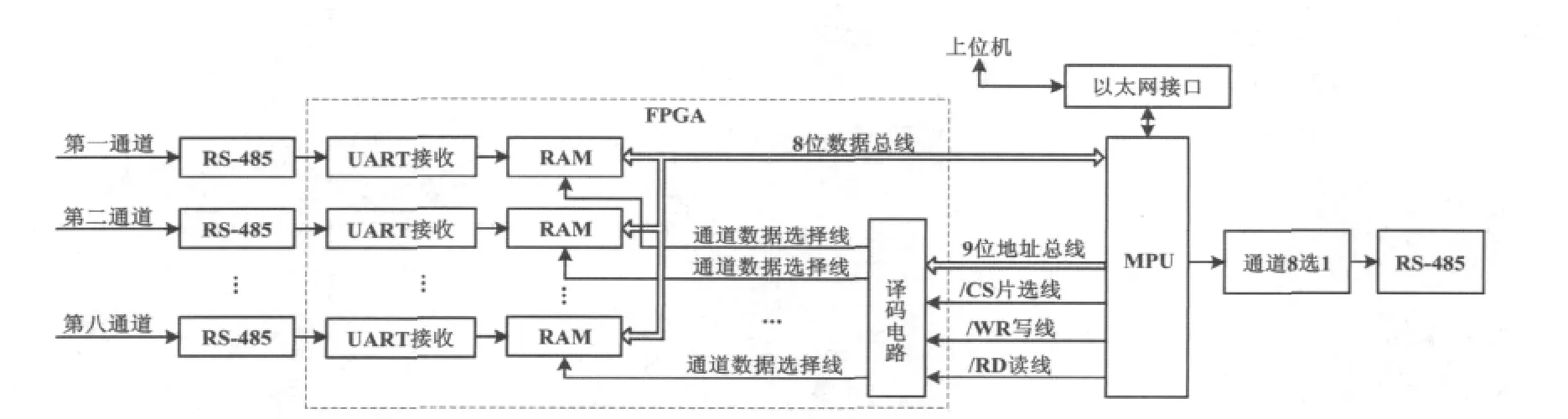

通信模块的主要功能是与调理模块、定值模块和工程师站进行通信转发,其基本工作原理框图如图5所示。

图5 通信模块原理图Fig.5 Principle of communication module

通信处理器模块用来接收定值模块或者调理模块发送的定值参数或者工程量值等信息,通过以太网传送至工程师站[8],还可以接收工程师站下发的指令,将定值写入相应的定值模块,或者将标定系数写入调理模块。

通信模块的FPGA内部设计了1个8通道、每通道10 B的RAM区[9],将UART接收模块收到的数据(包括从调理模块接收到的2 B模拟信号工程量值和1 B小数点位;从定值模块回读的SP值和ΔSP值,以及一些延时、旁路选择等参数)放入RAM区,同时设计了对应8通道的8位状态标志,MPU通过判断状态标志来决定是否读取该通道数据。

在测试过程中发现,长时间读取RAM过程中会出现读数据出错的现象。为解决该问题,对状态标志的设计作了改进,即当UART异步串口有新数据更新时,拉高可读状态标志,直到MPU读取过一次数据后,可读状态标志自动拉低;如果直到下一次UART串口数据更新时MPU还没有读取过数据,那么在下一次UART串口数据开始更新时,主动将可读状态标志拉低,更新完成后再拉高。这样就避免了在一次UART接收周期内MPU读不到数据或者连读两次的情况。改进后经长时间测试表明,MPU能正常读取各通道数据。

2.4 显示模块

显示模块将调理模块输出的工程量值在本地或者远程端显示出来,显示模块可通过跳线切换本地显示模式或者远程显示模式。当跳线为本地显示模式时,显示模块接收RS-485的串口通信信号;当跳线为远程显示模式时,显示模块接收光纤模块的信号。进入FPGA后的串口数据通过UART接收模块实现串并转换,并通过码值转换电路,将3 B的定点数转换成BCD码,输出到5个8段数码管显示[10]。

受数码管数量的限制,目前显示模块所能显示的范围为-19999~+19999。为确保数据的稳定性,电流电压信号保留2位小数,热电阻信号保留1位小数,热电偶信号没有小数点。

显示模块硬件原理框图如图6所示。

图6 显示模块硬件原理框图Fig.6 Principle of the hardware of display module

FPGA内的码值转换模块设计思路如下:首先判断符号位,正数不做处理,负数则将最高位的“-”点亮;然后处理数据位,将定点数的2 B整数部分除以10,余数就是个位所应显示的数字,将商再除以10,得到的余数就是十位所应显示的数字,依此类推,直到万位;最后判断小数点字节,应该点亮哪一位的小数点,如果最高位是0,则根据小数点位判断是否应该舍去0。

3 结束语

核电DAS系统位于核电站控制系统的最后一级,起到保护系统的备用系统作用,因此其设计的可靠性要求非常高。为提升安全等级,DAS系统在安全通道设计方案上采用纯硬件构架,选用FPGA代替CPU。

DAS系统主要包括调理模块、定值模块、通信模块和显示模块,模块之间通过光纤或者RS-485串行总线相连。同时,在FPGA设计过程中自主开发了SPI串口通信模块、原补码值转换模块、kx+b线形转换模块、Flash读写模块、UART串口收发模块、定值比较模块、BCD码转换模块和8通道×80 bits RAM模块等。该系统在运行时无需人工干预,可实现实时监控和自动输出驱动信号等功能。

2010年6月,该系统通过客户方验收,交付使用至今,工作情况良好。今后将在此基础上进一步改进DAS系统功能,提高系统可靠性和抗震性能,为核电控制系统的国产化做出新的贡献。

[1]李蔚,吴帆,王峰.AP1000全数字化仪控系统安全分析[J].电力安全技术,2006,8(6):45 -46.

[2]张淑慧,任永忠.AP1000核电厂仪控系统简介[J].自动化仪表,2010,31(10):48 -51.

[3]洪志良.模拟集成电路分析与设计[M].北京:科学出版社,2005:290-291.

[4]赵新民,王祁.智能仪器设计基础[M].黑龙江:哈尔滨工业大学出版社,2001:106-108.

[5]薛宏熙,刘素洁,刘宝琴,等.MACH可编程逻辑器件及其开发工具[M].2版.北京:清华大学出版社,1998:257-264.

[6]张友德,赵志英,涂时亮.单片微型机原理、应用与实验[M].上海:复旦大学出版社,2001:134-135.

[7]徐欣,于红旗,易凡,等.基于FPGA的嵌入式系统设计[M].北京:机械工业出版社,2005:519-520.

[8]费敏锐,郎文鹏.开放型工业控制技术及系统[M].上海:上海大学出版社,2000:144-145.

[9]冼进,戴仙金,潘懿萱.Verilog HDL数字控制系统设计实例[M].北京:中国水利水电出版社,2007:47-48.

[10]孙涵芳,徐爱卿.单片机的原理与应用[M].北京:北京航空学院出版社,1988:214-215.