基于System Generator的QPSK 数字调制器设计

2012-07-20薛青娜

薛青娜

(西安铁路职业技术学院,西安 710014)

1 引言

载波同步是实现QPSK 调制系统相干接收的关键技术[1],接收机必须重新产生一个与载波同频同相的本地载波,而锁相环技术便是实现这一要求的常用技术。本文采用XILINX System Generator for DSP 进行系统建模,System Generator是XILINX 公司开发的基于Simulink的建模软件,可以看作simulink的工具包。通过System Generator 可以将设计的模型直接生成位流文件,大大简化设计流程,能够让设计者把更多的精力投入系统的设计[2]。下面首先介绍锁相环的基本知识,然后探讨在System Generator 中实现数字锁相环技术,最后仿真验证锁相环的性能。

2 利用锁相环恢复载波的原理

2.1 锁相环基本知识

锁相环可以看作是一个跟踪伺服系统,通过反馈可以动态地调制输出信号,使输出信号与输入信号在频率和相位上保持一致。在锁相环锁定状态下,振荡器输出信号和参考信号之间的相位差为零,如果因某种原因产生相位误差,一种控制机理便作用在振荡器上,调制相位误差使其再次减小到零[3]。

锁相环通常有三个部分组成:鉴相器、环路滤波器和受控振荡器。鉴相器是一种特殊电路,它的输出信号和两个输入信号的相位差成比例。环路滤波器实际上是一个低通滤波器,它能够滤除鉴相器输出信号中不需要的高频分量,保留其低频分量,用来作为压控振荡器的控制信号。受控振荡器是一个晶体振荡器,用来产生与发射端载波同频同相的本地载波信号。

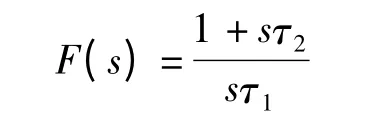

在锁定状态下,锁相环可以看作一个线性控制系统,鉴相器的数学模型可以看作一个增益为Kd的零阶模块[4]。而压控振荡器的数学模型可以等效为一个积分器,积分器的增益为K0。环路滤波器采用有源比例积分滤波器,其传输函数为:

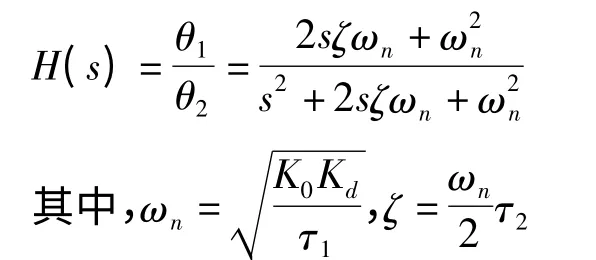

计算可得相位传输函数为:

θ1为接收信号的相位,θ2为产生本地载波的相位,ωn为自由振荡频率,ζ为阻尼因子。

锁相环通常分为模拟锁相环和数字锁相环,由于现在数字电路的应用越来越广泛,故本文采用数字模块对锁相环建模,需要将复频域的传输函数转换成Z 域的传输函数。

2.2 数字锁相环的实现

下面采用costas 环实现载波同步,costas 环是锁相环的一种,推广的cotsas 环的鉴相器输出波形为ε=sgn[I]Q-sgn[Q]I,其中符号函数代表限幅器,它的作用是使输出信号与调制信号的电平无关[4]。当环路的相位误差较小或者信噪比高的时候,经过减法器之后环路的误差信号为正弦型鉴相特性。

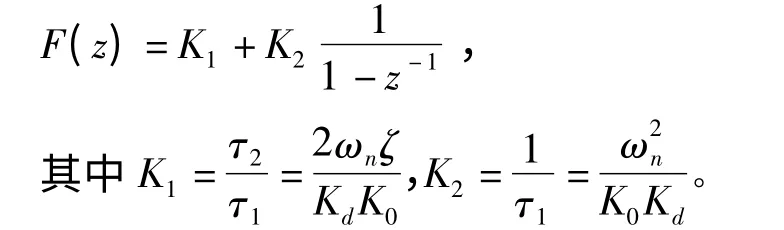

将环路滤波器的传递函数变换到Z 域得到[5]:

二阶锁相环是一个低通滤波器,频谱在0 到ωn之间保持平坦,因此在此范围内,二阶锁相环能够保持相位锁定状态。阻尼因子对锁相环的动态特性有很大影响,实际系统中大都以获取平坦的频率传输函数为目标,当ζ=0.707时,取得最佳平坦特性。综上,本实验中采用ζ=0.707。

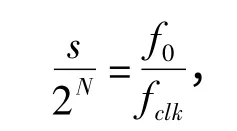

其中s是频率字,N是相位累加器的位数,也即查找表地址的宽度,f0是数控振荡器的输出频率,fclk是时钟频率。

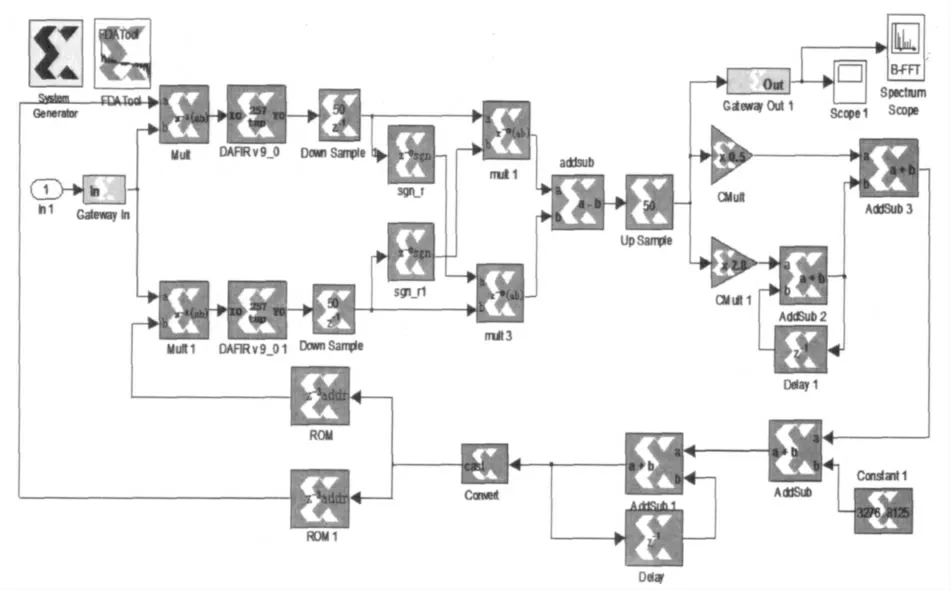

2.3 QPSK相干解调框图

图1为利用System Generator 对QPSK相干解调电路建模的原理图。图1 中的Gateway In 模块用来将由Simulink 中非Xilinx 模块搭建的QPSK 调制输出信号送入图中的相干解调电路进行解调(由非Xilinx 模块构建的调制原理图未画出),Gateway Out模块连接示波器和频谱仪可以观看鉴相器的输出信号和频谱图。

3 仿真结果及分析

3.1 参数设置

系统的基本参数为:符号速率为50K symbol/s;载波频率为500KHz;采样率为10MHz。

图1 QPSK相干解调原理图

3.2 有相位差时解调输出情况

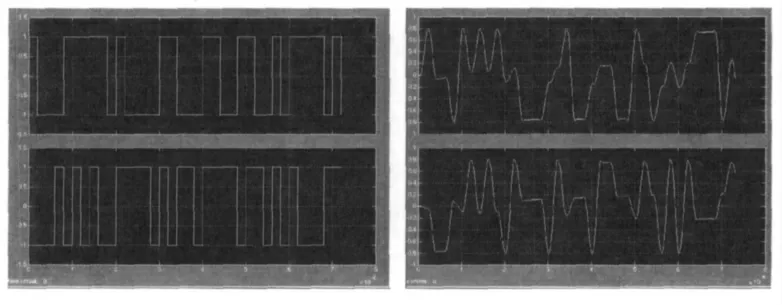

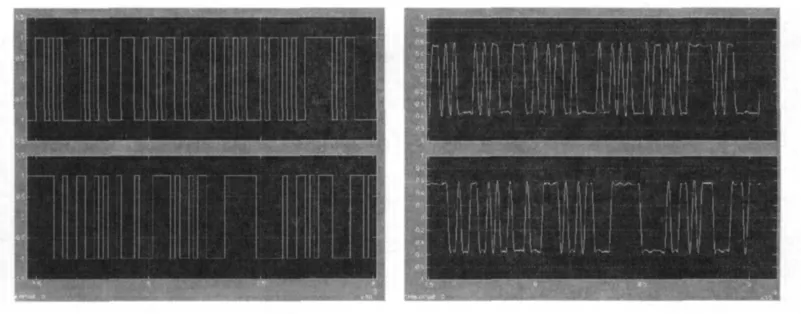

为了验证锁相环的工作性能,设置一定的相位差,仿真一段时间观察锁相环对系统的影响。正弦载波和余弦载波的相位分别设为0.1 和pi+0.1,即相位差为0.1rad。仿真波形如图2 和图3 所示,图2为同相支路信号,图3为正交支路信号。

图2 未同步时发送信号波形和解调信号波形

从图2 和图3 可以看出,解调后的信号波形变得平滑,这是由于信号经过升余弦滤波器的滤波作用导致的。仿真开始阶段,由于本地载波和发送载波不同步,解调后的信号波形与发送的信号波形差别较大,误码率很大;但经过一段时间的反馈调整后,收发载波基本达到同步,从图中可以看出收发信号基本一致,锁相环工作基本能满足相干解调的要求。

4 结束语

QPSK 调制技术具有电路实现简单、频谱利用率高和较强的抗干扰等优点,因此广泛应用于数字无线通信中。在解调方式的选择中,由于相干解调较其他方式误码率低,因此QPSK 系统常利用相干解调对接收信号进行解调,相干解调要求在本地产生一个与发送载波同频同相的本地载波,而锁相环技术则是实现这一要求的理想选择。本文通过在Simulink 中借助于Xilinx 公司提供的仿真建模软件System Generator,构建QPSK 系统的解调电路图,通过实验仿真,理论上验证了锁相环技术能够较好的产生与发送载波同频同相的本地载波,实现正确的解调。

图3 锁相环锁定时发生信号波形和解调信号波形

[1]Proakis G J.Digital Communications Fourth Edition[M].北京:电子工业出版社,2006.

[2]纪志成,高春能,吴定会.FPGA 数字信号处理设计教程-System Generator 入门与提高[M].西安:西安电子科技大学出版社,2008.

[3]Best R E.Phase-Locked Loops[M].London:Mc Graw Hill,2003.

[4]Wolaver D H.Phase-Locked Loop Circuit Design[M].Singapore:Prentice Hall,1991.

[5]郑逸群.非均匀取样信号数字频谱基本理论和高速波形数字化仪[J].国外电子测量技术,2005(5):2-9.

[6]刘强,郑莹娜,李扬,等.基于LabVIEW 平台和GPIB 接口的测试系统开发及应用[J].电子技术应用,2000(9):40-42.