低功耗低电源线噪声纳米CMOS 全加器*

2012-07-20董在望

田 曦,乔 飞,董在望

(清华大学电子工程系,北京 100084)

1 引言

算术运算广泛存在于诸如数字信号处理器、微处理器等各种数字系统中,全加器单元电路是构成加法器、乘法器、除法器、指数运算等复杂算术运算电路的基本单元,提高全加器电路的性能对于改善整个数字系统的性能是至关重要的[1]。随着CMOS集成电路制造工艺进入纳米阶段,各种电池供电的便携式电子设备需求的快速增长,类似于提高电路运算速度,降低电路功耗、提高电路可靠性等已成为数字集成电路设计的重要目标。

数字CMOS 集成电路的功耗包括动态功耗和漏电功耗。动态功耗主要来源于对电路节点负载电容充/放电所产生的功耗,可以通过减少电路节点的信号翻转率等方法来降低动态功耗。对于纳米CMOS集成电路而言,漏电功耗快速增长,将赶上甚至超过动态功耗,成为集成电路功耗的重要组成部分[2],漏电功耗包含以下三种主要组成成分:亚阈值漏电功耗、栅极隧穿漏电功耗和能带间隧穿漏电功耗。

降低纳米集成电路漏电功耗的方法包括:输入矢量控制,衬底偏压和电源门控[2]。在这些方法中,电源门控技术,已被证明是一种最有效的方法,它使用高阈值电压的晶体管作为休眠晶体管,并且在电路处于待机状态时关断休眠晶体管。由于堆栈效应,电源门控电路的亚阈值漏电功耗和栅极隧穿漏电功耗会显著降低[3]。

但是当一个电源门控电路从待机休眠状态切换到工作状态时,会有较大的开启电流流经休眠晶体管到地,由于地线及与地线相连的压焊线、封装引线上存在寄生电感,快速变化的开启电流会在地线引起较大的电压波动(电源线噪声)[4],电源线噪声会影响周围处于工作状态中电路的性能和可靠性,还会导致电路的噪声容限下降。

提出一种适于纳米CMOS 集成电路工艺的低功耗低电源线噪声的全加器电路,所设计电路用Hspice 在45nm CMOS 工艺下仿真,在平均功耗时延积、漏电功耗和电源线噪声等电路性能指标方面取得了明显的改进。

2 电源门控全加器结构

全加器单元电路的性能直接决定了数字系统的性能,国内外学者已提出多种基于不同逻辑风格的高性能全加器电路[1、5],如:伪NMOS 逻辑电路,传输管逻辑电路,传输门逻辑电路,静态互补CMOS 逻辑电路和动态CMOS 逻辑电路等。

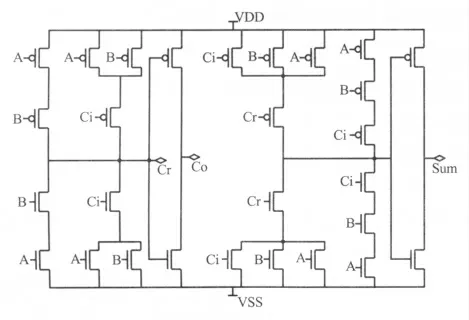

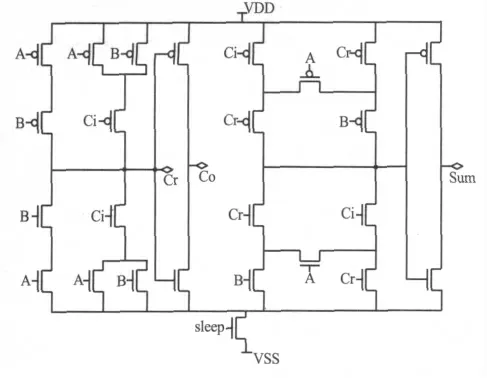

静态互补CMOS 逻辑电路具有良好的噪声稳定性(对噪声的灵敏度低),相比以上其它类型的逻辑电路更适合于按比例降低电压,对电源电压和晶体管尺寸的按比例缩小有良好的稳健性,在较小的晶体管尺寸和较低的电源电压下仍能可靠的工作,并且设计工具比较完备,适于纳米集成电路工艺[6]。静态互补CMOS 全加器结构如图1 所示[1],由以PMOS 管组成的上拉电路和以NMOS 管组成的下拉电路构成。

图1 互补CMOS 全加器

为提高全加器电路的噪声容限,获得尽可能对称的上升/下降传播延时和电压传输特性(VTC),图1 中全加器上拉电路的PMOS 管和下拉电路NMOS管的宽度比一般取2。

全加器电路的设计目标一般为降低电路的动态功耗,提高电路速度,以实现最小的动态功耗-延时积。但是对于纳米CMOS 集成电路而言,由于电路漏电功耗占电路总功耗的比重逐步增大,降低电路漏电功耗成为降低电路总功耗的关键所在。

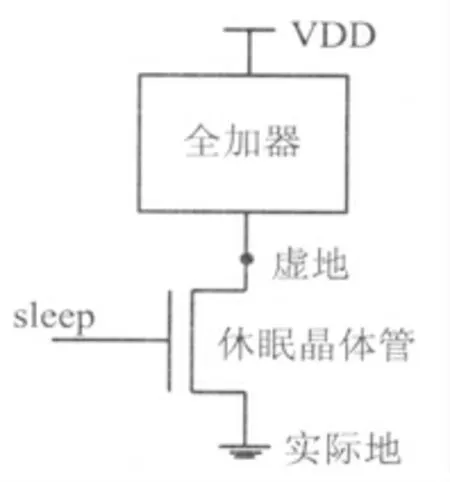

为降低全加器电路的漏电功耗,通过加入休眠晶体管,构成如图2 所示的电源门控结构。需要注意的是:休眠晶体管的插入,必然会影响全加器电路的正常工作性能,需要优化休眠晶体管的尺寸,以在尽可能减小休眠晶体管对全加器电路延时影响的情况下,实现最小的漏电功耗。

图2 电源门控全加器结构

3 全加器电路的改进

如图1 所示的传统互补CMOS 全加器,其上拉电路和下拉电路完全对称,完成如下计算:

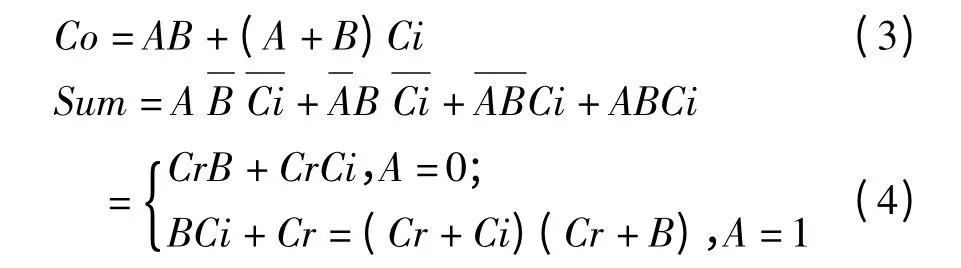

上式中,Ci是前级的进位输出,A、B是加数,Co是本级的进位输出,Sum是本级的和输出。设Cr是Co的补信号,由式(1)和式(2)可以推导如下:

根据式(4),设计如图3 所示的电路来实现全加器电路的求和运算,S是Sum的补信号。

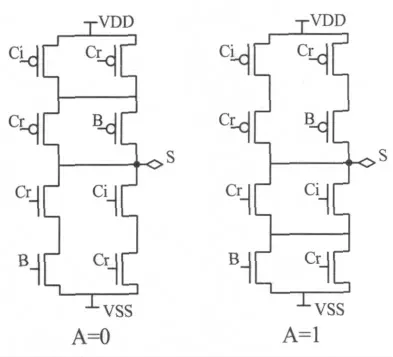

组合图3 中的A=0 和A=1 这两种运算,可得改进的电源门控全加器电路如图4 所示。

比较图4 所示的全加器电路和图1 所示的传统互补CMOS 全加器电路可见,改进的全加器电路的上拉电路和下拉电路仍然是完全对称的,并且其晶体管数量由传统互补CMOS 全加器的28个减少为24个,减少了14.3%,晶体管数量的减少,从直观上看,可以降低电路的漏电功耗。

全加器电路性能的改进不仅依赖于如前所述的逻辑优化,还依赖于晶体管尺寸的优化。同时对全加器电路和休眠晶体管进行统一分析,把二者视为一个整体进行电路优化,以获得最优的电路性能。对晶体管的尺寸优化通过迭代的方法进行:①所有的晶体管设为工艺允许的最小尺寸;②通过仿真得到最大延时及相应关键路径;③改变关键路径上的晶体管尺寸;④重复2、3,直到功耗-延时积最小;⑤取最小功耗-延时积对应的晶体管尺寸为优化尺寸。

图3 求和级的改进

图4 改进的电源门控全加器电路

4 实验和仿真结果

所有的电路仿真测试均基于45nm CMOS 工艺,电源电压1.0V[7]。

4.1 平均功耗和时延

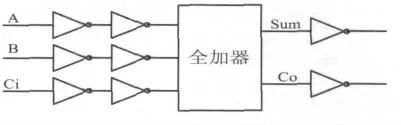

平均功耗指电路处于工作状态时的平均功耗,包括电路节点负载电容充/放电的动态功耗以及处于关断状态晶体管的漏电功耗。为了测试实际电路环境下全加器的平均功耗和时延,构建如图5 所示的全加器电路仿真结构。

图5 全加器仿真电路

输入信号A、B 和Ci 通过三个缓冲器(用级联的反相器实现)送入全加器,尽可能真实的模拟实际输入信号;输出信号Sum 和Co 分别接一个反相器做为设定的负载条件。

由于全加器不同的电路结构中有不同的分布电容,对一种结构有最大功耗的输入组合,对另一种电路结构而言可能会有较低的功耗;反之对另一种输入组合也会有类似情形。设计了一种输入组合,可以覆盖所有的输入状态,并且在不同的输入端交替形成较高的跳变频率。

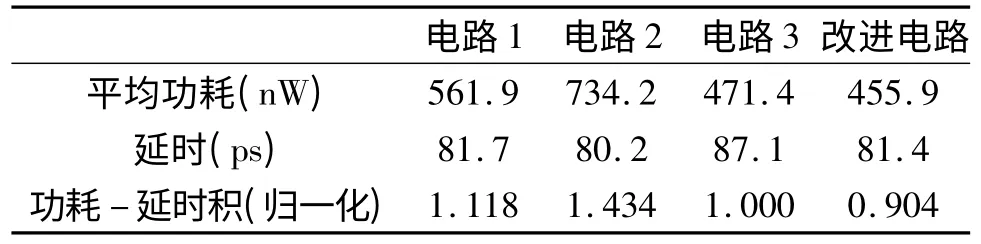

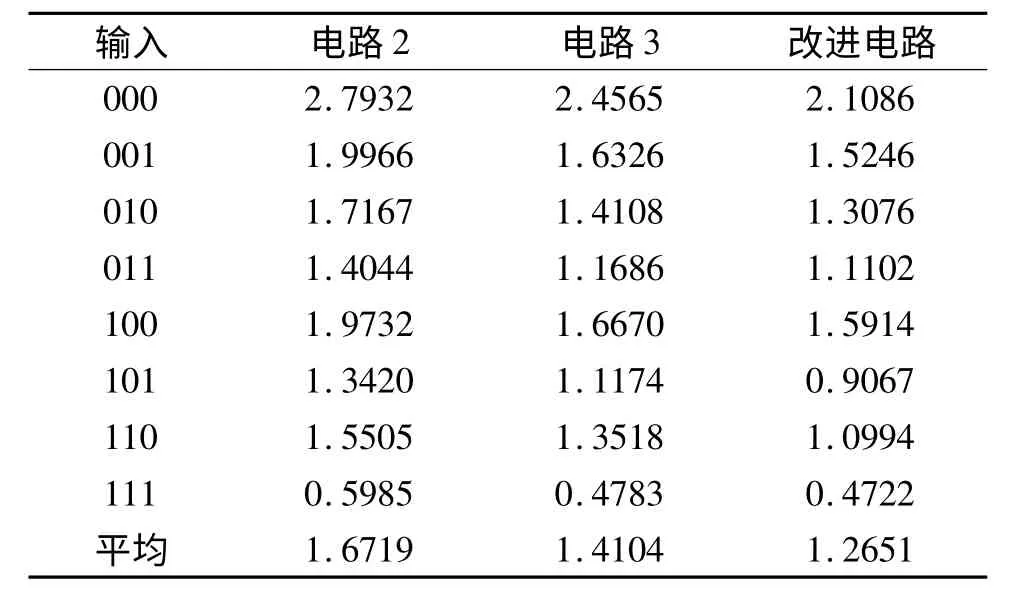

平均功耗和时延测量结果如表1 所示,其中“电路1”为如图1 所示的传统互补CMOS 全加器电路,“电路2”、“电路3”为如图2 所示的电源门控传统互补CMOS 全加器电路(上拉电路PMOS 管和下拉电路NMOS 管的宽度比分别取3 和1.5),“改进电路”为如图4 所示改进的电源门控全加器电路。

表1 全加器电路的平均功耗和时延

从表1 所示的测量结果可见:对于同样的全加器电路结构,晶体管尺寸较大,全加器的计算速度较快(延时较小),但同时其平均功耗也会增加;改进的全加器相比电路3的全加器,平均功耗降低了3.3%,延时缩短了6.5%,功耗延时积减小了9.6%。

4.2 漏电功耗

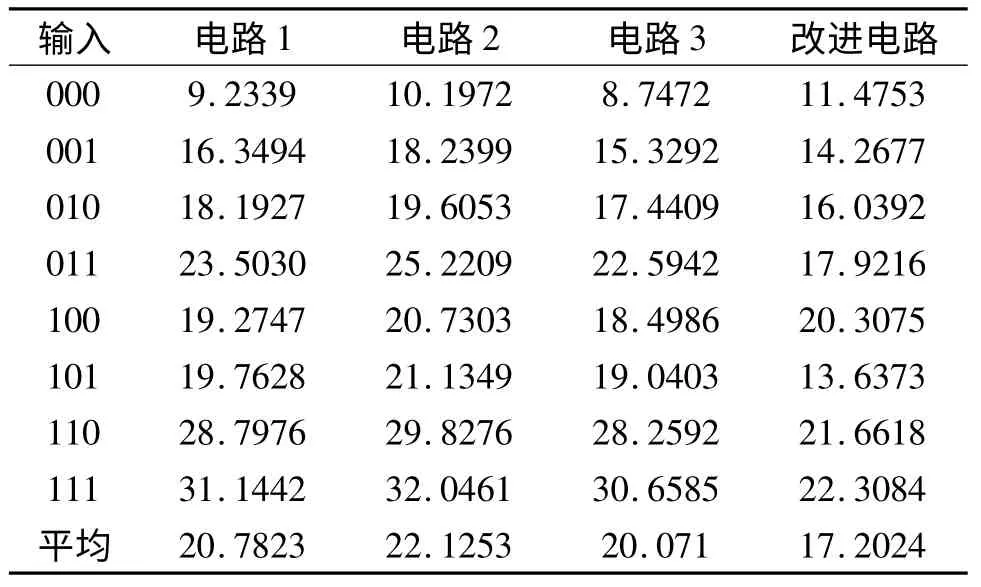

全加器处于待机状态时,电路节点不发生状态变化,不存在对节点负载电容充/放电的动态功耗,电路中处于关断状态的晶体管的漏电流导致漏电功耗。休眠晶体管控制信号sleep=1时,NMOS 休眠晶体管导通,对于各种输入矢量组合,全加器电路的漏电功耗如表2 所示(电路1 无休眠晶体管),单位nW。休眠晶体管控制信号sleep=0时,NMOS 休眠晶体管关断,对于各种输入矢量组合,全加器电路的漏电功耗如表3 所示(电路1 无休眠晶体管),单位nW。

比较表3 和表2的漏电功耗结果可见,如图4所示改进的全加器电路具有最小的漏电功耗。

表2 全加器电路的漏电功耗(sleep=1)

表3 全加器电路的漏电功耗(sleep=0)

4.3 电源线噪声

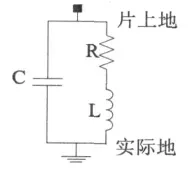

由前述可知,全加器电路唤醒过程中的电源线噪声主要是由于电源地上的寄生电感所致,其中,又以集成电路封装的寄生电感的影响最为明显。采用如图6 所示的DIP40 封装模型[8]来分析全加器电路唤醒时的电源线噪声,相应的R、L、C 数值分别为:0.217Ω、8.18nH 和5.32pF。

图6 DIP40 封装模型

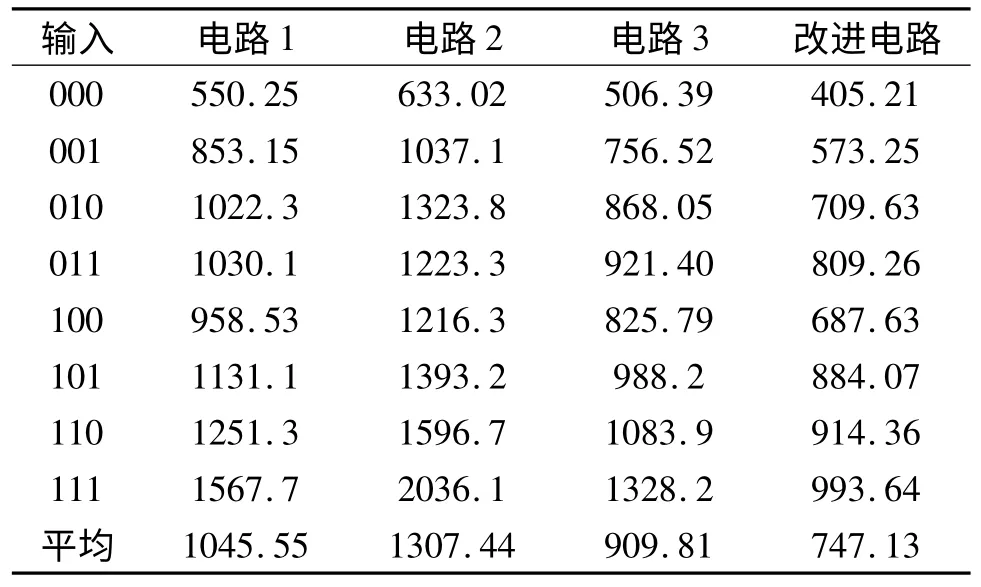

对于全加器的不同输入矢量,全加器唤醒时的电源线噪声的最大峰峰值电压如表4 所示,单位μV。为了进一步比较,“电路1”是图1 所示互补CMOS 全加器加入休眠晶体管后的的优化电路。

从表4的测量结果可见:在全加器唤醒过程中,如图4 所示改进的全加器电路具有最低的电源线噪声,相比其它几种全加器电路,电源线噪声峰峰值的改进在18%以上。

表4 全加器唤醒时电源线噪声的最大峰峰值电压

5 结束语

提出了一种适于纳米CMOS 集成电路工艺的低功耗低电源线噪声的全加器电路,在45nm CMOS 工艺下,通过Hspice 仿真验证了该电路在平均功耗时延积、漏电功耗和电源线噪声等方面都取得了很好的效果。

[1]拉贝艾,等.数字集成电路:电路、系统与设计[M].周润德,等译.北京:电子工业出版社,2010.

[2]K Roy,S Mukhopadhyay,H mahmoodi- meimand.Leakage Current Mechanisms and Leakage Reduction Techniques in Deep-Submicrometer CMOS Circuits[J].Proceedings of the IEEE,2003,(91)2:305-327.

[3]Siva G Narendra,A Chandrakasan.Leakage in nanometer CMOS technologies[M].New York:Springer- Verlag,2006.

[4]H Jiao,V Kursun.Ground bouncing noise suppression techniques for MTCMOS circuits[C].IEEE Asia Symp.Quality Electron.Design,Jul.2009:64-70.

[5]Dimitrios Sourdis,Christian Piguet,Costas Goutis.Designing CMOS Circuits for Low Power,European Low-Power Initiative for Electronic System Design[M].Boston:Kluwer Academic Publishers,2004.

[6]Harry Veendrick.Nanometer CMOS ICs:From Basics to ASICs[M].New York:Springer-Verlag,2008.

[7]Nanoscale Integration and Modeling (NIMO)Group,ASU.Predictive Technology Model (PTM)[DB/OL].[2009-01].http://www.eas.asu.edu/~ptm/.

[8]S Kim,S V Kosonocky,D R Knebel.Understanding and minimizing ground bounce during mode transition of power gating structure[C].Int.Symp.Low-Power Electron.Design,Aug.2003:22-25.