基于IP 核技术的SoC 设计

2012-07-20李洪海

韩 煜,李洪海

(中国电子科技集团公司第四十七研究所,沈阳 110032)

1 概 述

随着集成电路(Integrated Circuit,IC)设计技术和工艺水平进入超深亚微米,集成电路规模越来越大,芯片设计规模和设计复杂度也急剧提高,工艺流程呈现专业化,EDA 设计逐步发展和完善。九十年代出现了SoC 芯片,即可以在一个芯片上集成CPU、DSP、逻辑电路、模拟电路、射频电路、存储器和其它电路模块以及嵌入软件等,并相互连接构成完整的系统。

IP 有软核(soft IP)和硬核(hard IP)两种类型。前者以可综合的硬件描述语言(HDL)代码的形式交付;后者则用制定的工艺进行了功耗、面积或者性能的优化,以GDSII 格式交付。软IP 在配置后可针对多种硅工艺,易于被SoC 开发环境采纳,灵活性极高,但是成本也高。况且,软IP 不具备可预测性,每次使用后需要再次校验。硬IP 则恰恰相反,不仅具有可预测性,而且每次使用后也无需校验,可是大量预设的硬IP 设计参数限制了其灵活性。因此,融合软IP的灵活性和硬IP的预测性无疑是支持基于IP核设计的最佳选择。

成功地在SoC 开发中采用真正的IP 核结构,化解产品生产周期压力,需要做到:

·硬化:迅速优化配置并使软IP 硬化;

·建模:高度精确地为硬化的软IP 自动建模;

·集成:将模型综合到现有的SoC 设计流程中;

·验证:IP 核是否符合设计者的想法。

2 IP 核的硬化

使软IP 硬化成为IP 核的过程就是在标准规定的速度、功率和范围内以目标工艺实现IP。该实现必须能够提供准确的建模、自动化方法、工艺易于移植,以及具有基于业界标准的电子设计自动化(EDA)工具。硬化过程首先需要IP 供应商提供高质量RTL(寄存器传输级)描述,并且提供一套完整的GDSII 设计实现方案。

鉴于软IP 核固有的可配置性,必须对之予以妥善管理,为被授权者提供方便的目标应用IP 核配置。由于IP 核的实现是与整个芯片相对应的,因此必须充分考虑实现IP 核硬化的方式及其摆放位置。

3 IP 核的建模

典型的SoC 设计流程包括:功能模型、时序模型、测试模型、物理模型和功率模型。除了功能模型,其它模型都必须在一个物理执行的核里构建。功能模型可由RTL 或物理执行设计构建。

3.1 功能模型

功能模型必须在IP 核硬化前向最终用户提供,必须代表系统仿真中的IP 核周期特征,并且必须能够在门级仿真中支持精确到比特的RTL 仿真和时序注释。此外,功能模型还应消除仿真器特殊结构和接口,在仿真环境中便于移植。

由于模型构建过程实际上是C/HDL 设计的二进制目标模型,因此只需极少的额外工程设计。由于最终用户设计环境的不可测性,因此所有通过使用编译器构建的模型必须可以在仿真器、各种语言、硬件平台和操作系统上充分移植。采用PLI 和SWIFT 接口后,这些模型可在编译器和非平台环境下移植。当今大多数商业仿真器都支持SWIFT 接口,并提供有效的基于PLI的接口。

编译模型不仅独立于编译器和平台,还应支持SoC 设计过程中任何时段的使用。为优化仿真性能,在不同的设计时段里构建模型的能力就十分重要。

该模型的功能性和时序分开,因此只要提供正确的级别时序信息,就能在各种设计的抽象级别使用。

3.2 时序模型

时序模型具备所有的时序特点,在逻辑综合、物理综合、测试综合、静态时序分析、时间驱动地点和路线等设计步骤中得到采用,可能是软IP 核硬化在SoC 设计流程中应用最广泛的模型。因此,时序模型的准确性就变得尤为重要,必须达到以下要求:

(1)黑匣子:不得显示IP 核的执行细节;

(2)独立性:时序模型必须独立,并支持SoC 环境条件的变化;

(3)准确性:时序模型必须在录制磁带前为SoC提供完整的信号模型;

(4)业界标准:鉴于时序模型在系统设计过程中的大量应用,因此必须采用业界标准的EDA 工具。

3.3 测试模型

IEEE 规定了一个IP 核测试语言(CTL),定义了嵌入式IP 核和SoC的测试接口。该语言通过IP核访问以及隔离机理推动了嵌入式IP 核的再利用,为SoC 互联和逻辑提供了可测试性。此外,该语言支持即插即用协议的IP 核测试互用性。CTL 支持多种测试方式,如Scan(扫描)和BIST(内建目测试)等,并且不支配IP 核自身使用的测试方法。

构建测试IP 核的程序包括:①对IP 核进行测试包装;②在包装后的内核上执行多模型DRC(设计规则检测);③为包装后的IP 核内指明CTL种类;④为包装后的IP 核构建测试模型。

成功包装IP 核以后,一个CTL 包装IP 核即构建成功。该CTL 将IP 核包装为完全符合业界标准(IEEE P 1500)的基于ASCII的模型。因此,该模型可在支持P 1500的所有EDA 工具中移植。

3.4 物理模型

物理模型是IP 核具体物理实现的抽象,必须包含足够的信息满足以下IP 核系统设计实现的需要:平面布置;置换(包括物理合成);具体线路安排。

该模型必须准确表述:

·元件占用面积:IP 核本身的面积,长宽比和来源;

·接口引脚/端口数量:每个IP 核I/0 端口的名称、尺寸、形状、位置、连接层和相应引脚的数量;

·线路障碍:IP 核上线路障碍的面积、形状和影响层面等;

·电源和接地:每个电源连接的名称、面积、形状、位置和接线层;

·SI 作用:每个IP 核的I/O 端口提供有关高级别天线的计算。采用二极管或层面变化时,可在IP核慎重处理这些作用;

·信令/标志:独特的识别信号不仅提供IP 核,还可修订和配置IP 核。

3.5 功率模型

功率模型描述了IP 核功耗,必须忠实反映:

·静态和动态功耗;

·I/O 端口和内部节点的开关状态;

·I/O 端口和内部节点的状态;

·运行方式(如测试方式);

·运行、电压和温度等条件以及电容负载和输入瞬变时间。

4 IP 核的集成

选择IP 核时首要考虑的因素是IP 与目标系统的配合程度。对于已有的IP 核,优先选择芯片面积最小、运行速度最快、功率消耗最低、工艺容差最大的IP 核。一般说来,在进行集成之前,最好选择那些无需修改的IP 模块。但大多数情况是设计人员在获得IP 模块后必须进行修改,修改的范围包括各个设计层次上的IP 模型。为了使开发的IP 核能够高效地集成到新的设计中去,设计复用(Design Reuse)和标准化是必由之路。在IP 集成之前,必须先解决下面几个重要问题:

第一,在系统结构设计和模块划分时,必须考虑好系统芯片采用什么样的片上总线结构,确定哪些模块来自于IP 库,哪些模块需要购买IP,IP 模块的对接需要增加哪些连接性设计。

第二,模块间的接口协议要尽可能简单,模块间的接口定义尽可能与国际上通用的接口协议一致。这虽然会造成芯片在时序、面积、功耗等方面的损耗,但对于加快系统芯片的上市速度很有利。

第三,要注意积累集成的经验。一旦成功地集成了一个IP 到一个系统设计,就应该进一步完善该IP;同时,把集成该IP的经验教训及时记录下来形成技术文档,这将对下一个IP 集成十分有利。

第四,必须在时钟分布,关键路径的走线,电源、地线的走线,模块支持的测试结构等方面考虑与系统芯片保持一致。

5 IP 核的验证

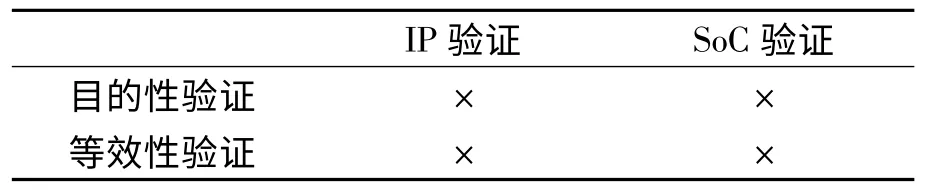

IP 核验证技术和方法可按照表1 所示的体系进行分类,其中将验证分为四大块。

表1 功能验证分类

5.1 目的性验证

目的是验证设计者所预想的功能是否在设计中得到正确实现。通常,目的性验证在最高抽象层次上完成。其最终结果是建立一个所谓的“黄金模型”,该模型可以作为整个设计过程中各种更加详细的设计视图的参考基准。

5.2 等效性验证

目的是验证在设计过程中生成的不同 层次的设计功能是否与“黄金模型”功能相一致。

5.3 IP 验证

指对单个lP的功能进行验证的过程,即单元测试。

5.4 集成验证(SoC 验证)

指对包含一个或多个IP的SoC 进行功能验证的过程,即SoC的系统级验证。以上每项验证任务所使用的技术和工具之间存在很大的重叠。虽然IP的验证和SoC的验证过程相同或者相似,但是验证测试组件的模型和源代码集则可能不同。对IP验证,关键是验证IP 内部逻辑的详尽功能以确保IP的正确实现。而SoC 验证则是把重点放在I P的连接和相互作用上,验证所用模型应能精确地仿效IP接口,而对IP的内部功能只需能够近似地塑造即可。

6 结束语

SoC 设计方法已经成为了IC 设计的主流。SoC可以充分利用已有的设计积累,显著地提高ASIC的设计能力,缩短设计周期,缩小设计能力与IC 工艺能力的差距,而SoC 设计技术的关键是IP 及其复用技术,如何利用经过验证的IP,成功地把IP 集成到SoC 系统中,是限制设计能力的瓶颈问题。

[1]Keating M,Bricaud P.Reuse Me thodology Manual for Systerm-on-a-Chip Designs[M].Third Edition.New York.Klu wer Academic Publishers,2002.

[2]银燕,汤帜.数字版权保护技术研究综述[J].计算机学报,2005,28(12):1957-1968.

[3]Garnett N.Digital rights management,copyright,and napster[J].ACMSIGecom Exchanges,2001,2(2):1-5.