三模冗余MPSOC容错设计与验证

2012-04-17杨孟飞刘鸿瑾

陈 陈,杨孟飞,刘鸿瑾

(1.北京控制工程研究所,北京 100090;2.中国空间技术研究院,北京 100194)

航天技术的发展对以星载计算机为代表的空间电子系统的性能、体积、功耗、重量、可靠性及空间环境适用性的要求越来越高.片上系统(SOC,systemon-chip)技术不仅可以提高星载计算机的内部功能集成度、减小体积重量、提高功能密度,而且可以提高性能,提高系统的总体可靠度.多处理器片上系统(MPSOC,multiprocessor system-on-chip)[1]具有多处理器系统和单处理器SOC的共同优点,代表着嵌入式多核设计的发展方向.MPSOC具有良好的扩展性、可定制化设计等特点,尤其在提高系统并行性方面显示出巨大优势.

研究表明,计算机系统中70~80%的失效都是由于瞬态故障引起[2],这表明瞬态故障是引起计算机系统失效的主要原因.在航天等特殊应用场合,瞬态故障也将是引起处理器以及计算机系统失效的主要原因,并且随着特征尺寸的减少,这一趋势将会越来越明显[3].因此,为了提高航天等特殊应用场合下处理器的可靠性,消除瞬态故障所引起的软错误(soft error)[4]的有害影响是一个重要的任务.在多核体系结构中,存在多个内核,可以设计为冗余运行的处理结构,因此除了并行性之外,还具有容错潜力.只要合理有效地利用这些冗余硬件资源,就可以在减少额外开销的基础上,提供更强的容错能力.

本文提出了一种能够检测并屏蔽瞬时故障的三模冗余(TMR,triple modular redundancy)MPSOC处理器设计方案.该系统由3个基于SPARC V8规范的LEON3处理器[5]、容错管理模块和选通电路等组成,采用软件表决和硬件仲裁相结合的方法完成三模冗余的容错功能.

1 三模冗余MPSOC处理器的容错设计

1.1 容错方案设计

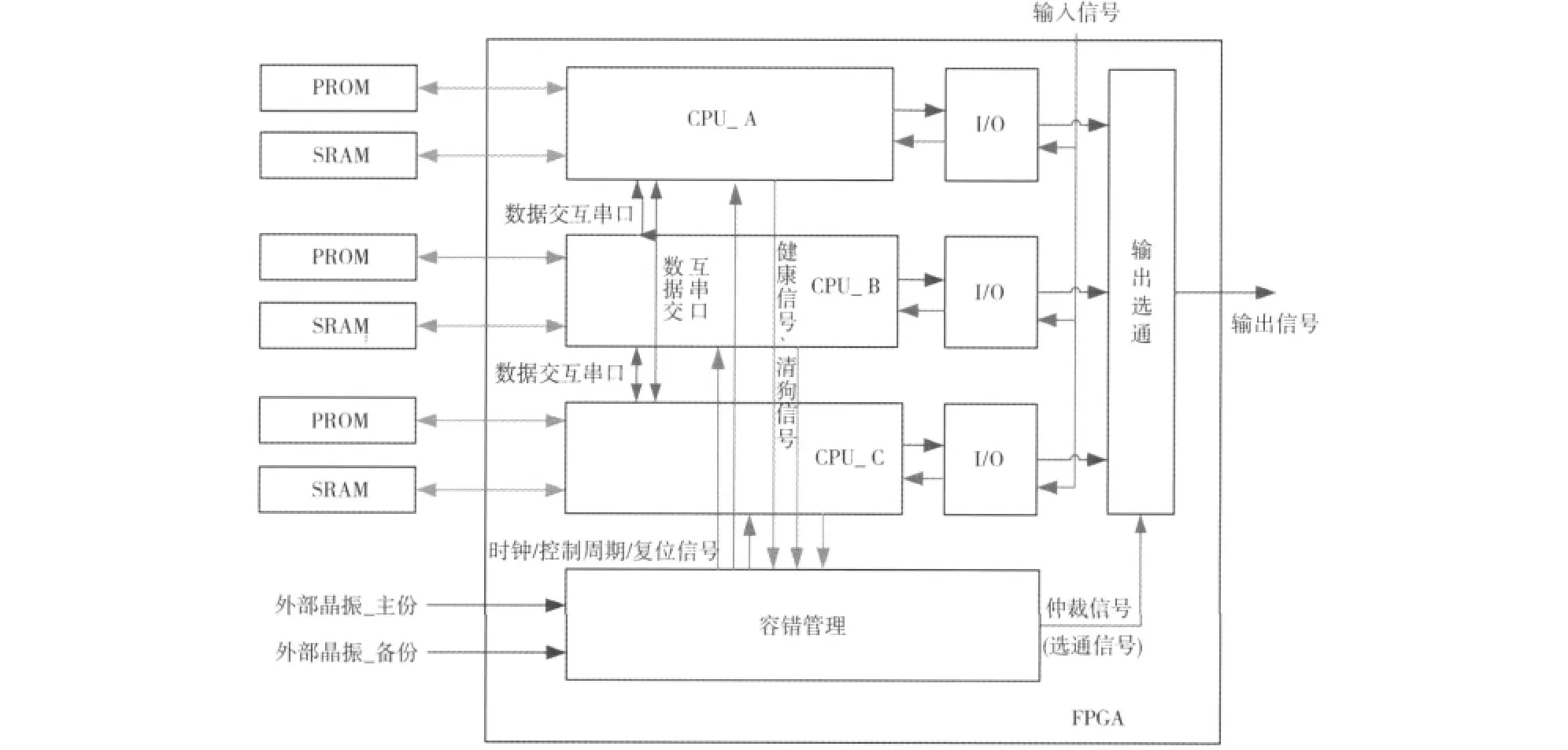

本文提出的三模冗余MPSOC容错处理器结构如图1所示.三模冗余MPSOC容错处理器基于FPGA设计实现,设计中采用了3个原理设计完全相同的LEON3处理器.3个处理器独立运行,每个处理器有独立的静态随机存储器(SRAM,static random access memory)和可编程序只读存储器(PROM,programmable read-only memory).3个处理器中其中一个为当班机,其他两个则为非当班机.当班机由容错电路仲裁产生,任意时刻只有当班机的数据输出.

图1 系统内部结构框图Fig.1 Architecture diagram of TMR system

三模冗余MPSOC处理器具体的容错策略是采用TMR数据表决输出的容错结构,在3个完全相同的处理器上运行相同的程序;3个处理器以串口通信的方式实现数据交换,软件进行三模冗余数据比对(部分浮点数据带容差比较),由软件进行3取2表决,最终向容错管理单元输出本机状态信息(健康信号、清看门狗信号等),由容错管理单元仲裁后输出当班信号,确定一个当班机,并选通当班处理的数据输出,当班机的输出数据作为系统输出的最终结果(如图1所示).

三模冗余MPSOC处理器容错设计的关键在于容错管理单元的逻辑设计、软件表决算法的设计及处理器之间的同步机制的设计,下面将详细描述.

1.2 容错管理模块设计

容错管理模块功能框图如图2所示,主要由时钟产生电路、看门狗电路、复位电路和当班仲裁电路组成,为了提高容错管理模块的可靠性,容错管理模块功能均采用双热备份的方式实现.容错电路的主要功能有:

1)为3个处理器提供时钟及控制周期信号;

2)通过看门狗电路监视当班机工作状态;

3)提供复位信号,同时送往3个处理器;

4)根据三机健康状态由硬件仲裁决定哪一机为当班机.

时钟产生逻辑用来产生时钟及控制周期信号.为了提高电路的可靠性,设计两套独立的时钟产生电路,主备份时钟信号可以实现自主切换.产生的时钟信号同时送往3个处理器作为控制周期信号,保证3个处理器采用同一时钟源.

看门狗电路用于监测当班机的工作状态.该电路设计的主要作用是当3个处理器均不能正常清看门狗时可产生自主复位,修复瞬时故障.当班机在每个控制周期内进行清看门狗操作,如果当班机不能正常清看门狗,则看门狗电路通过狗咬信号使处理器复位.看门狗复位由看门狗的狗咬信号产生,最终生成3个复位信号,分别送往3个处理器,保证所有处理器同时复位.采用两套独立的看门狗电路可以在单个看门狗电路失效的情况下,由另一路看门狗电路监视当班机的工作状态,在3个处理器都发生故障的情况下,通过狗咬复位使系统恢复正常.两路看门狗电路的清看门狗信号均由LEON3处理器的通用输入/输出端口(GPIO,general purpose I/O port)口产生.

仲裁电路根据各处理器的工作情况控制三机中的其中一机输出.三机输出的数据经软件3取2表决后,发出本机的健康状态信号,仲裁电路根据三机的健康状态信号决定哪一机输出,其他两机的输出均被封锁.三机健康状态信号SA、SB、SC为低电平有效.三机的当班信号CSA、CSB、CSC是高电平有效.

图2 容错管理模块功能框图Fig.2 Block diagram of the fault-tolerant management module

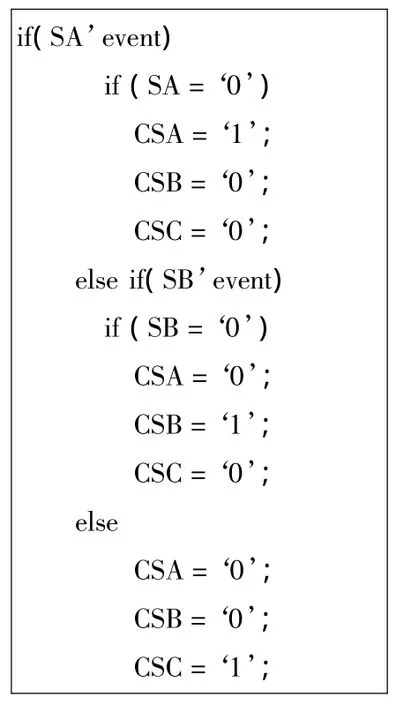

仲裁逻辑根据3取2的原则,即根据三机健康状态来决定输出哪一机的数据.同时,在仲裁逻辑的设计上保证了只能输出一机的数据.为防止仲裁逻辑电路单点故障,采用两套相同的电路,并联输出.三机的优先级是A>B>C,例如:如果SA,SB为低电平,SC为高电平,则仲裁模块输出CPU_A的数据;如果SA为高电平,SB、SC为低电平,则仲裁模块输出CPU_B的数据.

当班信号CSA、CSB、CSC的产生方式如图3所示.为防止三机都不输出的情况,即三机的状态SA、SB、SC都为“1”时,仲裁电路自主选择 CPU_C当班,由于CPU_C不健康,不清看门狗,则引起狗咬复位.为了防止仲裁电路短时间内的循环切换当班机,造成任务无法完成,设计中采用单向切换的方案.

图3 当班信号产生方式Fig.3 Generation of the on duty signal

最后输出选通模块使用容错管理模块产生的当班信号(CSA、CSB、CSC)来控制各处理器对外输出接口的使能端,保证只有当班机能够对外发送控制指令和信号,而其他两机的输出被禁止.

三模冗余MPSOC处理器对外输出的接口只有3种:串口、1553B总线和GPIO口.对于输入信号采集和接收电路的使能端则常有效,3个处理器都能够接收其他外部设备的输入数据和状态信号.

1.3 软件的3取2表决算法设计

三模冗余MPSOC处理器的3取2表决通过软件实现,由表决生成每一机的健康状态信号供容错管理单元的仲裁逻辑使用.

如图4所示,当每个控制周期某一机工作正常并且与其他任意一机的数据比对一致时,该机发送健康信号,该控制周期当班机正常清看门狗,下一个控制周期的数据计算使用该控制周期经过三机数据比对软件表决后的数据.

当某一机在一个控制周期与其他两机的数据比对都不一致时,该机首先判断其他两机数据比对是否一致,如果其他两机数据比对一致,则该机置自己不健康.

如果某一处理器判断三机数据比对都不一致,则该机查询自己的系统自检状态信息,如果系统状态信息正常,则该机置自己健康,如果系统状态信息不正常,则该机置自己不健康.

在出现三机数据比对均不一致时,如果三机的系统自检状态信息都不正常,则三机都置自己不健康,仲裁电路的硬件会自主选择CPU_C为当班机,由于CPU_C不健康,不清看门狗,则引起狗咬复位.三机同时复位后,尝试恢复重要数据,并重新进入TMR工作模式.

图4 软件表决算法原理框图Fig.4 Block diagram of software voting algorithm

1.4 处理器之间的同步设计

同步技术是三模冗余容错处理器的核心基础技术之一,它用来消除系统中3个处理器模块之间因时钟、输入延迟等因素造成的不同步,使得系统中3个处理器模块在程序执行状态、周期定时及时间基准上达到相对一致的状态,在计算后同时将输出送给仲裁电路进行表决输出,真正完成三模冗余功能.常用的同步技术包括任务同步、中断同步[6]、公共时钟、锁相同步[7]等.

本系统在三模冗余工作模式时实现3个处理器任务级同步[8]功能.系统通过容错电路产生3个处理器共用的控制周期信号和复位信号来实现任务级同步.三模冗余工作模式下,完成上电后3个处理器同时复位,这种情况下3个处理器控制周期信号同源可保证同时产生控制周期中断,通过控制周期中断进行任务调度,即可完成处理器间任务级同步.

2 实现与验证

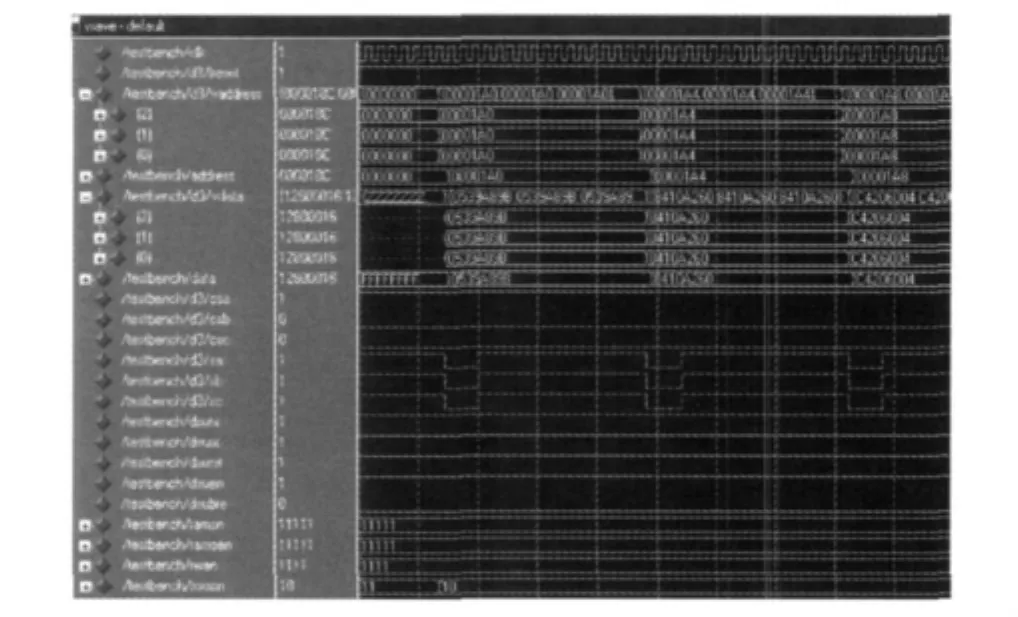

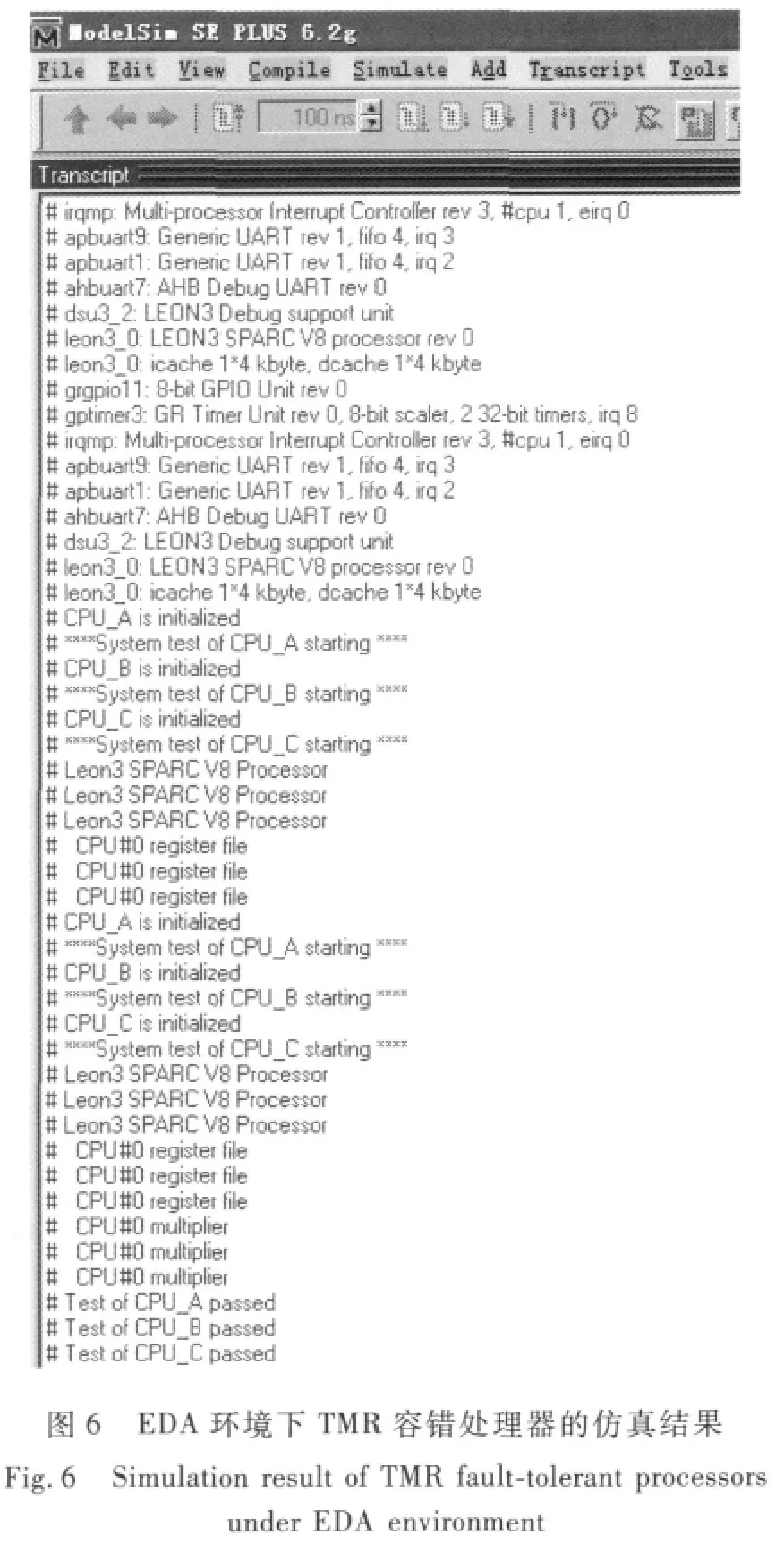

2.1 TMR处理器正常运行时的仿真结果

为了验证上述处理器系统的正确性,使用EDA仿真工具ModelSim对该系统进行仿真验证.图5所示为处理器正常运行时的仿真波形,其中vdata(0)、vdata(1)、vdata(2)分别为 CPU_A、CPU_B、CPU_C 3个处理器的运算结果,data为TMR处理器最后输出的结果.从仿真波形可以看出,3个处理器同时运行相同的程序,经过数据交换和比较后,向容错电路发送正常信号,SA、SB、SC均为低电平时表示相应的处理器处于正常工作状态.容错电路经过仲裁控制输出选通.当3个处理器都正常运行时,默认CPU_A为当班机.系统最后输出的数据data为CPU_A的输出数据vdata(0).图6所示为EDA环境下TMR容错处理器的仿真结果.

图5 3个处理器正常运行时的仿真结果Fig.5 Result of simulation when 3 processors run normally

2.2 TMR处理器故障注入时的仿真结果

为了验证处理器系统对错误的诊断和屏蔽能力,试验中模拟了处理器系统因存储区域被单粒子击中造成的翻转而发生的程序计算结果错误,并验证了在这种故障模式下处理器和容错电路的功能.

如图7所示,对CPU_A进行故障注入,假定其运算结果在某一时刻出现错误.由仿真波形可以看出,通过数据交换和比较,检测到处理器CPU_A中的错误,CPU_A的正常信号为“1”(该信号低有效),容错电路经过仲裁,将当班机切换至CPU_B,输出数据为vdata(1),同时清看门狗.系统最后输出数据data为CPU_B的输出数据vdata(1).

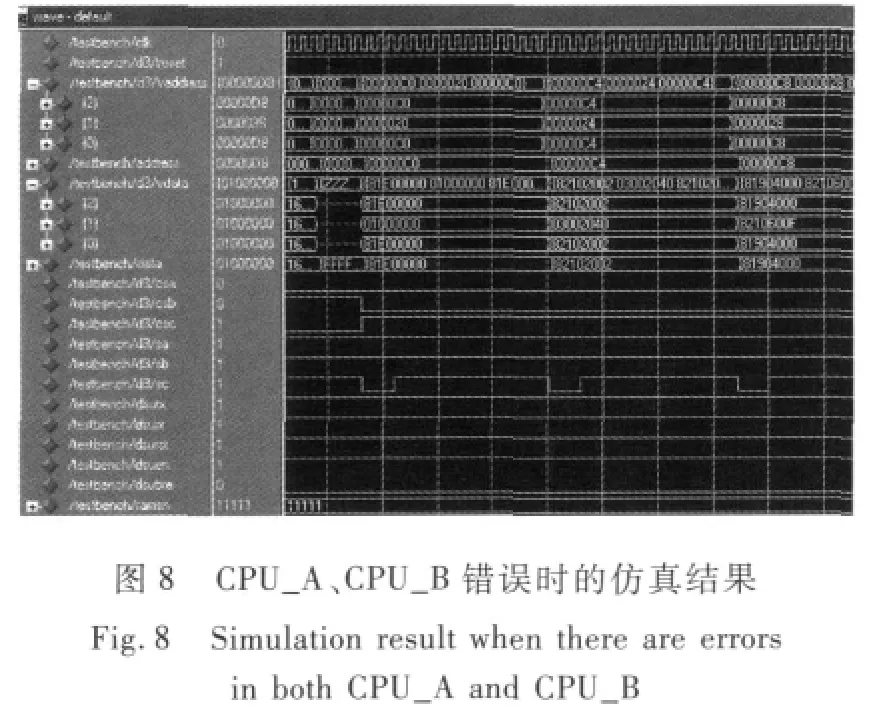

同样,继续对CPU_B进行故障注入,从仿真波形可以看出当CPU_B出错时,CPU_B的正常信号为“1”(该信号低有效).根据单向切换的原则,尽管CPU_A在当前时刻的输出正确,其正常信号仍为“1”(该信号低有效),仲裁电路将当班机切换至CPU_C,输出数据为 vdata(2),清看门狗(如图8所示).

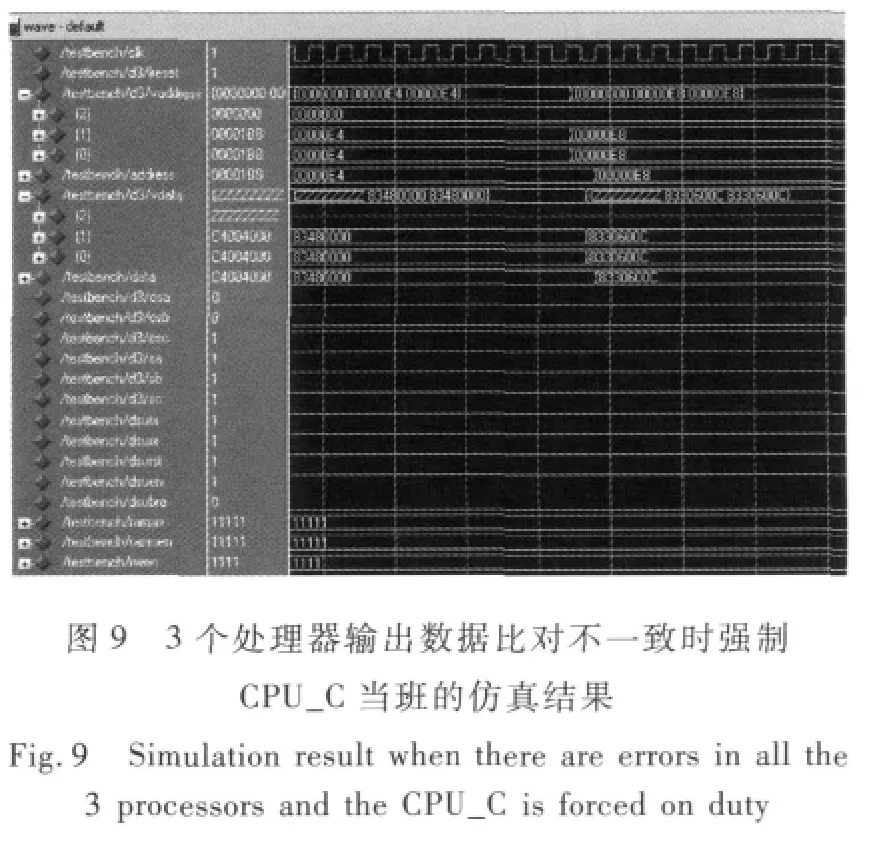

当3个处理器都不正常时,系统强制CPU_C当班,输出数据为vdata(2).如果当班机CPU_C不清看门狗,最后,狗咬复位信号lreset被触发,3个处理器同时复位,重新运行初始化程序(如图9、图10所示).

2.3 TMR处理器演示验证系统

TMR处理器原型基于Virtex IV 2000万门FPGA实现,最终完成综合、调试后的TMR容错处理器演示验证系统如图11所示.系统的核心功能(包括3个处理器和容错电路等)都集中在FPGA中实现.FPGA通过JTAG线缆与PC机连接.本设计的对外接口与单处理器系统相同,因此可通过Gaisler公司的调试工具GRMON在PC机上实现软件的加载、调试.以矩阵乘法运算程序作为测试用例,如图12所示,测试程序可以正常运行.该试验验证了本设计可以完成预定的处理功能.

本系统采用50MHz的晶振,通过数字时钟管理模块(DCM)处理后,系统实际时钟仍为50MHz.在该时钟频率下,系统的最大工作频率为70.4MHz,与单处理器系统相比性能下降了9%左右.根据布局布线后的结果,本设计占用的FPGA资源约为单处理器系统的302%.

3 结论

本文提出了一种用FPGA实现的基于软件表决和硬件仲裁相结合的容错处理器的软硬件设计方案,然后对这种容错设计方案进行了原型实现和验证.试验结果表明,该设计可以屏蔽瞬时故障,任意一个处理器故障或两个处理器故障时不影响正常当班机的输出,系统具备自主切换当班机的能力.

[1] Wayne W,Ahmed A J,Grant M.Multiprocessor system-on-chip(MPSOC)technology[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2008,27(10):1701-1713

[2] Karlsson J,Liden P,Dahlgren P,et al.Using heavyion radiation to validate fault-handling mechanisms[J].IEEE Micro,1994,14(1):8-23

[3] Mukherjee S.Architecture design for soft errors[M].San Francisco,CA,USA:Morgan Kaufmann Publishers Inc.,2008

[4] Mukherjee S S,Emer J,Reinhardt S K.The soft error problem:an architectural perspective[C].The 11thInternational Symposium on High-Performance Computer Architecture,San Francisco,CA,USA,Feb 2005

[5] Jiri G,Sandi H.GRLIB IP library user’s manual[M].Sweden:Gaisler Research,2010

[6] Xin M,Qiu Q.Research on precise synchronization for TMR fault-tolerant embedded computer[C].The 1stInternational Conference on Multimedia Information Networking and Security,Wuhan,China,Nov 2009

[7] Tomohiro Y,Takashi S,Yoshihiro T.Interrupt handling in the loosely synchronized TMR system[C].The 44thAsilomar Conference on Signals,Systems and Computers,Pacific Grove,USA,Nov 2007

[8] Mahyar R,Malekpour.A byzantine-fault tolerant selfstabilizing protocol for distributed clock synchronization systems[R].Dallas,TX,United States,NASA Report NASA TM-2006-214322,Nov 2006