基于FPGA的数控系统脉冲式速度控制模块实现技术

2012-04-10朱兴华左健民汪木兰

朱兴华,左健民,2,汪木兰,苏 薇

ZHU Xing-hua1,ZUO Jian-min1,2,WANG Mu-lan3,SU Wei4

(1. 常州数控技术研究所,常州 213164;2. 江苏技术师范学院,常州 213001;3. 南京工程学院 先进数控技术江苏省高校重点建设实验室,南京 211167;4. 江苏大学 机械工程学院,镇江 212013)

0 引言

速度控制功能在计算机数控(Computer Numerical Control,CNC)系统中发挥着重要作用,它接受插补运算结果(命令值),并控制伺服电动机,其性能直接影响和决定了CNC系统的快速性、精确性和稳定性。

由于技术的发展,脉冲式速度控制方式应用越来越广泛,不仅步进电动机工作于脉冲控制方式,而且交流伺服单元也可工作于脉冲控制方式。为了易于叙述实现思路和说明实现技术,本文以步进电动机伺服装置实现过程为例。步进电动机是一种将电脉冲信号转换成相应角位移和线位移的执行元件,其转速与电机绕组相电流的切换频率成正比。因其结构简单和运行稳定可靠,可以和其他元器件组成简单实用的全数字化伺服系统,且不需要反馈环节,故在数控系统脉冲式速度控制场合获得了成功应用[1]。步进电动机的起动频率特性使其启动时不能直接加载到运行频率,需要经历“启动—加速—恒速—减速—停止”的升降速过程[2]。对步进电动机速度控制实现方式的研究文献很多,如使用单片机与PC机、定时器和寄存器等实现速度控制[3~5],并且大多数是由软件实现,在控制的快速性和稳定性等方面不如早期的硬件电路。由于早期硬件电路较复杂,调整不便,后期的CNC系统中软件实现比较广泛。随着电子技术快速发展,FPGA(Field Programmable Gate Array,现场可编程门阵列)的综合性能和集成度等方面得到很大提高,可以满足软件硬化实现速度控制模块功能的需要[6]。本文介绍使用FPGA软件硬化技术实现数控系统中脉冲式速度控制模块功能,并采用定时法原理予以实现。

1 脉冲式速度控制

1.1 定时法脉冲式速度控制

步进电动机的速度控制规律一般有直线型、指数型和抛物线型速度控制[7]。由于步进电机的转速正比于控制脉冲的频率,故调节控制脉冲频率就可以达到调节电动机转速的效果。本文采用了直线型控制速度方案,相应的步进电动机速度控制过程如图1所示。

图1 步进电动机速度控制过程

实现直线型速度控制方案的方法有定时法和定步法。本文采用定时法实现升降速控制,即按一定的时间间隔(Dt)改变步进电动机的运行频率,从而实现升降速控制。为了确保步进电动机运行稳定且不发生失步或过冲现象,每改变一次运行频率,步进电机运行一段时间(一定步长)。在选择Dt时要注意每次的频率变化量不得大于步进电动机所允许的突跳频率值,否则会引起步进电动机发生失步或堵转现象,从而导致定位误差增大或无法正常运转,甚而会损坏电机。

1.2 脉冲式速度控制实现流程

如果进给的行程比较长,则脉冲式伺服单元的速度控制过程不但有恒速段,还包含升速段和降速段,且降速段是升速段的逆过程,相应速度(脉冲频率)变化曲线如图1(a)所示。如果进给的行程很短,不足以完成一个定时时间间隔的升速和降速过程时,就不必进行升降速控制,而是以较低的适当设定速度走完整个行程,则速度控制过程只有恒速段,相应的速度(脉冲频率)变化曲线如图1(b)所示。

根据最佳升降频控制规律[8],可推出步进电机的“频率—步长—时间”关系曲线如图2所示。

图2 步进电机的“频率—步长—时间”关系曲线

图2中,步进电动机以起始频率fs开始作升速运动,经过Dt时间,运动S1步长后,再以频率f1作升速运动,同样经过Dt时间,运动S2步长,如此经过若干Dt时间,到达频率fo,以fo作恒速运动,经过mDt 时间后作与升速过程相反的降速运动。Ss为升速段的总步长,Sj为升速段和恒速段的总步长,S为整个过程的总步长。频率与步长之间对应关系如表1所示,进一步根据图2和表1可以总结出脉冲式速度控制运动方式和相应的满足条件如表2所示。

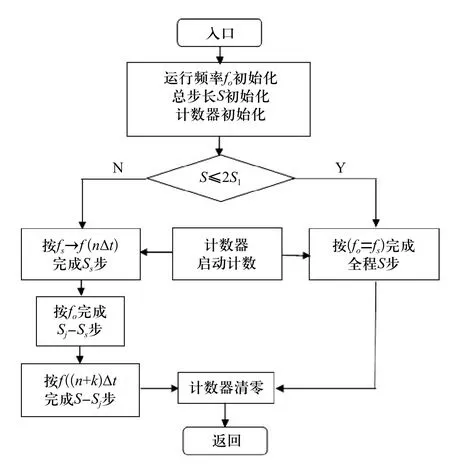

当模块初始化以后,首先根据S、S1、Ss和Sj等变量之间的关系,选择相应的运行方式,然后根据如图3所示的脉冲式速度控制流程走完整个行程。

表1 运行频率变化与步长之间对应关系

表2 脉冲式速度控制运行方式及满足条件

图3 脉冲式速度控制流程

2 脉冲式速度控制模块设计与实现

2.1 FPGA和Quartus II

CYCLONE II 系列FPGA器件是美国Altera公司的中端产品,本文选用器件型号为EP2C8芯片,它具有8256个逻辑单元(LE),26块M4K存储器,165888 bits存储器容量,13个乘法器,2个锁相环(PLL),182个用户可用引脚数。

Quartus II设计软件是Altera提供的FPGA软件开发环境,由原先的MAX+PLUS II演变而来,继承了MAX+PLUS II工具的优点,能够直接满足各种设计需要,可为单芯片可编程系统(SOPC)提供全面的设计环境,已成为Altera公司新一代的EDA设计工具。

2.2 脉冲式速度控制模块的硬化实现

脉冲式速度控制模块由复位单元、分频单元和速度处理单元组成。使用软件硬化技术把步进电动机升降速软件实现过程采用FPGA硬件电路实现,并将整个脉冲式速度控制模块功能固化到单芯片,也相当于定制一个专用控制芯片,其内部原理结构如图4所示。

图4 脉冲式速度控制模块内部结构简图

图4中复位单元的作用是负责整个速度控制模块的复位、清零和置位等工作。分频单元的作用是生成升速、恒速和降速段控制信号的脉冲频率。速度处理单元的作用是当分频单元传来脉冲频率(时钟)时,根据计数器的数值反馈分频控制信号至分频单元和最终输出信号至脉冲式伺服驱动单元。

频选信号计数器i的数值把分频控制信号f_ctr数值发送到分频单元,分频单元把与f_ctr数值对应的分频信号发送到速度处理单元作为时钟输入,速度处理单元在时钟的控制下,根据定时码计数器的数值输出速度控制信号。

运动方式为第1类别情况下,即“恒低速”运行时,计数器初始化并根据判断条件确定是否计数,在条件满足时计数器累加到总步长S,表示到达目的地。相应的部分硬件描述语言程序如下:

其中fo为运行频率,fs为有载起始频率,CNT1为计数器,S为总步长。第1行表述“恒低速”运行条件判断,条件满足后,第2行表述计数器值是否小于等于总步长,若计数器值等于总步长,则计数器清零,频选信号计数器值清零,如第5行、第6行所述,否则计数器值累加,如第9行表述。

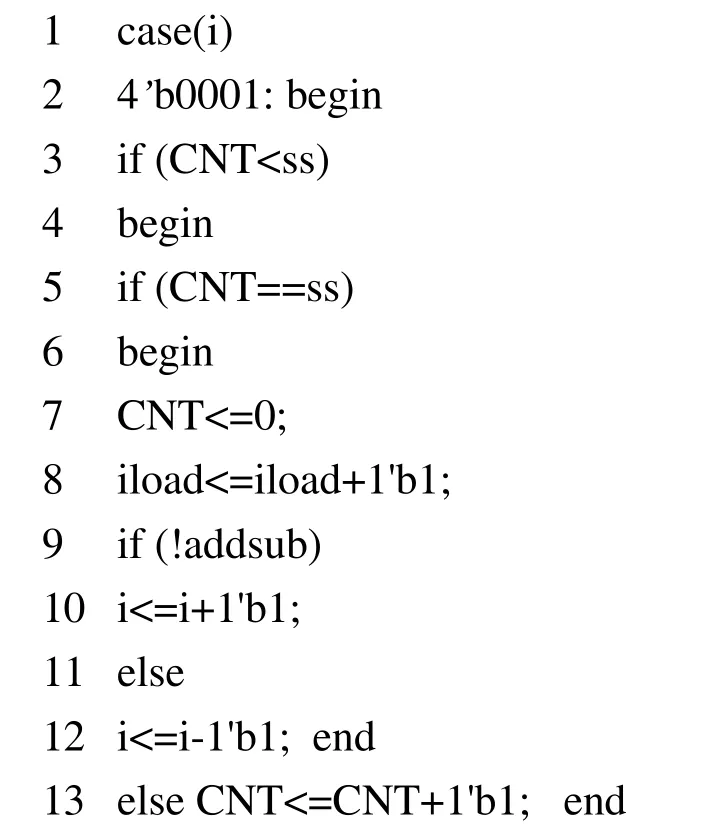

运动方式为第2类别情况时,速度处理单元在分频时钟的控制下,加减计数器对输入脉冲个数进行计数,计数值达到定时数值时,计数器i加1,f_ctr数值改变,速度处理单元分频时钟更新,加减计数器再次对输入脉冲个数进行计数,如此循环。当i计数到与Ss所对应的定时数值时,执行恒速阶段。恒速阶段完成以后,i进行累减运算进入降速阶段,处理过程与加速过程相反,直到i=1停止。使用case语句来处理频率选择后的过程,部分硬件描述语言程序如下:

其中CNT为计数器,ss为在Dt时间内频率对应的步长,addsub为计数器i值的增减信号,iload为计数器i值的增减控制信号,此段处理方法与第1类别运动方式相似。

所设计的复位单元采用了异步复位、同步释放的双缓冲电路,可以较好地解决同步复位资源消耗过多和异步复位的亚稳态问题,相应的复位单元内部电路原理结构如图5所示。

3 仿真验证与波形分析

本设计在Quartus II 9.0环境中采用Verilog HDL语言编写,应用于CYCLONE II 系列EP2C8Q208C8芯片。经过编译和综合,通过ModelSim SE软件仿真验证了设计的正确性。速度控制模块共消耗了457个LE(逻辑单元),71个寄存器,51个可用管脚。

图5 异步复位和同步释放电路

为了仿真时便于观察,模块时钟使用50MHz,分频单元将50MHz分频为100Hz、200Hz……900Hz、1kHz,设置 fs为 400Hz,Dt为 100ms。

在第1类别运行方式下,fs设置为200Hz,S1置为200,S置为100,其仿真结果波形如图6所示。

在第2类别运行方式下,fs设置为200Hz,S1置为200,S置为900,其仿真结果波形如图7所示。

在仿真结果波形图中,mclk为主时钟50MHz;clr为复位、清零和置位等信号,低电平有效;V为速度信号输出。

4 结束语

图6 第1类别运动方式仿真图

图7 第2类别运动方式仿真图

根据数控机床脉冲式速度控制的功能需求,利用Verilog HDL语言设计了基于FPGA的步进电动机升降速控制模块,并进行了仿真,验证了设计的正确性。本文的主要工作体现在根据步进电动机升降速软件实现流程提出了FPGA硬化实现的具体方法,提高了系统的运行速度,相对于早期硬件实现电路,减少了元器件数量,提高了系统的可靠性,增强了模块的可移植性和适用性。在仿真中出现的毛刺现象和定时间隔可调实现是以后进一步研究的内容。

[1] 汪木兰. 数控原理与系统[M]. 北京:机械工业出版社,2007.

[2] 庞淑娟,倪受东. 基于FPGA的步进电机速度控制器的设计[J]. 数字技术与机械加工工艺装备,2008(4):32-33.

[3] 黄勇,廖宇,高林. 基于单片机的步进电机运动控制系统设计[J]. 电子测量技术,2008(5):150-154.

[4] 杨国良,高瑞斌. 步进电机的加减速控制设计[C]. 第十四届中国小电机技术研讨会,2009.

[5] 李翠敏,高有行. 用寄存器实现步进电机速度控制[J].驱动控制,2005(5):14-16.

[6] 姚远,李辰. FPGA应用开发入门与典型实例[M]. 北京:人民邮电出版社,2010.

[7] 徐煜明. 步进电机速度控制的研究与实现[J]. 工矿自动化,2007(2):82-84.

[8] 王玉琳,王强. 步进电机的速度调节方法[J]. 电机与控制应用,2006(33):53-56.