基于FPGA的数字信号传输性能分析仪

2012-01-19姚佳毅林阅斌

孙 盼,姚佳毅,林阅斌

(山东大学信息科学与工程学院,山东济南 250000)

基于FPGA的数字信号传输性能分析仪

孙 盼,姚佳毅,林阅斌

(山东大学信息科学与工程学院,山东济南 250000)

文中分析的FPGA系统以数字电路为核心,由数字信号发生器、低通滤波器、加法器、伪随机信号发生器、数字信号分析电路组成。并通过对系统方案的对比,以及电路、软件的分析与设计,针对数据率误差、伪随机码误差、眼图和眼幅度均进行了实测,检测结果显示误差值均在允许范围内。

曼彻斯特码;数字锁相环;同步信号;眼图

1 系统方案

1.1 系统原理框图与方案描述

系统由数字信号发生器、低通滤波器、加法器、伪随机信号发生器和数字信号分析电路5部分组成,实现数字信号传输性能测试,同时由低通滤波器和伪随机发生器模拟传输信道。V1和 V1-clock是数字信号发生器产生的数字信号和相应的时钟信号;V2是经过滤波器滤波后的输出信号;V3是伪随机信号发生器产生的伪随机信号;V2a是V2信号与经过电容C的V3信号之和,作为数字信号分析电路的输入信号;V4和V4-syn是数字信号分析电路输出的信号和提取的同步信号。

图1 原理框图

1.2 方案论证与比较

(1)信号发生电路。

方案1 采用数字芯片构建数字信号发生器,伪随机信号发生器,采用FPGA实现数字信号分析。

方案2 采用纯FPGA硬件电路方式。即分别用3块FPGA硬件电路来实现数字信号发生器、伪随机信号发生器。

方案2硬件电路简单,利用了FPGA的强大性能,但容易降低传输性能指标。相比之下,方案1对该系统设计更加合理,且并未降低指标。应用纯硬件电路进行信息处理和模块控制,可有效提高设计效率和稳定性,故采用方案2。

(2)模拟电路。

方案1 采用电感与电容搭建无源滤波器。

方案2 采用运放NE5532搭建有源滤波器。

方案1电路简易但精度低。相比之下,方案2达到了最大10%误差精度,增益范围较大。因此采用方案2。

2 电路分析与设计

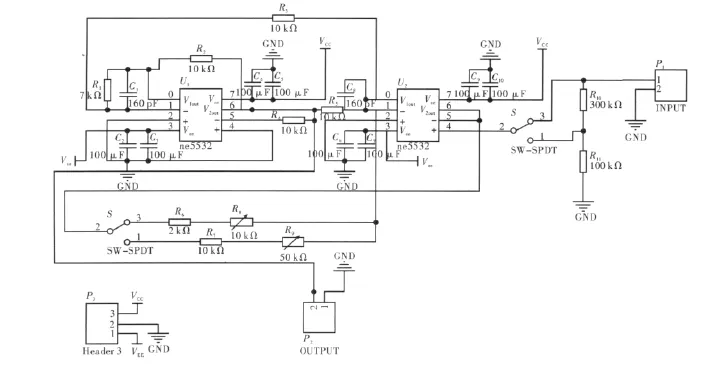

2.1 低通滤波器的设计

双二阶巴特沃兹有源滤波器:由两个积分器及一个单位增益反相放大器构成,运放采用NE5532。截止频率为100 kHz时,电容为159 pF,R1为7 kΩ,Q为0.707;截止频率为200 kHz时,电容为80 pF,R1为7 kΩ,Q为0.707;截止频率为500 kHz时,电容为31 pF,R1为7 kΩ,Q为0.707。增益分为衰减与放大两档,采用电位器实现增益可调,由NE5532搭建同相加法器抬高电平至FPGA输入信号范围。

图2 低通滤波器

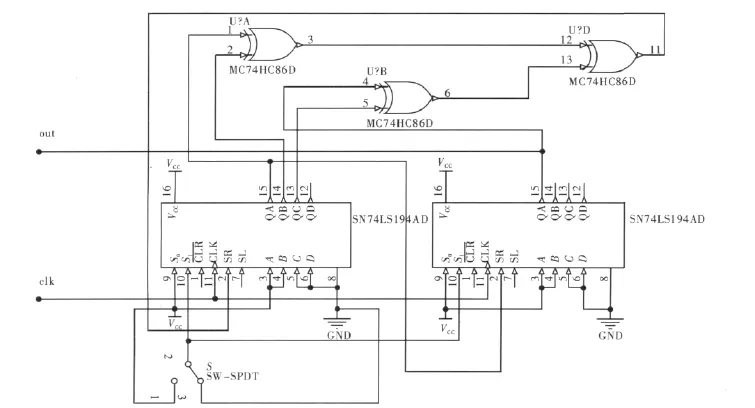

2.2 数字序列信号的产生

序列的产生需要完成以下几步操作:时钟信号的产生,移位寄存器反馈异或。

(1)时钟信号的产生。频率从10~100 kHz,步幅为10 kHz变化。首先是分频,以2 MHz晶振搭的振荡电路为原频率,采用分频芯片cd4017进行100分频得到20 kHz的脉冲,再通过T触发器得到占空比为50%的10 kHz频率。再将10 kHz的信号利用锁相环进行倍频,将锁相环的反馈电路接入一分频器,有如下关系:w0/N=w1,所以w0=N×w1,因此可实现对w1的倍频。其中分频器采用分频芯片cd4017与模拟开关cd4051搭成可实现10分频的分频器。至此得到了10~100 kHz步幅为10 kHz的10种频率的信号。

(2)由移位寄存器产生曼彻斯特序列。结合曼彻斯特编码原理及序列定义,采用移位寄存器74ls194和74hc86异或门结合搭成的带特定反馈的序列产生电路。

图3 序列产生电路

2.3 眼图显示方法

眼图指通过用示波器观察接收端的基带信号波形,从而估计和调整系统性能的一种方法。具体做法为:用一个模拟示波器跨接在抽样判决器的输入端,然后调整示波器水平扫描周期,使其与接收码元的周期同步。此时可从示波器显示的图形上,观察码间干扰和信道噪声等因素影响的情况,从而估计系统性能的优劣程度。在该设计中利用位同步时钟信号或从曼彻斯特码流中分离出的时钟信号作为模拟示波器的外触发输入,而信号作为普通信号在x轴或者y轴输入,利用模拟示波器的余辉效应可得到该信号的眼图。

3 软件分析与设计

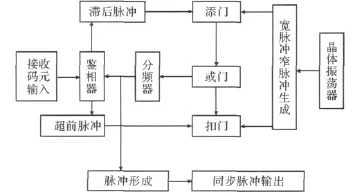

3.1 同步信号提取流程设计

信号发送端采用的编码是曼彻斯特编码,故通信系统采用自同步方法进行时钟和相位同步。该设计利用FPGA设计微分型数字锁相环实现位同步信号的提取。

图4 设计流程图

3.2 FPGA硬件模块设计

FPGA设计的数字锁相环由微分鉴相模块、双向高频时钟源模块、超前-滞后控制电路模块和分频器模块构成。其中鉴相器的功能是比较接收码元与分频器输出的本地时钟信号的相位,若本地时钟超前于接收码元的相位,鉴相器向扣门电路输出一个超前脉冲,若本地时钟滞后于接收码元的相频窄脉冲,整个数字锁相环路按上述方式,反复调整本地时钟相位,以实现位同步。

4 测试方法与结果

伪随机信号峰峰值范围100 mV~4.6 V。

4.1 数据率误差检测

10 kbit·s-1数据率标准下,实测10.001 0 kbit·s-1,误差 0.010%;30 kbit·s-1数据率标准下,实 测30.123 9 kbit·s-1,误差 0.401%;70 kbit·s-1数据率标准下,实测 69.450 0 kbit·s-1,误差 0.781% 。

4.2 伪随机码误差检测

检测方法:示波器探头直接跨接在数据率两端。结果:10 Mbit·s-1数据率标准下,测得 9.99 Mbit·s-1,误差达到0.1%。

4.3 眼图和眼幅度测试

检测方法:用示波器的同步输入通道接收码元的时钟信号,用另一个通道接在接受滤波器的输出端,因其与接受码元同步,所以在荧光屏上可以看到显示的眼图。改变噪声,观察眼图并且读数可得到当前噪声的眼幅度。码间串扰和噪声干扰越严重,眼皮越厚。

结果:输入噪声100 mV时,眼幅度3.6 V,眼皮厚度0.7 V;输入噪声250 mV时,眼幅度2.6 V,眼皮厚度1 V;输入噪声500 mV时,眼幅度2.3 V,眼皮厚度1.3 V;输入噪声1 000 mV时,眼幅度1.2 V,眼皮厚度2.4 V。

5 结束语

文中对FPGA系统进行了分析,并对系统原理框图与此次论证的方案进行了描述。同时,还针对低通滤波器的设计方法、数字序列信号的产生以及眼图显示的方法均作出了分析。随后对FPGA硬件模块设计和同步信号提取流程进行了设计。最终对数据率误差、伪随机码误差、眼图和眼幅度均进行了实测,检测结果令人满意。

[1]夏宇闻.Verilog数字系统设计教程[M].2版.北京:北京航空航天大学出版社,2008.

[2]樊昌信.通信原理[M].北京:国防工业出版社,2009.

[3]靖文,李斌,屈薇,等.一种快速位同步时钟提取方案及实现[J].电子设计应用,2007(12):82-85.

[4]严冬.基于VHDL语言的数字锁相环的设计与实现[J].中国科技论文在线,2007,2(6):52 -61.

[5]刘雁飞,吴进.基于CPLD的曼彻斯特编译码实现[J].西安邮电学院学报,2003(1):52-55.

[6]谢方乐,张红雨,文维.基于USB接口ID读卡器的设计[J].电子设计工程,2009(11):30 -32.

Analyzer of Transmission Performance for Digital Signals Based on FPGA

SUN Pan,YAO Jiayi,LIN Yuebin

(School of Information Science and Engineering,Shandong University,Jinan 250000,China)

The FPGA system analyzed in this paper has the digital circuit as its core.It is composed of the digital signal generator,low pass filter,adder,pseudo random signal generator and digital signal analysis circuit.The system scheme is compared and the circuit and software are analyzed and designed.To reduce the data rate error and pseudo random code error,eye and eye amplitude were measured.Test results show that error values are within the allowable range.

manchester code;digital phase-locked loop;synchronized clock signal;eye diagram

TN919.6+4

A

1007-7820(2012)08-032-03

2012-03-13

孙盼(1992—),男,本科。研究方向:通信技术。