基于FPGA与PCI总线的实时控制计算机的设计与实现

2011-10-09张磊

张磊

(中国兵器工业二〇六研究所 陕西 西安 710100)

外部器件互联总线即PCI总线,是Intel公司提出的将高速高带宽的外围功能移到靠近CPU的地方,并通过一个系统接口(主桥路)与处理器/存储器连接的“局部总线”解决方案[1]。随着集成技术突飞猛进地发展,如今工业、军事领域中使用的计算机正逐步向着微型化、超低功耗、超大规模集成的片上系统发展,越来越多的功能被集成到一个或数个芯片上,并能可靠地工作。新技术不仅使计算机的功能越发强大,同时功耗降低,体积缩小、在开发和调试中令开发者摆脱了底层繁冗的重复开发,缩短了开发周期,降低了开发成本。

文中在考虑到硬件产品的通用性,保证其功能和速度的前提下,兼顾体积、功耗、易用性,我们选用定制方式将计算机模块和大规模可编程器件FPGA作在一块印制板上。省去了大量的分立电路,降低了故障率,也使实控机的功能扩充更加容易。

1 系统总体介绍

实控机系统由计算机、FPGA及接口电路组成,只作为一块6U标准电路板。计算机模块本身拥有1个网口,2个USB2.0接口,8 个 RS422 串口(COM1~COM8),波特率可达 921.6 kbps,因此,我们可以分别使用COM3~COM8分别和各不需要高速通信的分系统模块进行通讯。本实控机的操作系统使用VxWorks操作系统,网口和主机连接用于调试和加载程序,板上使用2 G的电子盘作为操作系统及应用软件的存储设备。

通过计算机PCI总线扩充了一片大容量的FPGA,引到连接器的I/O线多达160根。在这片FPGA里,实现的主要功能模块有:I/O系统、定时系统、4个高速串口以及对自制定时信号的处理,其中I/O系统用于输出控制和状态输入,定时系统用于系统定时,4个8 Mbit/s同步串口分别于其他各分系统进行通讯。由于使用大容量FPGA,可完全满足一般系统对实控机的功能要求以及后续的功能扩充。

实控机板上有IDE接口用于连接外扩硬盘和光驱,PS/2接口用于连接键盘和鼠标,DB-15接口用于连接显示器,两个USB接口用于连接USB设备,一个备用的网口,以及复位键、电池等都放到面板上方便使用。系统原理图如图1所示。

图1 实控机系统原理图Fig.1 Principle scheme of RTC

2 实控机接口模块设计

目前开发PCI接口大体有两种方式,一是使用专用的PCI接口芯片,可以实现完整的PCI主控模块和目标模块接口功能,将复杂的PCI总线接口转换为相对简单的用户接口。用户只要设计转换后的总线接口即可,缩短了开发周期,缺点是用户可能只用到部分PCI接口功能,这样造成了一定的逻辑资源浪费,也缺乏灵活性,很可能增加板上的组件,导致产品成本的增加和可靠性的降低。二是使用可编程器件,采用FPGA的优点在于其灵活的可编程性,首先PCI接口可以依据插卡功能进行最优化,而不必实现所有的PCI功能,这样可以节约系统的逻辑资源[2]。而且,用户可以将PCI插卡上的其他用户逻辑与PCI接口逻辑集成在一个芯片上,实现紧凑的系统设计。当系统升级时,只需对可编程器件重新进行逻辑设计,而无需更新PCB版图[3]。

文中采用FPGA进行实控机接口模块的开发,实控机接口控制模块作为一个转换接口,工作于PCI总线与目标设备串口之间,完成两者间的数据传送。文中所选用的芯片是Xilinx公司的Virtex-5系列的5vlx30tff665,编写、仿真软件采用的Active-HDL,编译软件采用的是ISE 10.1 Service Pack 3,语言采用混合语言编程。

图2为实控机接口模块总体框图,分为用户应用模块(USER APP),多路选择器(MUX),串口模块(RS),控制寄存器(CTL_REG),中断共享(Int share)和定时器(TIMER)。 在USER APP中控制对PCI IP Core的调用,多路选择器用于选择读取哪一路串口的数据,控制寄存器用于控制各串口是否允许发送以及各定时器是否允许定时。文中将对PCI模块和串口模块的设计进行详细叙述。

图2 接口模块框图Fig.2 Interface module

2.1 PCI端的设计

2.1.1 IP Core的调用与配置

3.1 本次试验显示每隔6天输精一次受精率最高,间隔8天输精一次受精率最低。分析原因认为精子在母鸡体内一般存活6~7天,因此6天输精一次受精率较高。

Xilinx提供了大量的IP core供用户使用[4],例如pci32_V4.8就是32位的PCI Initiator/Target接口的LogiCORE IP product,共有3个基地址寄存器。文中调用的IP Core采用的是PCI Target模式,只调用第一个基地址寄存器:BAR_0。

PCI总线定义了3种物理地址空间,分别是存储地址空间,I/0地址空间和配置地址空间。配置空间是PCI所特有的一种空间,其目的在于提供一套适当的配置措施,使之满足现行的和可预见的系统配置机构。配置空间是一长度为256字节并且有特定记录结构的地址空间,可以在系统自举时访问,也可在其他时间访问。通过配置寄存器,配置软件可了解目标设备的存在、功能及配置要求:

1)厂商ID:此16位的只读寄存器定义了设备的生产厂商,文中使用Xilinx的默认ID值10EE;

2)设备ID:该值由生产厂商分配以识别其产品,文中设置为0050;

3)命令寄存器,此寄存器控制了设备响应PCI访问的能力,位0为I/O空间控制,位1为存储空间控制。文中采用I/O空间访问,因此我们在配置命令寄存器的时候需要在配置空间头标区04H处写入000 000 01,来实现I/O空间操作。

4)状态寄存器。状态寄存器用于记录 PCI总线有关事件的状态信息。该设备可以根据自己的功能来决定实现状态寄存器的那些位,不一定要实现所有的位。

图3 命令寄存器格式Fig.3 Command register state bits format

图4 状态寄存器格式Fig.4 Status register state bits format

5)基地址寄存器:加电软件在引导操作系统之前,必须要建立一个统一的地址映射,也就是说必须确定在系统中有多少存储器以及系统中的I/O控制器要求多少地址空间。当这些信息确定后,加电软件便把存储器和 I/O地址请求映射到合理的地址空间并引导系统。为了使这种映射能够作到与相应的设备无关,从而在配置空间的头标区中安排了一个供映射时使用的基址寄存器。基地址寄存器主要有两种作用:一个作用是存放存储器空间或 I/O空间基地址;另一个作用确定I/O或者存储器空间的长度。基地址寄存器根据存放于其中的数据来判断数据类型,位0为只读位,用来决定是存储器空间还是I/O空间,如果该位为0,则是映射到存储器空间;否则若为1,表示映射到 I/O空间,本文设置为1。

图5 配置访问Fig.5 Configuration accessing

文中利用I/O地址空间进行数据传输,因此需要在命令寄存器内写入01,图6为配置写操作,在地址04H写入000 000 01,之后,读出04H地址的数据进行验证,读出数值为?20?00 01,最低位为1,符合I/O地址空间传输要求。

图6 配置命令寄存器Fig.6 Config command register state bits

2.1.2 I/O传输控制

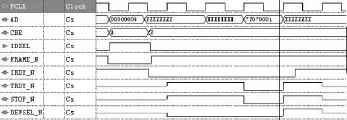

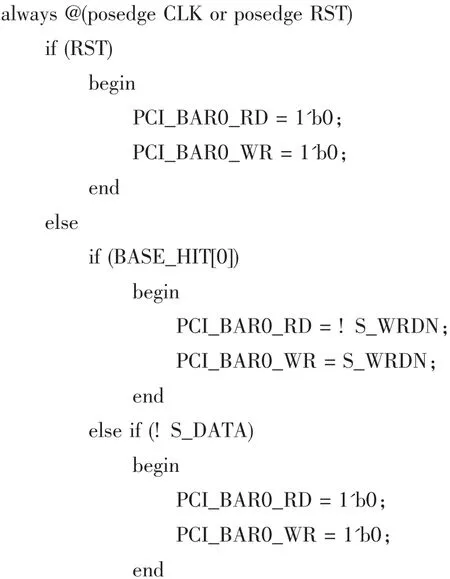

调用IP Core的文件完后,需要编写USER APP对IP Core进行控制。在文中将采用I/O地址空间进行数据传输,因此文中首先要对I/O地址空间数据传输进行译码操作,下列程序即是判断所使用的基地址寄存器和对BAR_0读写状态的译码:

在调用IP Core的时候只选择了BAR_0,所以BASE_HIT(0)=1;S_WRDN是IP核内部的一个输入信号,高电平代表写入,低电平代表读出;S_DATA是数据是否在传输的状态信号。

因为文中要连接4个串行接口,因此需要在USERAPP中加入一个多路选择器,对串口输入至PCI总线的数据进行选择,根据PCI总线上的地址判断与哪一个串口进行通信,读操作时,选择信号与PCI总线上的地址ADDR、基地址寄存器的读状态PCI_BAR0_RD以及数据传输状态S_DATA有关;写操作时,写使能信号必须在一个时钟周期内完成,因此它与PCI总线上的地址ADDR、基地址寄存器的写状态PCI_BAR0_WR以及数据传输状态有效位S_DATA_VLD有关。

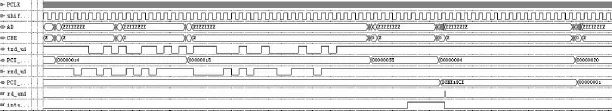

在图7中,CBE为2时,执行I/O读操作,此时PCI总线地址为4,生成串口三的片选rs3_cs信号,PCI总线上输出输入信号PCI_DATA_IN为452 247 72;CBE为3时,执行I/O写操作,此时PCI总线地址为1,生成串口一的写使能rs1_wr_en信号,PCI发送到串口一的数据PCI_DATA_OUT1为000 402 34。

2.2 串口模块的设计

图7 I/O读写操作Fig.7 I/O write and read operation

PCI数据是并行数据,通过FPGA发送到串口必须要转换成串行数据,因此我们需要在FPGA内产生一个移位寄存器和FIFO,实现串行数据同并行数据的相互转化。FIFO仍然使用Xilinx公司ISE中所提供的IP Core—fifo generator v4.4[5]。

首先调用FIFO IP Core并对其进行设置,文中对FIFO的读写时钟不同,因此时钟采用独立时钟模式,存储方式采用Block Ram模式;读方式采用First-Word Fall-Through;读写时的FIFO宽度均为32,深度1 025;不选择Almost Full和Almost Empty标志接口,不选择Prog_full和Prog_empty标志接口;不添加计数器接口;不选择握手。

根据串口数据规范,串口在无数据时始终保持高电平,数据的开始是以一个时钟的低电平开始,数据结束时至少为一个时钟的高电平,因此在设计移位寄存器时要注意这一点。由于收发数据的逻辑是不同的,因此串口模块根据数据的流向不同分为发送至串口模块和接收串口数据模块两部分。

接收串口模块是为实现接收串行输入数据并发送到PCI总线的功能,因此接收模块的移位寄存器是将串行数据转换成并行数据,在此模块中可以通过一些参数设置数据的长度和宽度,接收移位寄存器状态机图如图8所示。数据首先由串口写入,在移位寄存器中进行串—并转换,在接收完符合规定长度的串行信号后,移位寄存器发送一个时钟周期的写使能信号给FIFO,将转换后的数据写入FIFO,当FIFO接收到PCI总线发送的读使能信号后,由PCI总线读走FIFO内的数据。

图8 接收移位寄存器Fig.8 Receive shift register

发送串口模块是为实现将PCI总线输入的并行数据转换成串行数据后输出的功能,同样可以在此模块上通过参数设置数据的长度和宽度,发送移位寄存器状态机图如图9所示。PCI总线将数据写入FIFO,在发送允许信号有效的情况下,移位寄存器发送一个时钟周期的读使能信号将FIFO中的数据读出,进行并—串转换后输出数据。

在完成这部份工作的时候,需要注意几个问题,首先是时钟的问题,PCI总线传输的时钟是33 MHz,而串口的时钟是8 MHz。对于FIFO来说,当信号由总线流向串口时,FIFO以PCI总线时钟写入,串口时钟读出;反之则是以串口时钟写入,PCI总线时钟读出。其次是读、写使能信号的问题,对于FIFO来说,信号不同方向的传输造成读、写使能管脚的连接正好相反。当信号由PCI总线流向串口时,FIFO的写使能由PCI总线提供,即上文所说的rs_wr_en信号,宽度为一个PCI时钟周期,读使能信号由发送移位寄存器产生;反之,FIFO的写使能由串口提供,宽度为一个串口时钟,读使能信号由PCI总线提供。另外,发送移位寄存器上的发送使能接口send_n,作用是将移位操作完成后的串行信号发送到串口,send_n由终端的软件控制产生,通过PCI总线传至寄存器;接收移位寄存器上会输出一个中断信号,用于在长时间没有输入串口信号时产生中断,为了避免中断信号丢失,文中通过一个D触发器发出中断信号。

图9 发送移位寄存器Fig.9 Send shift register

2.3 综合设计

在分别完成PCI部分和串口部分的设计后,我们将两个部分合二为一。串口信号的PCI时钟和重置信号由PCI端提供,其中重置信号需要进行反转;读、写使能信号根据PCI端的解码后,发送给串口;发送信号Send的低4位分别连接到4个串口,用于驱动将FIFO里的信号发送至串口,高4位保留,用于扩展到其他需要控制的信号。综合设计仿真时序图如图10所示。

图10 综合设计时序图Fig.10 Sequential relationship diagram of integrative design

3 结 论

采用FPGA处理实时控制计算机PCI总线端口与各分系统的高速串口之间的通信,节约了元器件、以及电路布线,使电路更加紧凑、高效。在PCI总线接口的设计中,PCI总线接口的性能将会影响整个系统性能[6],本文运用Xilinx的IP Core技术,混合语言进行其它功能描述,采用 FPGA实现PCI总线接口不但性能可靠、稳定,而且提高了系统集成度。论文给出了系统的整体模块设计和各个子模块的设计,对系统各个模块的功能进行了严格仿真。整个系统设计可以应用于实际当中。

[1]李贵山,陈金鹏.PCI局部总线及其应用[M].西安:西安电子科技大学出版社,2003.

[2]Brueggen C,Pottinger H J.A novel FPGA-based master/slave PCI interface core,Circuits and Systems[C]//2000 Proceedings of the 43rd IEEE Midwest Symposium America:IEEE,2000.

[3]WANG Zhong-hai,YE Yi-zheng.Designing AHB/PCI Bridge[C]//ASIC 2001 Proceedings 4th International Conference.Beijing:IEEE Press:People’s Posts&Telecommunications Pub,2001.

[4]Xilinx.LogiCORETMIP Initiator/Target v4.8 for PCITMUser Guide[EB/OL].[2008-09-19].http://ching.xilinx.com/support/documentation/ip_documentation/pci_64_ug159.pdf,2008.

[5]Xilinx.LogiCORETMIP FIFO Generator v4.4 User Guide[EB/OL].[2008-09-19].http://www.digchip.com/application-notes/36143571.php,2008.

[6]William S.Operating systems-internals and design principles[M].Beijing:IEEE Press:People’s Posts&Telecommunications Pub,2011.