基于NIOSⅡ的大规模矩阵开关的研制与应用

2011-10-09朱彦青董振旗程绪建王翔宇

朱彦青,董振旗,程绪建,王翔宇,李 坤

(1.第二炮兵工程学院 陕西 西安 710025;2.西安微电子技术研究所 陕西 西安 710054)

片 上 可 编 程 系 统 (System On a Programmable Chip,SOPC)是一种灵活、高效的 SOC(System On a Chip)解决方案。它将处理器、存储器、I/O口等系统设计需要的功能模块集成到一个PLD上,构成一个可编程的片上系统[1-2],它具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件可编程的功能。NIOS处理器就是FPGA中嵌入的一个软核,它占芯片一部分逻辑单元。相比传统单片机有处理器速度快(可达上百M)、系统配置修改方便、可在一个FPGA中嵌入多个NIOS处理器等优点。NIOSⅡ是第二代用户可配置的通用32位RISC软核处理器。它采用哈佛结构,流水线技术、单指令流的可配置、可伸缩的软核处理器,具有32位指令集合16/32位数据通路。作为一种可配置的通用RISC处理器,它可以与用户自定义逻辑(user logic)结合构成SOC系统,并下载到Altera的可编程器件中去。当前,NIOSⅡ处理器已经在测量、控制、信号处理等领域广泛应用。

矩阵开关模块是自动测试系统(ATS)中不可缺少的组成部分,是ATS中信号传输与分配的中枢,是实现测试系统通用性的最关键部分。电源、信号源等测试激励信号通过矩阵开关切换到被测对象的任意输入端口,同时,将被测对象输出端口的信号自动切换到相应的测试仪器、仪表。借助开关系统的不同组态,可以充分利用自动测试系统(ATS)有限的测试资源,实现各种检测与激励信号的灵活路由[3-4]。因此,能够满足任意通道切换的开关模块的研制,就成为测试系统实现通用性的重要条件。

基于NIOSⅡ处理器的矩阵开关模块具有规模大、成本低、性能稳定等诸多优点,很好地解决了大型复杂系统结构复杂、体积庞大、I/O通道数不足等问题。

1 矩阵开关简介

矩阵开关是一个m路输入,n路输出的继电器阵列,在控制部分的控制之下,选择m路中的任意一路或多路测试信号,输出到n路中指定的测试通道上,主要功能为对指定信号进行转接[5]。

1.1 矩阵开关的特点

继电器矩阵开关具有动态范围大、通道阻抗低、通用性好、信号采集的精度高等优点,适用于电源通道和模拟信号通道。尤其对于不同时段需要采集不同路径的信号,可通过软件灵活设置信号路由,完成不同通道的数据采集工作,减少系统走线和复杂性,不必增加A/D通道数目,节约了测试资源。测试系统所采集的各种开关信号,如模拟信号、串行信号、数字信号、离散信号、功率信号、射频信号、高速数字信号等,都能经过继电器控制网络进行自动切换。

1.2 矩阵开关的设计原则

矩阵开关的主要作用是实现测试系统与被测对象的信号切换,使测试系统为被测对象提供工作环境,从而实现被测对象脱离系统情况下的测试。因此,对矩阵开关模块的性能要求是:1)矩阵开关应提供足够的切换通道,以满足系统的通用性要求,并为将来的功能扩展预留空间;2)矩阵开关行和列的数目应能够灵活配置,以满足不同被测对象的特殊需求;3)矩阵开关应反应迅捷、准确,工作可靠,同时应尽量减小 对 被 测 信 号 的干 扰[4,6]。

1.3 基于NIOSⅡ的大规模矩阵开关的结构

矩阵开关模块主要由接口及控制电路、驱动电路和继电器开关阵列组成,通过控制矩阵开关,将激励信号进行分类调整,自动切换到相应端口[4]。基于NIOSⅡ微处理器进行设计的4×100矩阵开关的原理框图如图1所示。

图1 矩阵开关模块的原理框图Fig.1 Elements schematic of matrix switch module

2 NIOSⅡ系统的设计

NIOSⅡ处理器在 Altera公司 Cyclone系列的EP1C6Q240C6 FPGA中嵌入实现。该芯片有5 980个逻辑单元,185个I/O管脚,92 916 bit RAM,2个锁相环。

Altera公司还为FPGA系统开发提供了专门的软件平台QuartusⅡ,为SOPC开发提供了专门的软件开发环境SOPC Builder。

2.1 定制NIOSⅡ处理器内核

在SOPC Builder环境中,在Avalon Components目录下调用 NiosⅡ Process-Altera Corporation,出现 Alteta NIOSⅡ配置向导,可方便的定制NIOSⅡ系统[1]。

本系统选用32位的NIOSⅡ/f型CPU,带2 k字节的数据缓存和2 k字节的地址缓存。为了方便调试,还为CPU加入了JTAG调试和在线软件断点调试模块,为了减少系统占用资源,选择最简单的Level1级JTAG模块,即不包含硬件断点调试、指令跟踪数据捕捉功能。

2.2 定制片内存储器

在片内为NIOSⅡ系统配置存储器,实现高性能应用的片内缓冲区,该存储器操作延迟固定,便于建立速率匹配的高速运行系统。本系统设计了一个2 kB片内ROM存储器(Onchip_ROM),用于存储程序代码以及程序运行空间;1 kB片内RAM存储器(Onchip_RAM)用于变量存储、stack等。

2.3 定制串口通信模块

在矩阵开关模块中,具有Avalon接口的通用异步接收器/发送器(UART核)在FPGA上的嵌入式系统和外设之间实现了一种串行字符流通信方式,它实现了RS-232协议,通过两个外部引脚TxD和RxD发送和接收串行数据。

2.4 定制I/O接口

本系统中,共定制了3个I/O接口,分别为:

IO:A、B、C、D作为 4-16译码器的 4个输入口;

IO1:D1-D8作为锁存器74273的8个输入口;

2.5 指定基础地址和中断请求优先级

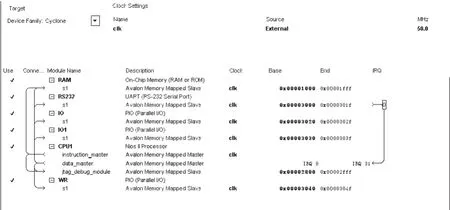

本系统所有的元件定制到系统后,NIOSⅡ处理器的配置图如图2所示。之后,要为外设分配基地址和中断请求优先级(IRQ)。由于对外设的寻址地址没有严格的要求,因此,采用SOPC Builder提供的Auto-Assign Base Address自动分配优先级[7-8]。

图2 NIOSⅡ系统组成的配置图Fig.2 Configuration diagram of NIOSⅡsystem

2.6 设置NiOSⅡ复位和异常地址

本系统设置系统上电以后,从内部的ROM开始运行,所以 Reset Address的 Memory Module设置为 Onchip_ROM,地址为Ox00001000。异常向量表放在外部RAM里面,所以Exception Address的 Memory Module设置为 Onchip_RAM,Offset地址为Ox00001020.

3 大规模矩阵开关的电路设计

3.1 接口及控制电路

接口及控制电路的设计采用FPGA设计,选用EP1C6Q240C6器件,主要包括初始化电路、锁存电路和NIOSⅡ微处理器。其中,初始化电路完成对接口的初始设定,判定系统是否通过自检,并在接到清除、结束、复位等命令后,系统返回初始状态。锁存电路用于寄存NIOSⅡ发出的控制指令,使矩阵开关可以同时进行多个通道的切换,由一个4-16译码器74154、13个或门 7432、13个 8位D型触发器 74273组成,其中译码器的每一个输出均与NIOSⅡ处理器的WR管脚作为每一个或门的两个输入,或门的输出作为触发器74273的时钟,锁存电路的时序仿真图如图3所示。

图3 锁存电路的时序仿真图Fig.3 Timing simulation diagram of latch circuit

3.2 驱动电路的设计

由于12 V继电器比5 V继电器具有更高的可靠性、更好的信号隔离度和稳定性能,因此在模块设计时,选择12 V继电器作为矩阵开关的切换控制继电器。由于接口电路送入的控制继电器工作的控制信号为TTL电平,因此需要驱动电路将TTL电平转化为12 V,以控制继电器实现信号的切换,在设计中,选择8通道的高电压、大电流达林顿晶体管阵列驱动器ULN2981A和ULN2803A,分别作为矩阵继电器的行和列提供驱动电压。ULN2981A和ULN2803A是TTL和大电流、高电压系统间的通用接口,其特点是:输入端具有嵌位二极管、输入兼容性强、开关速度快、维持功耗低。各自引脚排列如图4所示。

图4 ULN2981A和ULN2803A引脚排列图Fig.4 Pins pareto diagram of ULN2981A and ULN2803A

3.3 继电器阵列的设计

选用继电器时,要根据实际的技术要求、功能特性和环境适应性,参照继电器的性能参数,考虑负载特性、安装方式、体积大小等,合理准确地选择使用。根据实际需求选用合适的继电器是非常重要的,如果继电器的性能达不到要求,必然影响整个系统;而如果所选的继电器性能超过实际需求,必然会导致设计成本增加,因而也是不可取的[9]。

在实际使用继电器时需要一些特殊功能,例如延时、锁存。延时是指从发出驱动信号到触点动作有一个延时过程;锁存是指继电器能锁存驱动信号,即使驱动线圈的信号已撤消,但触点的状态仍然保持。在计算机控制系统中,延时功能可以通过相应的软件来实现,但锁存功能就很难通过软件实现,特别是当控制系统突然停电后,若要求继电器仍能保持原有的状态,就需要使用具有锁存功能的继电器[10]。

基于以上考虑,选用欧姆龙公司的具有保持锁存状态的G6HK-2型继电器搭建行列矩阵。

4 大规模矩阵开关在板级测试系统中的应用

板级测试系统是用于测试某大型复杂系统中计算机板卡的一套自动化测试系统[3]。由于板卡功能各异,数量、种类繁多,涵盖多种总线接口,要用一套系统实现对所用板卡的功能测试,对矩阵开关模块有很高的要求。

板级测试系统是基于模块化思想进行设计,测试资源高度集成在5块电路板上,分别是A/D板、D/A板、I/O板、MC/RDC板和串口通信板,为了使测试高效、准确,用5个4×100矩阵开关,分别与测试资源中的功能模块相连。测试过程中,用矩阵开关来实现多路数据分时采集,只需要通过软件设置继电器矩阵的工作模式可实现通道切换,针对不同板卡的测试需求搭建功能测试平台,可以实现对该大型复杂系统现存所有计算机板卡的测试。

5 结束语

NIOSⅡ嵌入式系统速度快、配置方便、便于扩展,简化了大规模系统设计中的复杂程度,基于NIOSⅡ的矩阵开关,在测试中运行高效,极大提高了测试系统的速度、精度和灵活性。

[1]周立功.SOPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2006.

[2]李兰英.NIOSⅡ嵌入式软核SOPC设计原理及应用 [M].北京:北京航空航天大学出版社,2006.

[3]朱彦青,程绪建,董振旗,等.多总线兼容的板级测试系统设计[J].电子设计工程,2011(14):64-66.

ZHU Yan-qing, CHENG Xu-jian, DONG Zhen-qi, et al.Design of board-level test system on multi-bus compatibility[J].Electronic Design Engineering, 2011(14):64-66.

[4]张洪刚,邢焕革,王德石.基于FPGA的大规模矩阵开关设计[J].鱼雷技术,2006,14(2):44-60.

ZHANG Hong-gang, XING Huan-ge, WANG De-shi.Design ofmassive switching matrix module based on field programmable gate array(FPGA)[J].Torpedo Technology,2006,14(2):44-60.

[5]彭荣木,崔少辉,陈胜,等.某型导弹测试系统的测试接口结构研究[J].兵工自动化,2008,27(6):23-24.

PENG Rong-mu, CUI Shao-hui, CHEN Sheng, et al.Research on test interface structure of certain missile test system[J].Ordnance Industry Automation, 2008, 27 (6):23-24.

[6]于劲松,李行善,徐波.自动测试系统中的信号开关设计[J].测控技术,2004,23(08):62-64.

YU Jin-song, LI Xing-shan, XU Bo.Design of signal switching in automatic test system[J].Measurement&Control Technology,2004,23(08):62-64.

[7]黄颖.动力调谐陀螺仪数字再平衡回路的设计与实现[D].哈尔滨:哈尔滨工程大学,2007.

[8]邹强.基于SOPC技术的智能同步开关研究[D].西安:西北工业大学,2007.

[9]柳颖.导弹电缆通断与绝缘电阻测试仪的研制[D].北京:中国石油大学,2010.

[10]杨江平,肖文杰.自动测试设备开关矩阵之研究[J].计算机测量与控制,2002,10(2):78-80.

YANG Jiang-ping,XIAO Wen-jie.A study of the switch matrix for automatic test equipment[J].Computer Measurement&Control, 2002,10(2):78-80.