载人航天空空通信子系统及其关键技术

2011-09-18石云墀

石云墀

(上海航天电子技术研究所,上海 201109)

0 引言

空空通信子系统是中国载人航天二期实现交会对接任务的关键子系统,完成运输飞船和目标飞行器间的数据通信。为提高系统的抗干扰和保密性能,空空通信子系统采用了DS-DBPSK直接序列扩频体制,该体制将原始数据与远高于其码速率的伪噪声序列模二加后生成新序列,其码速率与伪噪声序列相同,由此明显扩展了信号频谱。在接收端,将一个与发射端同步的本地伪噪声序列用接收信号相关,利用伪噪声序列的自相关特性,将信号能量集中在窄带范围内,提高接收信号的信噪比,获得处理增益。空空通信机是该子系统的核心单机,中频接收机是该单机的核心模块,其中数字化中频解扩解调是关键技术。为此,本文对空空通信子系统及其关键技术进行了研究。

1 系统构成

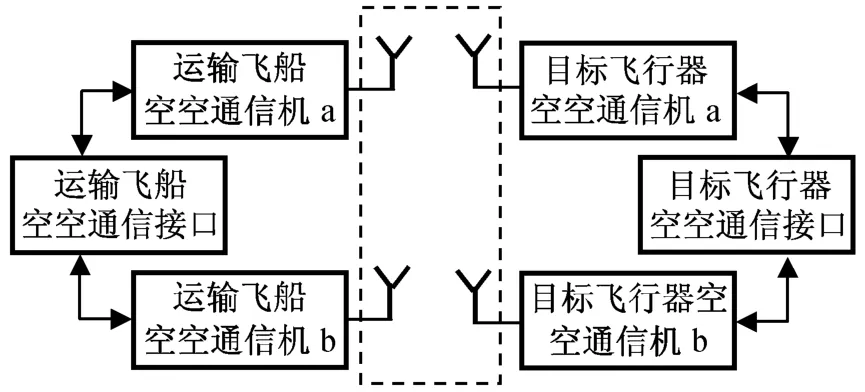

空空通信子系统由空空通信机4台(运输飞船、目标飞行器各2台)、空空通信天线4副(运输飞船、目标飞行器各2副)和空空通信接口2个(运输飞船、目标飞行器各1个)组成,如图1所示。其中4台空空通信机为该子系统的核心设备。

运输飞船空空通信机、目标飞行器空空通信机及其相连的空空通信天线组成2个独立的双工通信链路,两链路同时工作,收发频率完全相同,用不同扩频序列进行码分多址。为进一步抑制远近效应,两链路的空空通信天线采用不同圆极化方式进行旋向隔离。空空通信接口设备接收来自飞船或目标飞行器的数据,将其组帧后送空空通信机,同时接收空空通信机送出的接收数据,将数据还原后送飞船或目标飞行器上设备。

图1 空空通信子系统组成Fig.1 Composition of space to space communication subsystem

2 空空通信机

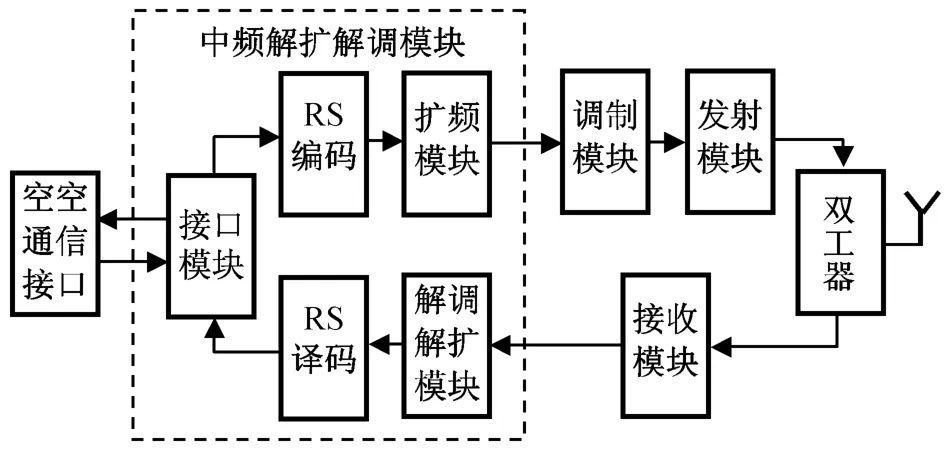

作为空空通信子系统的核心设备,其内部功能如图2所示。空空通信机接收空空接口送来的数据进行RS编码、扩频、调制、放大后经双工器后送天线发射,同时对天线接收到的信号进行放大、模拟下变频、解扩解调、RS解码后送空空通信接口。

图2 空空通信机组成Fig.2 Scheme of spaceto space communicator

发射通道的信号调制放大和接收通道的放大、下变频采用传统模拟方式实现。空空通信机的关键技术是中频信号的解扩解调,该功能由中频解扩解调模块实现。考虑运输飞船和目标飞行器空空通信机的码速率、扩频比不同,采用软件无线电方式实现中频信号的解扩解调,这样可用相同的硬件平台加载不同的软件实现不同的功能。

中频解扩解调模块主要指标式:中频载波频率70 MHz;载波最大多普勒频移13 k Hz;扩频体制DS/SS;扩频比1 023/127;调制方式DBPSK。

3 中频解扩解调关键技术

3.1 伪码的捕获与跟踪

直接扩频信号解扩的关键是保证本地PN序列和与接收信号同步。这样通过与本地PN序列进行相关运算,就能恢复原始数据。伪码的同步分捕捉和跟踪两个阶段:通过扩频码的捕获可使本地伪码与接收到的码元基本保持同步,获得一定的同步精度(如二分之一码元宽)。由于发射机和接收机的相对运动及时钟的不稳定,特别是解扩解调的需要,须进一步跟踪接收信号,使本地伪码尽可能跟随接收信号的变化,使同步精度控制在更小码元周期范围内,进一步降低数据误码率。

3.1.1 伪码捕获

伪码的同步捕获实质是对每个可能的相位点进行相关解调,根据解调结果判断相位是否同步的扫描过程,常用的PN序列捕获有匹配滤波器法、串行滑动相关捕捉法、多通道滑动相关捕捉法、辅助序列捕捉法等。比较各捕获算法的优缺点,选择了资源和捕获时间均适中的多通道滑动相关捕捉法。

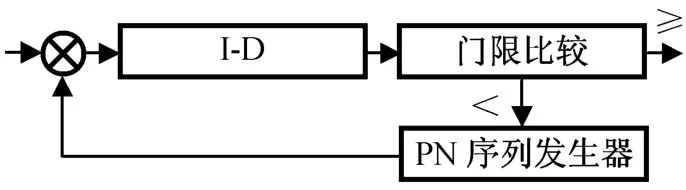

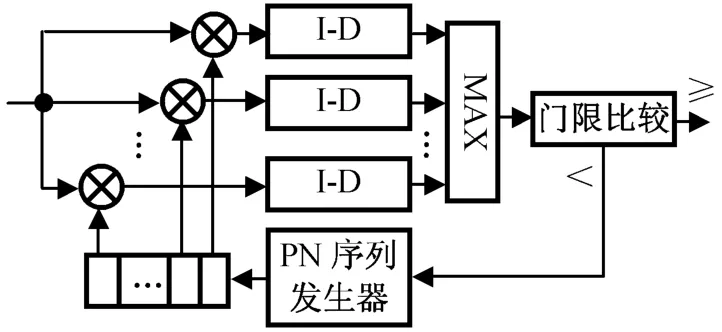

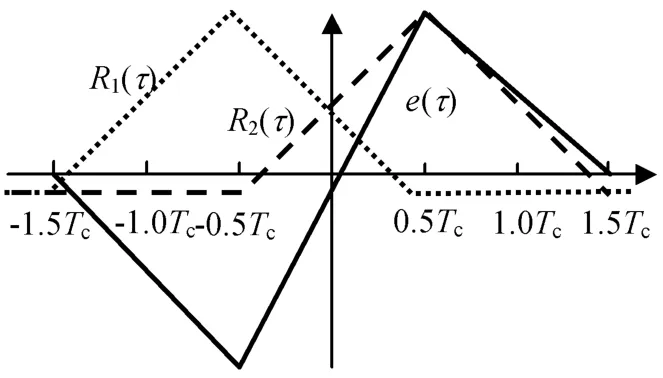

多通道滑动相关捕捉系统中有并行的N个滑动相关捕捉通道,输入每个通道的伪码相差一定的相位(如1/2码元)。其中每个滑动相关捕捉通道如图3所示,输入信号与本地产生的PN序列相乘后,在一个PN序列的周期内进行积分,利用PN序列的自相关特性,仅当本地PN序列与接收到的信号中的PN序列相差小于1个码元时,积分清洗滤波器(I-D)才会输出较大的相关峰。比较相关值与门限电平,当最大相关值大于门限时,就认为本地PN序列同接收信号达到了同步,进入跟踪状态;当最大相关值小于门限时,移动本地PN序列发生器产生的PN序列的相位(N/2个码元),重新进行相关运算直至同步。这样一个完整的伪码捕捉周期可完成N个相位的查询,捕捉时间变为单个串行滑动相关捕获法的1/N。所用硬件资源虽增加了N倍,但远小于全并行匹配滤波器所用资源。多通道滑动相关捕捉系统如图4所示。

图3 串行滑动相关捕捉系统Fig.3 Serial sliding correlater capture system

图4 多通道滑动相关捕捉系统Fig.4 Multi-channel sliding correlativecapturesystem

3.1.2 伪码跟踪

当接收到的信号与本地PN序列同步后,两者相位差小于1/2个码元周期。此时,系统进入跟踪状态,本地PN码相位须通过跟踪使其和输入PN码相对时间差减小为零。

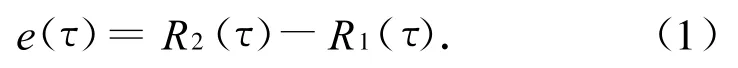

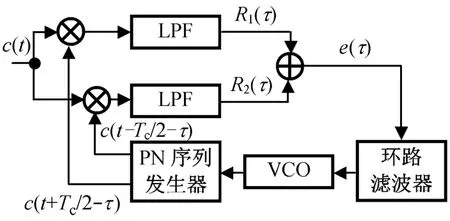

PN序列的跟踪采用延迟锁定环实现,延迟锁定环又称“全时间”(Full-time)超前-滞后跟踪环,其构成如图5所示。图中:自相关函数R1[τ(t)],R2[τ(t)]为低通滤波器输出,2个相关器输出之差用于产生误差信号

图5 延迟锁定环Fig.5 Delay lock roop

如图6所示,e(τ)被用作调整信号,用于驱动压控振荡器(VCO),VCO可用于调节PN码发生的时钟,当PN码发生器落后于输入序列相位时,则使时钟变快,反之,则使时钟变慢,由此实现跟踪相位。

图6 误差信号e(τ)和相关器输出R1(τ),R2(τ)Fig.6 Error signal e(τ)and relative output R1(τ),R2(τ)

采用数字技术实现延迟锁定环时,VCO由可编程的数控振荡器(NCO)替代。因每个伪码周期只能产生1个误差信号,为使误差信号导致的PN序列相位差不超过1个码宽度,NCO须有较高的精度和工作频率,而这会占用较多的硬件资源。实际使用中,可对DLL作适当简化:比较超前与滞后支路的相关结果,超前支路相关结果较大,则说明本地PN序列落后于接收到的信号,将本地PN序列的相位前移Δ(如1/2或1/4个码元);反之,将本地PN序列的相位朝后移Δ,实现相位跟踪。该方法在伪码发生器采用RAM结构实现时尤为简便,只需适当调整RAM的读取指针即可实现。

3.1.3 判决门限确定

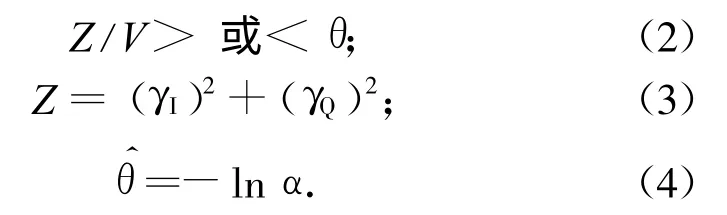

根据Bauyes和Neyman-Pearson假设检验,在AWGN下无衰落信号的非相关接收的最大似然估计方程可表示为

式中:V为噪声能量;γI,γQ为两路正交同相信号;α为无信号时的虚警率[1]。

瞬时接收到的信号功率和噪声功率为未知,且随时间而变。固定的门限捕获方案将使系统性能明显下降而无法正常工作。因此,有必要设置自适应门限检测。

因本地PN序列与接收信号未对齐时信号的相关值很小,而噪声与本地PN序列相关后能量基本不变,故可将未对齐时的相关值的平方作为噪声能量的估计。为提高噪声估计的准确性,将多个未对齐通道相关值的平方作平均处理。获得估计的噪声能量后,乘上一比例因子,即可作为自适应门限与相关器输出进行比较。

在弱信号时,未对齐通道相关值主要取决于噪声能量,仅基带信号主瓣的相关峰会超出门限;在强信号时,未对齐通道相关值更多由信号能量贡献,基带信号旁瓣的相关峰也会超过门限,导致误捕。为提高伪码捕获概率,可适当提高门限(加大比例因子),使旁瓣相关峰落于门限以下。

3.2 载波的捕获与跟踪

3.2.1 载波捕获

输入信号有较大的多普勒频移,而解扩后基带信号频谱主要集中在基带码速率2倍带宽内,信号带宽较窄,当本地载波与输入信号频偏较大时,相关峰将明显降低,即使伪码相位对齐,也可能无法检测到相关峰。因此,在相位捕获的同时,应对载波频率进行捕获。在扫描完一遍所有相位后修正载波频率,在下一个频点再次进行扫描。

另外,在检测到相关峰后,在伪码对齐条件下,再次对临近频段进行扫描,选取相关峰最大的频点。这样,利于载波环对载波的跟踪。

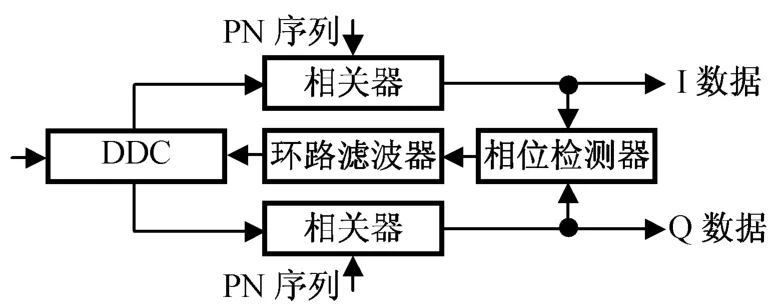

3.2.2 载波跟踪

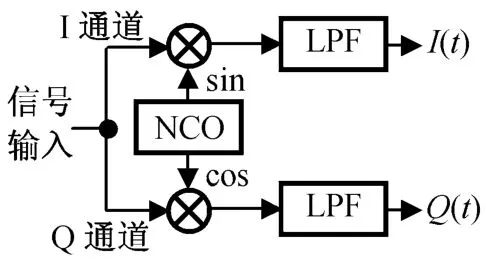

载波捕获后,需对载波进行跟踪,使本地载波与输入信号频率相位保持一致,以进行相干解调。载波跟踪环采用数字Costas环,由数字下变频器(DDC)、解扩单元、数字鉴相器和环路数字滤波器等组成,如图7所示。其中:DDC是中频数字解调的重要组成,它包括数字混频器、NCO和数字低通滤波器等三部分。其工作原理是:将输入信号与一本地振荡信号作乘法运算,乘法器输出送低通滤波器以滤除高频分量,获得基带数据。同相一个正交(I-Q)分解DDC的结构如图8所示。

图7 数字Costas环组成结构Fig.7 Structure of digital Costas loop

图8 正交分解DDC结构Fig.8 Structureof orthogonal decomposition DDC

数字鉴相器根据I,Q两路相关结果,由反正切运算获得本地载波与输入信号的相位误差,并去除数据调制引起的180°相位翻转。环路滤波器对相位误差进行低通滤波,滤波结果控制NCO的输出频率,实现对输入信号载波的闭环跟踪。

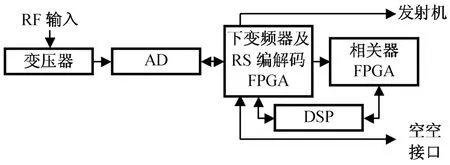

4 中频解扩解调模块实现

受器件规模与等级限制,中频解扩解调模块采用了现场可编程逻辑阵列(FPGA)+数字信号处理器(DSP)架构。中频解扩解调模块由变压器、AD、下变频及RS编解码FPGA、相关器FPGA,以及DSP组成(如图9所示),可实现自中频(70 MHz)起的下变频、相关捕获、解扩、解调、RS解码的接收功能和发射前的组帧RS编码功能。图中:变压器由一个4∶1阻抗变换器及周围器件构成,作用是抑制共模噪声和隔离模拟数字地,并进行阻抗匹配;AD对输入中频信号进行采样,采样频率为伪码速率的4倍。选用AD公司的AD6645高速14位并行AD,输入带宽200 MHz,其最高采样率可达80 MS/s,实际使用了高8位数据。

图9 中频解扩解调模块组成Fig.9 Module composition of middle frequency demodulation of DS/SSsignal

4.1 数字下变频及RS编解码FPGA

下变频及RS编解码FPGA为一片30万门的XQVR300,其作用是:在捕获前消除采样后的残余频差,为其后的相关运算消除频差的影响;捕获完成后,作为载波锁相环的一部分对载波的频率和相位进行跟踪;完成与DSP及空空通信接口设备的信号交换和RS编解码,其内部功能如图10所示。AD采样值分别同NCO输出的相位相差90°的正弦信号和余弦信号相乘,再通过FIR滤波器滤除高频分量,即可得两路正交的基带信号。I/Q两路FIR滤波器的参数完全相同,在低通滤波的同时完成数据抽取。DSP接口1完成下变频FPGA与DSP的接口时序,使DSP能控制NCO的输出频率。

同时,该FPGA接收来自空空通信接口的数据,将其组成传输帧,进行RS编码后,与本地PN序列异或进行直接序列扩频,将扩频后的信号送发射机。该FPGA还接收DSP送来的解扩数据帧,在RS解码后,选出有用数据送空空通信接口。

4.2 相关器FPGA

图10 数字下变频FPGA功能Fig.10 FPGA function of digital down conversion

并行相关FPGA选用一30万门的XQVR300,其作用是生成本地伪码序列并与基带信号相关,将相关结果送DSP,并为DSP提供看门狗和译码逻辑,功能如图11所示。图中:GOLD序列发生器产生本地伪码,并通过移位寄存器产生相位相差1/2或1/4码元的多个伪码供相关器使用,同时还能根据DSP的控制信号调整自身相位;积分清洗滤波器根据输入的伪码序列,每个伪码周期进行1次相关运算,将相关结果送往DSP。考虑资源使用和捕获时间要求,I/O路并行捕获通道各24个。DSP接口将相关结果送DSP,并提供中断、接收DSP控制指令调制GOLD序列相位。看门狗逻辑提供DSP复位信号,译码逻辑为外设提供地址译码。

图11 相关器FPGA组成Fig.11 FPGA composition of correlater

4.3 解扩解调DSP

DSP采用SMJ320VC5416芯片,工作时钟最高可达100 MHz/s,运算能力满足任务需求;内部自带64 k B程序与数据RAM,节省了外围电路开销。该DSP主要完成判决门限计算、伪码/载波的捕获、伪码/载波的跟踪,以及接收帧结构的判决等功能。两个阶段的工作模式为:

a)捕获阶段 每次相关运算结束后,读取各路相关器的相关值,计算每个相位I,Q路相关值的平方和,取最小的21路的平均值,乘以一参数因子作为判决门限。比较平方和的最大值与判决门限,若超门限,则认为捕获伪码,反之,在下一组相位进行捕获。当全部相位均试探过后,DSP控制下变频FPGA中的NCO频率变化一定值,在下一频率点试探。

b)跟踪阶段 DSP通过读取I/Q相关结果,计算本地载波和接收的相差与频差,经环路滤波后调整NCO频率字,实现载波跟踪;读取超前和滞后相关通道的相关值,根据结果调整伪码相位,实现伪码跟踪,并判决出接收数据的帧结构,提取有效数据送外部RS解码器解码。

根据上述方案设计硬件并编写相关软件,实现了中频解扩解调功能,整机实现的主要性能指标为:捕获带宽±16 k Hz/±30 k Hz;接收机灵敏度-123~-113 d Bm;接收机误码率1×10-6;捕获时间平均不超过3 s,最大不超过5 s。

5 结束语

采用直接序列扩频通信体制的空空通信子系统是载人航天二期交会对接任务的关键子系统。作为该系统核心单机,空空通信机采用软件无线电方式实现了伪码/载波的捕获和跟踪,具有结构灵活、通用性好的特点。

[1]A J维特比.CDMA扩频通信原理[M].李世鹤,等(译).北京:人民邮电出版社,1997.