基于信号完整性的高速数据采集存储器PCB设计与仿真

2011-08-07王乐裴东兴崔春生

王乐,裴东兴,崔春生

(中北大学 仪器科学与动态测试教育部重点实验室,电子测试技术重点实验室,山西 太原 030051)

0 引言

近年来,随着集成IC工艺突飞猛进的发展,电路的工作频率越来越高。高性能的电子设计体积的减小导致电路的布局布线密度变大,集成电路输出开关速度提高,而同时信号的工作频率还在不断提高,在高速PCB的设计过程中,面临的主要问题有3个:电磁兼容、电源完整性和信号完整性。当系统工作的时钟频率过高时,将出现传输线效应和信号完整性问题,本课题研究的高速采集电路的时钟每个通道分别为50MHz,所以要在满足电路功能设计的基础上,需要对电路进行布线前后的信号完整性分析。

本文对一个高速数据采集存储器进行了PCB设计,为了保证该存储器的各个模块能够有效的运行,本文采用HyperLynx软件对PCB进行了信号完整性仿真分析。信号完整性分析分为布线前信号完整性分析和布线后信号完整性分析,前者为PCB布线提供布线准则,后者用来检验完成后的PCB能否达到预期的效果。

1 高速数据采集存储系统关键模块选型

在本系统中,硬件电路由两块电路板制作而成,一块是自制ADC采集模块,另一块是FPGA开发板。

中心控制器件:Altera公司的Cyclone Ⅲ系列的FPGA。

ADC芯片:AD9288,采用差分信号作为其输入信号。

片外高速存储器:Zentel公司的SDRAM,型号为A3V64S40ETP,存储容量为64M bit,采用业界通用的SDRAM控制器来实现对片外DRAM的控制。

时钟模块:50MHz晶振。

电源模块:要求提供3.3V、2.5V、1.2V的电压。

2 布线前信号完整性分析

高速系统的设计中存在的信号完整性(信号质量)问题主要有反射、串扰以及传输线效应等。本文应用信号完整性分析软件HyperLynx中的LineSim对本系统的阻抗匹配与端接技术以及串扰进行仿真分析。仿真条件设置为:传输线为顶层微带传输线;特征阻抗 Z0= 8 3 . 5 Ω ;线宽W=6mils ; 线长 L = 2 i n c h e s ;PCB叠层设置为6层,从上到下依次为:顶层信号层、电源层、中间信号1层、中间信号2层、地平面层、底层信号层,电介质常数为4.3。LineSim原理图中驱动端与接收端均采用IBIS模型中的CMOS3.3V模型,驱动端由100MHz信号驱动,占空比为50%。

⑴ 阻抗匹配与端接技术仿真分析

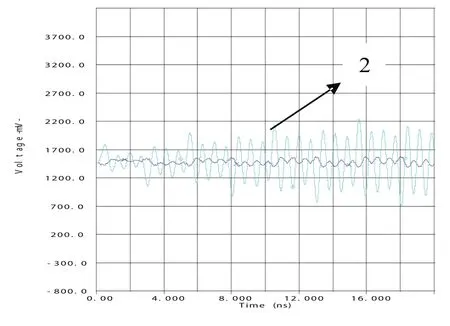

阻抗匹配与端接技术主要有:串行端接、简单并行端接、戴维宁并行端接、主动并行端接、并行AC端接。未使用端接的仿真结果如图1所示。串行端接的仿真结果如图2所示。

图1 未端接模型及仿真结果

图2 串行端接模型及仿真结果

如图1、2中所示1为驱动端波形的标号,2为输出端波形的标号。经过本系统对各种端接技术的仿真比较发现,串行端接在减缓上冲、下冲、振铃等现象的效果比较好,故在本系统中的传输线需要端接时均采用串行端接技术。

⑵ 串扰仿真分析

串扰分析两线走线网络,参数设置为:两线线宽W=6mils。分别改变平行走线长度L和两线间距P对其仿真,仿真结果如图3~9。

图3 L=2inchs,P=8mils,W=6mils

图4 L=2inchs,P=18mils,W=6mils

图5 L=2inchs,P=18mils,W=6mils

图6 L=1inchs,P=18mils,W=6mils

图8 干扰源频率为50MHz

图9 干扰源频率为200MHz

通过对不同条件下的串扰仿真,如图3~9,得出以下结论:串扰随着信号走线间距的增大而减小;串扰随着平行走线长度的增大而增大;串扰随着干扰源信号频率的增加而增加。平行走线L小于1inch,走线宽度W为6mils,平行走线间距P为18mils。

3 原理图中的信号完整性设计规则

设计原理图时主要解决地弹效应和反射带来的影响。

地弹效应处理:处理地弹效应的主要方法是使用去耦电容。规则是IC的每一个电源引脚接一个0.01~0.1µF的电容,对于功率较大的IC,另外还要有一个10~100 µF的电解电容或钽电容。

反射处理:对于高速信号线(被视为传输线)必须要进行阻抗匹配。由于印制电路板PCB上器件和信号线的密度较大,采取源端端接处理。本系统中具体的匹配电阻选择:输入AD8138的差分信号与AD8138之间分别选用500Ω和523Ω电阻匹配, AD8138输出到AD9288选用50Ω电阻匹配。

在高速数据采集系统中,差分布线技术大量用于时钟信号和数据信号中。差分传输技术较单端传输技术有显著的优点,如:电压波动范围小、不易受到串扰的影响、降低电磁干扰、消耗功率少等。用差分信号进行布线时,要遵守一些特定的规则:差分线对之间的长度差值必须控制在信号上升沿时间的电气长度的20%以内;差分信号在走线时,要求在同一个布线层内背靠背布线;当差分信号需要切换布线层时,要求两条信号线在相同的地方通过过孔切换到另一个布线层;差分信号线要尽量靠近,一般要求线间距为一倍的线宽;为防止差分信号对邻近信号线的干扰,要求差分信号与邻近信号线的间距大于3倍线宽。

4 高速数据采集模块PCB版图

通过以上对系统布线的详细阐述,按照设计要求结合端接及串扰仿真得出的结论,布线后完成的采集模块PCB版图如图10所示。

图10 布线后PCB版图

5 仿真结果

该高速数据采集系统PCB设计完成后,利用HyperLynx软件对其中的差分输入时钟网络、数据通道进行信号完整性仿真分析。图11和图12为对AD9288的差分输入时钟进行信号完整性仿真。图13为对AD9288输出到FPGA的数据进行信号完整性仿真。

图11 差分时钟网络信号完整性仿真

图12 差分时钟(CLK+/CLK-)输出波形仿真图

图13 AD数据通道输出波形仿真

6 结论

从图11中看出,差分输入时钟信号边缘较光滑、无明显过冲、下冲、振铃现象。从图12可以看出,在50MHz的高频情况下,差分时钟经过传输到达AD9288的波形是符合实际要求的。从图13中可以反映出AD数据通道输出信号无明显的过冲、下冲、振铃现象,信号质量较好,波形符合实际要求。故对关键网路的仿真表明PCB布线基本符合信号完整性要求。

[1]田广锟,范如东.高速电路PCB设计与EMC技术分析[M].北京:电子工业出版社,2008.

[2]夏金军.应用FPGA的高速数据采集的设计与实现.[D].西安:西安电子科技大学,2008.

[3]张海风.HyperLynx仿真与PCB设计[M].北京:机械工业出版社,2005.

[4]吴聪达.高速数字设计中的信号完整性研究[D].西安:西安电子科技大学,2005.

[5]杨洪军.信号完整性分析及其在高速PCB设计中的应用[D].成都:电子科技大学,2006.

[6]靖军红,谢君红,田杰荣,胡瑞卿.数字射频存储仿真研究[J].电子测试,2009(2):9-14.

[7]刘伟,康凯,钟子发.高速数字设计中的反射分析[J].电子测试,2010(8):26-31.

[8]高剑.存储器并行测试方法[J].电子测试,2009(2):47-49.