基于AMBA APB总线NandFlash控制器的设计研究

2011-07-13刘卫东

王 洋 , 刘卫东 ,, 于 岗

(1.中国海洋大学 信息科学与工程学院,山东 青岛 266100;2.海信电器股份有限公司 山东 青岛 266071)

随着SOC技术的发展,集成SOC的整机系统规模越来越大,功能越来越强大。在这些整机系统中,NandFlash得到了广泛的应用。为了支持NandFlash通信,在SOC中必须设计NandFlash控制器接口。

笔者设计的NandFlash控制器支持AMBA APB接口和数据校验、纠错功能。经Modelsim仿真和FPGA验证表明,本设计完全满足NandFlash的时序和通信功能要求。

1 NandFlash简介

Flash内存主要有 NandFlash和NorFlash两种,NorFlash技术由Intel公司1988年首先推出,NorFlash特点是工作电压低、随机读取快、功耗低、稳定性高;1989年,东芝公司发表了NandFlash结构。其强调降低每比特的成本和更高的性能。NandFlash存储器具有容量较大、改写速度快等优点,适用于大量数据的存储,因而在嵌入式产品中得到了广泛的应用,如数码相机、MP3随身听记忆卡、体积小巧的U盘等。

2 NandFlash控制器的设计

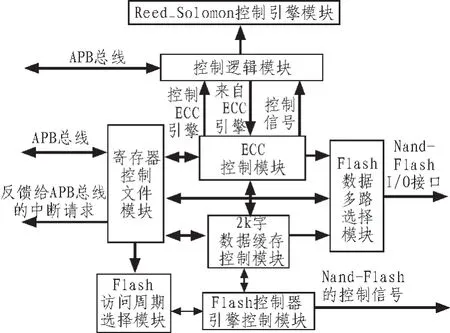

图1 NandFlash控制器整体框架Fig.1 Entire architecture of NandFlash controller

2.1 NandFlash控制器整体框架

NandFlash控制器的整体框架[1-3]如图1所示。其主要模块有:寄存器控制文件模块、Flash访问周期选择模块、Flash控制器引擎控制模块、2 k字数据缓存控制模块、ECC控制模块、逻辑控制模块、Reed-Solomon控制引擎模块、Flash数据多路选择模块。

NandFlash控制器的读写擦除的操作都是来自AMBA APB总线的请求,本控制器的主要功能是把来自于AMBA APB总线的请求转化为符合NandFlash时序要求的控制信号。该控制器适用于从64 M bits到32 G bits的所有类型的NandFlash。

2.2 NandFlash控制器的具体模块功能

2.2.1 寄存器控制文件模块

寄存器控制文件模块是面向AMBA APB总线的接口设计的,所有被AMBA APB总线访问的控制寄存器都是通过本模块进行配置的。其主要的作用是通过AMBA APB总线配置本设计的寄存器。

2.2.2 Flash访问周期选择模块

本模块主要作用是为NandFlash读写产生一个适当的访问时钟周期,本模块主要实现了一个可编程的(3~10个系统时钟)分频器,也就是说可以通过寄存器控制文件模块配置寄存器,实现3~10倍的分频,从而产生适合Flash访问的时钟周期。

2.2.3 Flash控制器引擎控制模块

Flash控制器引擎控制模块是整个控制器非常重要的部分。它把APB总线的请求转换成NandFlash设备的访问时序,如命令锁存周期、地址锁存周期、数据读/写周期、数据擦除周期等,从而实现控制NandFlash设备的目的。

由于NandFlash的控制指令比较多,为了能够灵活控制各款NandFlash芯片,本模块采用了状态机[4]的设计。本模块的状态机主要分为7个状态:空闲状态、写命令状态、写地址状态、写数据状态、等待状态、Flash忙状态、读Flash状态。状态之间的转换如图2所示。

图2 NandFlash的状态转换Fig.2 State transition of NandFlash

在空闲状态时,当开始启动NandFlash进入写命令状态,其他条件下保持在空闲状态。

在写命令状态时,当cpu重启时返回到空闲状态;当要进行块擦除或者读Flash的状态时进入等待状态,其他条件下进入写地址状态。

在写地址状态时,当一直保持写状态时保持此状态;当写完地址需要写数据时进入写数据状态;当要进行块擦除时回到写命令状态。

在写数据状态时,当一直保持写数据状态时保持此状态,其他条件下回到写命令状态。

在等待状态时,当一直保持等待状态时保持此状态;当读Flash的状态或读NandFlash的ID号时进入读Flash状态,其他条件下进入Flash忙的状态。

在Flash忙的状态时,当超出Flash忙的最大时间并且cpu重新开始读时回到空闲状态;当超出Flash忙的最大时间并且读Flash的状态时进入写命令状态;当没有超出Flash忙的最大时间并且Flash忙信号有效时则保持在此状态;当没有超出Flash忙的最大时间并且以上条件都不成立则进入读Flash状态。

2.2.4 2 k字数据缓存控制模块

2 k字数据缓存控制模块内部是单端口同步的SRAM(静态随机存储器),它主要的作用是为NandFlash读/写操作一页的数据缓存。由于数据缓存被AMBA APB总线和NandFlash控制器访问,所以设计了2 k字数据缓存控制模块控制所有的AMBA APB总线接口和NandFlash控制器。2 k字数据缓存的具体分配如图3所示。

图3 2 k字数据缓存分配Fig.3 2 k word data buffer allocation

2.2.5 ECC控制模块

ECC控制模块在其内部提供了一种ECC(错误检查和纠错技术)的算法,还为Reed-solomon控制引擎模块提供接口,所以NandFlash根据Flash的要求选择不同的错误检查和纠错的算法。

由于NandFlash所采用的工艺导致位翻转的现象比较多,但是它的出错一般不会造成整块或者整页不能读取或者全部出错,而是整个页中的一位或者几位出错,因此在NandFlash处理中使用ECC算法纠正单比特错误、检测双比特错误。

当ECC控制模块使能后,ECC控制模块开始接收数据并且进行计算,ECC控制模块会根据写入的数据判断此时为数据区域或备份区域(spare area)。当为写操作时并且判断为备份区域时,ECC控制模块发送FIFO的写数据使能,将ECC的结果写入备份区;当为读操作时,ECC会根据备份区读出的ECC结果和计算的ECC结果相比较,定位错误的具体位置,写入寄存器提供查找。

2.2.6 逻辑控制模块

逻辑控制模块的主要作用是控制ECC控制模块和Reed-Solomon控制引擎模块,以及从AMBA APB总线配置的控制信号。

2.2.7 Reed-Solomon控制引擎模块

Reed-Solomon控制引擎模块[5]可以实现4纠错和8纠错功能。在其内部有两个控制引擎分别是每503字节可以纠错4字节,另一个为每495字节可以纠错8字节,这两个控制引擎能够同时工作互不干扰。

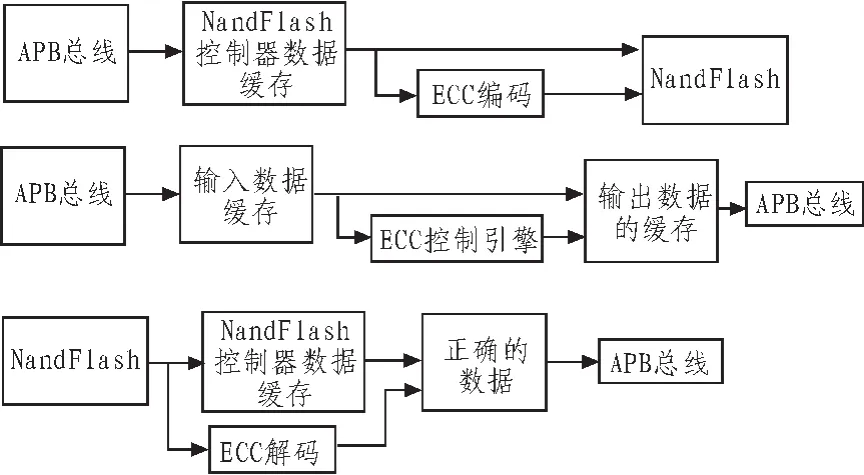

2.3 NandFlash控制器内部的数据通路

NandFlash控制器内部的数据通路主要分为3种:APB总线-NandFlash设备、NandFlash设备-APB总线、APB总线-APB总线。

图4 3种数据通路Fig.4 The flow direction of internal data

APB总线-NandFlash设备的数据通路:APB总线来的数据进入NandFlash控制器内部的数据缓存经过ECC编码输到NandFlash设备。

NandFlash设备-APB总线的数据通路:从NandFlash来的数据进入NandFlash控制器内部的数据缓存经过ECC解码校验得到正确的数据输入到APB总线的数据。

APB总线-APB总线的数据通路:APB总线来的数据进入输入数据的缓存区经过ECC控制引擎输出到输出数据的缓存区将其输入到APB总线。

3 验证结果

为了实现ModelSim对NandFlash控制器的功能级仿真,搭建了一个行为级系统模型。将NandFlash设备的行为级模型与NandFlash控制器进行连接,编写了一个行为描述的任务 (task)apb_write_fsc,它的主要作用是模拟了APB桥(APB主机)向APB总线发送数据,通过APB总线配置NandFlash控制器的寄存器,实现控制NandFlash设备。

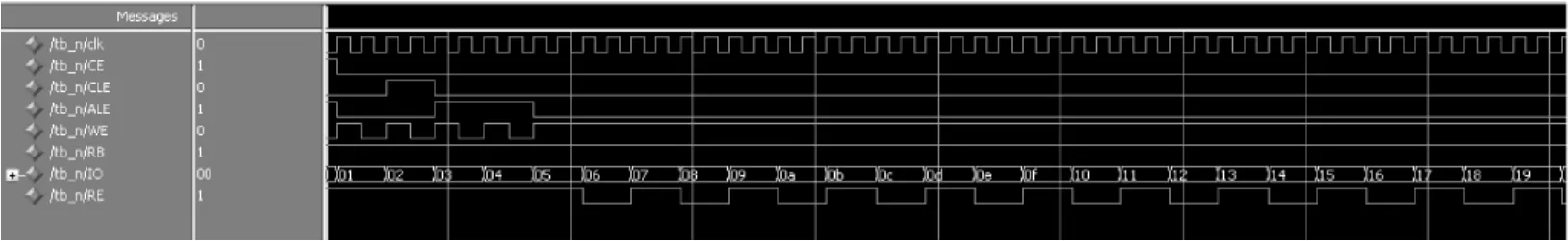

NandFlash读一页为例,仿真的结果如图5所示。

图5 NandFlash读一页的数据时序Fig.5 NandFlash timing of reading one Page

图5为NandFlash读一页的数据的时序图[6],可以看到当CE为低电平时芯片启动,CLE为指令锁存使能信号,当CLE为高电平时并且当WE上升沿时将发出数据线IO上指令01H,表示要读一页的数据,ALE为地址锁存使能信号,当其为高电平时并且当WE上升沿时将读数据的地址发出,表示要读的地址,这里写地址用了3个时钟周期。当RE为下降沿时将这一页的数据读出即IO端口。从上图的时序可知和NandFlash标准的时序图相一致。

4 结束语

文中设计的基于AMBAAPB总线的高速大容量NandFlash控制器,实现了将AMBA APB总线请求转化为NandFlash存储器的时序请求,在通信过程中能进行数据校验和纠错,能够对NandFlash设备进行读写和擦除等基本操作。验证表明,设计完全满足系统要求。

[1]杨宗凯.数字专用集成电路的设计与验证[M].北京:电子工业出版社,2004:197-205.

[2]West N.H E,Harris D.CMOS超大规模集成电路设计[M].汪东,泽.北京:中国电力出版社,2006.

[3]肖鹏,刘新宁,杜洪华.基于AMBA总线的NAND FLASH控制器软硬件划分设计[J].现代电子技术,2008(2):1-3.

XIAO Peng, LIU Xin-ning, DU Hong-hua.NAND FLASH controller design with software/hardware partition based on AMBA general bus[J].Modern Electronics Technique,2008(2):1-3.

[4]刘思平,陈利学.基于FPGA的NAND FLASH控制器[J].现代电子技术,2007,30(9):134-135.

LIU Si-ping,CHEN Li-xue.NAND FLASH controller based on FPGA[J].Modern Electronics Technique, 2007,30(9):134-135.

[5]张建文,王宏远.Reed-Solomon码的原理和软硬件实现[J].电视技术,2001(7):13-15.

ZHANG Jian-wen,WANG Hong-yuan.Principles of reedsolomon codes and implementation of software and hardware[J].TV Engineering, 2001(7):13-15.

[6]Samsung Electronics Corporation.K9F1G08U0B NandFlash Memory Data Sheet[EB/OL]. (2006-09-07).http://www.samsung.com.cn.