基于CPLD驱动的CCD整纬装置探头设计

2011-07-03陈伦琼范力旻

陈伦琼,范力旻

(常州工学院 电子信息与电气工程学院,常州 213002)

0 引言

纺织产品的整纬是非常重要的,纬弯或纬斜的存在会给产品质量带来极大的不利,利用光电式整纬装置进行检测和校正纬纱变形(即整纬)的方法是目前较为先进的整纬手段。我国从上世纪八十年代引进国外光电整纬装置,广泛用于纺织行业。但大多数的整纬装置的光电检测探头采用的是硅光电池作为感光传感器,硅光电池作为可见光及近红外光的光电探测器件,由于价格低、电流输出大、工作时不需外加电源而得到广泛使用。然而其工作特性容易受温度的影响而降低检测精度。而CCD器件是一种固体化器件,体积小,质量轻,功耗低,可靠性高,寿命长;图像畸变小,尺寸重现性好;光敏元件间距的几何尺寸准确性高,可获得较高的定位准确度和测量准确度。当然,CCD器件的外围驱动电路要求较高,产生严格的CCD芯片驱动时序,是应用CCD器件的先决条件。视频信号处理电路的设计也是至关重要的。但是,随着EDA技术的芯片设计技术的发展。CPLD可以将数字电路集成到一块芯片上,极大减小电路板的体积的同时其电路的升级和修改也非常简单和方便。将CPLD应用于CCD的外围电路并且结合A/D(模数转换器)和FIFO(先入先出缓存器)来设计,就可解决CCD信号的采集和处理难题。基于以上,本文主要是在前人的工作上将纬纱变形检测装置的“探头”中的光电传感器采用CCD器件。采用硅光电池的装置详见参考文献[1]。

1 探头的工作原理

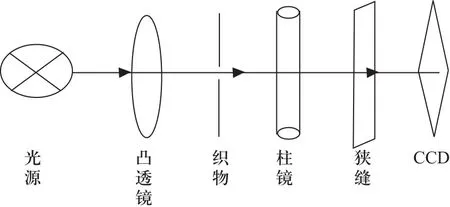

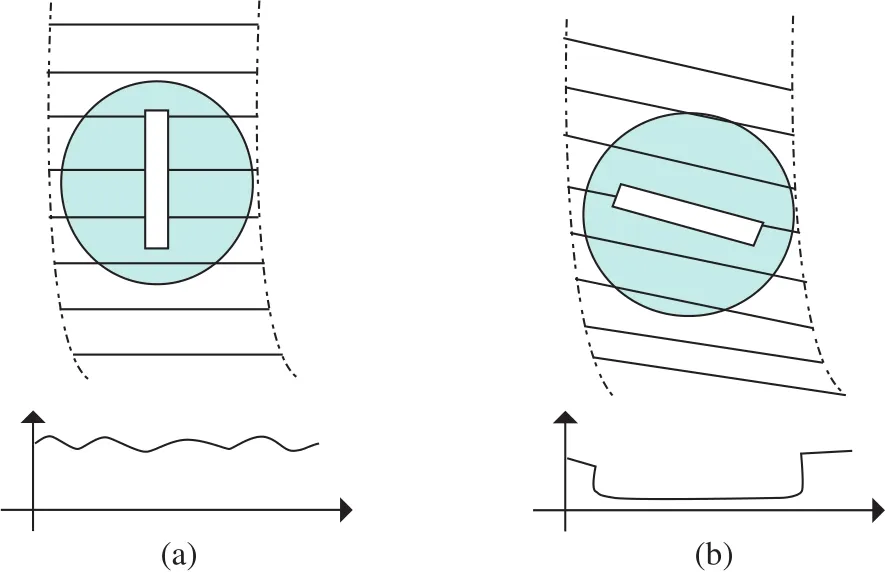

纬纱变形检测装置可根据布幅宽度设定检测头2~4个, 检测头采用“旋转光电探头”透射式原理[1],原理如图1所示,一定功率的可调光源经凸透镜后形成平行光,透过织物,经圆柱镜放大聚焦,在狭缝后的线阵CCD上成像,如果织物纬纱不断运动,在CCD最后输出的电信号就有变化。如图2所示,(a)图为狭缝与纬纱垂直时,CCD像素单元几乎无感光时的输出电平,(b)图为狭缝旋转至和纬纱重合时,CCD输出的信号最大。

图1 CCD检测原理图

图2 狭缝与纬纱不同角度输出示意图

2 探头的硬件设计

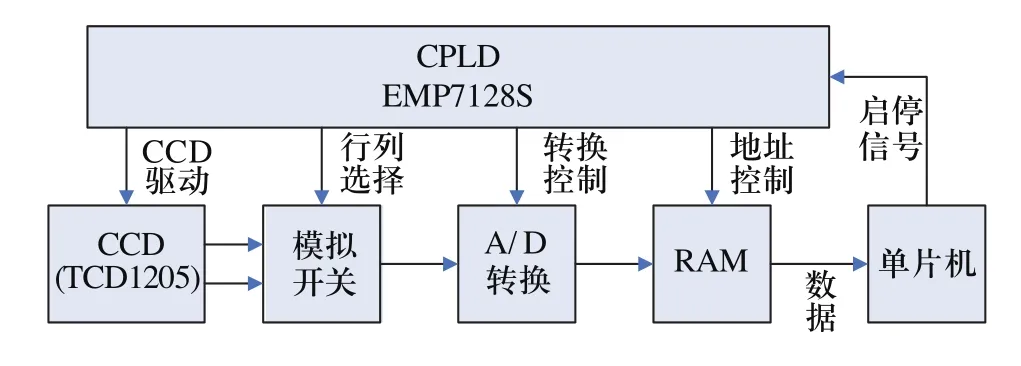

探头中的传感器采用的是CCD型号是TCD1205,而其驱动电路是以MAX7000(CPLD)为基础进行设计的。如图3所示,主要由CCD芯片、CCD时序产生和逻辑控制单元EPM7128、驱动电平转换及偏置电压单元、以及视频信号输出存储单元等几部分组成。

图3 硬件框图

其工作原理是,由于CCD感光成像,信号经过调理,由模拟开关分时切换进行A/D转换,数字化后在单片机的控制下数据送RAM存储。采集电路的核心是时序逻辑设计,用1片CPLD(EPM7128S)完成所有时序逻辑功能,包括CCD驱动信号、模拟开关控制信号、A/D转换的片选和转换控制信号、存储器操作所需的地址和控制信号。

1)模/数转换

MAX153是一个八位的模拟量转换为数字量的器件,最大转换电流为8安培,8V到28V的电压输出,660ns的转换时间。其作用是将来自CCD采集的模拟信号OS和DOS在通过多路开关的选择后,将它们转换为便于单片机和CPLD处理的数字信号,如图4所示。

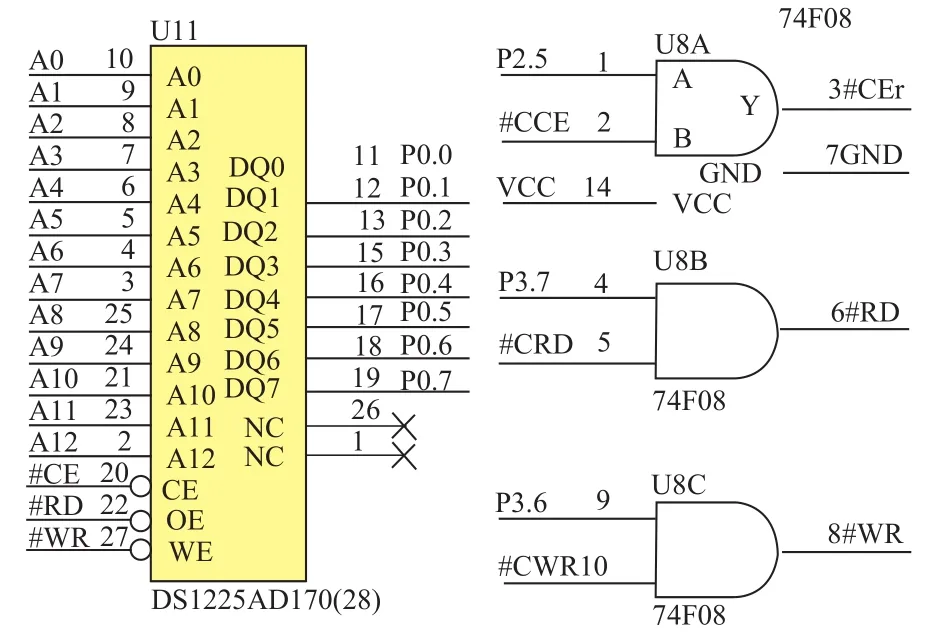

2)RAM存储设计

图4 模/数转换

如图5所示,单片机/CPLD利用单片机的地址线 A0到 A12(P0.0到 P0.7,P2.0到 P2.4)产生的16KB空间,通过P2.5/CCE对RAM的片选信号启动(/CE),P3.7/CRD对RAM的读信号(/RD),P3.6/CER对RAM的写信号(/WR)的控制。这些控制信号,控制着CCD将采集来的信号通过多路开关和A/D转换器件将采集的模拟量转换为2048×2的数字信号存储在RAM中以及单片机与CPLD对RAM内的数据的读取。

图5 存储设计

3)CCD时序处理

从EPM7128S输出的脉冲波形RS、SH、φ、ICG和BT是由基本TTL电路产生的,正逻辑为5V,负逻辑为0V,而TCD1205要求上述信号高电平为4.5到5.5V,低电平为0V;此外,CCD为电容性负载,工作频率高时有一定的功耗,因此用一片74HC04对RS、SH、φ、ICG和BT进行电平转换和驱动放大以驱动CCD工作,如图6所示。这样,在CCD的输出端将得到与入射光强相对应的模拟视频信号,并且视频信号的输出得到了相应的补偿。

3 软件设计

1)CPLD时序的软件设计

社区要搞一台消夏晚会。开演临近,一个小品还缺演员,居委会主任很着急。市人才交流中心的老王说,我来安排吧。他临时拉了几个人,没怎么排练就上台了。不料,演出大获成功!庆功宴上老王多喝了几杯,道出原委:他让公交售票员演泼妇,让大学教授演伪君子,让城管演土匪,让律师演骗子……

软件设计采用硬件描述语言的输入方式,如VHDL或Verilog,虽然不如原理图输入方式直观简单,但可移植性和可读性都很好,鉴于本设计的逻辑设计规模不大,为了驱动时序的通用性,因此利用MAX—PLUSII开发系统,采用的VHDL输入方式进行逻辑设计。VHDL语言程序设计流程图如图7所示。

图6 CCD时序驱动电路图

用VHDL产生频率大致相同的脉冲信号比较容易,比如CCD驱动信号中的RS、BT、φ1、φ2、以及A/D转换信号等。而要产生信号频率相差比较大的脉冲信号却比较困难,如要产生的SH、ICG、RS以及RAM的地址写信号等。有一个方式就是使用计数器来分频系统的时钟输入信号。下面的程序就可以实现信号的分频,多次分频就可以得到想要的频率信号。但是这样非常消耗资源,且计数器用的越多,延迟越大。这里采用另一种解决方案,通过分支CASE语句,通过一个15位矢量信号实现了功能要求:

signal qd1: std_logic_vector(14 downto 0);

……

case qd1 is

when "000000000000000" =>

rsbtc<='0';

init <='1';

ccdsh<= '1';

ccdicg <= '0';

ramfrom0<='1';

图7 时序设计流程图

……

end case;

由于所有的时序要求都是通过EPM7128S产生,系统中只有一个晶振,各芯片之间的逻辑关系完全由编程控制,因此很容易实现A/D转换和RAM控制之间的时序关系。最终仿真时序如图8所示。

图8 仿真时序图

2)单片机控制软件设计

单片机管理CCD数据的采集、接收、传送。数据的采集通过外中断实现。在初始化程序中设置与上位机的通信波特率、堆栈初始化以及寄存器初值,然后进入循环,等待中断的发生,调用中断子程序,实现预定功能。当上位机有命令到来时,进入串行中断子程序,在中断中根据预先定好的协议,判断计算机发来的不同命令,调用不同的处理子程序。其中的命令有:采集、停止采集、取数、停止取数。

4 结束语

由CCD作为整纬装置的检测传感器,由于采用了CPLD芯片实现CCD的驱动电路,因此其开发方便、快捷,系统功耗更小,成本也更低;同时编程调试也更方便。系统的体积大大缩小,可靠性也大大提高。这些对于改善整纬装置的整体性能有非常重大的意义。

[1] 郭建江. 新型单片机P89LPC935在光电整纬机中的应用[J]. 机电工程技术, 2006, (12): 97-99.