EV8AQ160型ADC在2.5 Gsps双通道高速信号采集系统中的应用

2011-06-05蔡春霞吴琼之丁一辰

蔡春霞,吴琼之,丁一辰

(北京理工大学 信息与电子学院,北京 100081)

ADC作为模拟量和数字量接口的关键部件,广泛应用于各领域,在信息技术中起着重要作用。高速ADC已成为决定诸如雷达、现代宽带通信系统、电子对抗等现代化电子设备性能的重要环节[1]。随着高速数据采集系统的快速发展和复杂性提高,对在很大程度上决定了系统整体性能的ADC要求也越来越高。文中提出一种新的解决方案,采用高速ADC EV8AQ160进行准确性较高且较稳定的数据采样,使得系统中ADC转换电路具有较好的信噪比。

1 系统概述

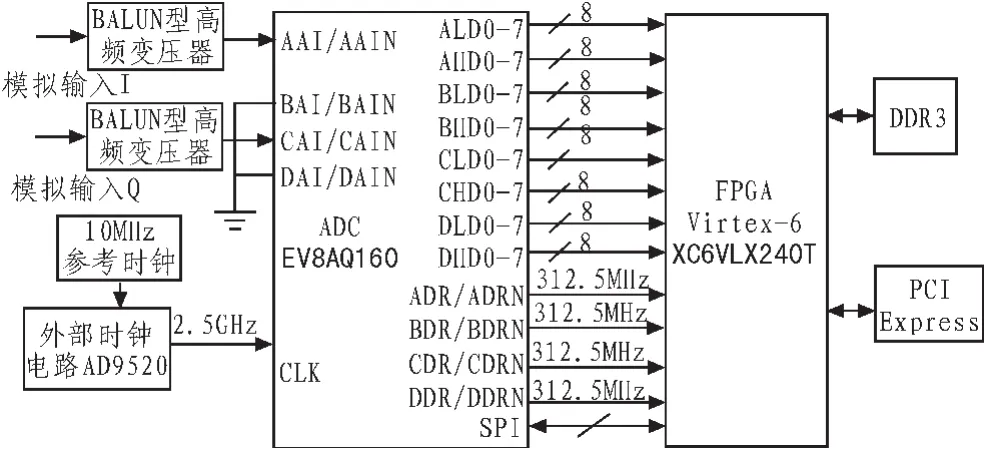

图1所示为基于EV8AQ160[2]的2.5 Gsps数据采集系统的原理框图。两路模拟输入信号分别从外部接入,经过BALUN型高频变压器完成单端信号到差分信号的转换,然后送入ADC输入端。ADC的2.5 GHz时钟由低抖动、低相位噪声锁相环芯片AD9520-1[3]提供。FPGA用64个LVDS数据输入通道[4]接收来自EV8AQ160的8路8 bit-625 Msps的数据输出,并用4个LVDS时钟输入通道接收4路ADC给出的312.5 MHz同步采样时钟。FPGA将接收到的数据进行预处理存储后到第三代双倍速率同步动态随机存储器(DDR3)中,需要对采集的数据进行后续处理时,将数据从DDR3中取出,并通过总线和接口标准(PCI Express)传送给上位机。整个硬件系统仅采用一片FPGA来处理,并作为主控芯片对整个系统进行通信和控制,大大提高了系统的运行速度。本设计 采 用 Xilinx公 司 Virtex-6系 列 FPGA, 型 号 为XC6VLX240T-1156C。

2EV8AQ160的主要特点

图1 2.5Gsps高速数据采集系统原理框图Fig.1 Block diagram of 2.5Gsps high-speed data acquisition system

EV8AQ160在片内集成了4路ADC,可以工作在3种模式下,最高采样率可达5 Gsps。要求2.5 GHz差分对称时钟输入,可进行ADC主复位。EV8AQ160内部集成了1:1和1:2的数据多路分离器(DMUX)和LVDS输出缓冲器,可以降低输出数据率,方便与多种类型的高速FPGA直接相连,实现高速率的数据存储和处理。为了补偿由于器件参数离散和传输路径差异所造成的采样数据误差,该ADC具有针对每路ADC 数据的积分非线性(INL)、增益(Gain)、偏置(Offset)、相位(Phase)的控制和校正。EV8AQ160提供测试功能,且具有两种测试方式,如表1所示,方便用户根据自己的习惯对ADC是否正常工作进行测试。

表1 测试模式说明Tab.1 Description of test mode

EV8AQ160共有380个外部管脚,按性质主要分为模拟、数字两部分。模拟部分引脚分为模拟电源和模拟输入两类。模拟电源为3.3 V,模拟输入必须配置成差分输入,并且具有500 mV的峰峰值。有4个差分模拟输入,如AAI/AAIN,若前端信号是单端的,则必须经过一个射频转换器将单端信号转换为差分信号。数字部分包括1.8 V的数字电源以及输出电源、时钟输入、数据输出信号(包括数据溢出修正位)、SPI接口信号。其他信号包括SPI异步复位信号,扫描模式信号,同步信号,温敏信号,参考阻抗信号、输出共模电压参考信号等。

3 EV8AQ160的串行控制端口

EV8AQ160的所有参数,包括通道选择、旁路模式、编码格式、输出多路分离器、积分非线性校准、偏置校准、增益校准、相位校准等,均通过串行控制端口对相应的控制寄存器进行设置。串行控制端口写入的字长为24 bit,8位地址A[7]到 A[0],包括一位读写(R/W)控制位A[7],以及 16位数据 D[15]到D[0],均以MSB首传。串行控制端口由5条控制线组成,如表2所示。

表2 串行控制端口说明Tab.2 Description of serial control port

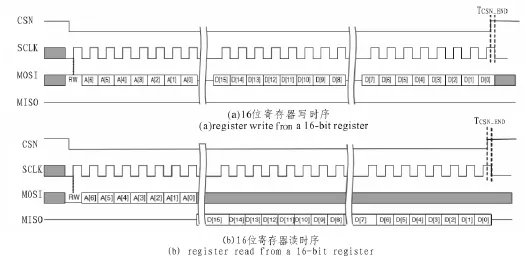

MOSI线上的序列应该从读写控制位开始,当R/W=1时进行写操作,时序见图2(a),R/W=0时进行读操作,时序见图2(b)。为使串行控制端口能正确配置ADC的控制寄存器,设计时序时要注意CSN在SCLK的第一个正脉冲上升之前须提前拉低,在最后一个正脉冲下降之前须提前拉高。

图2 16位寄存器读/写时序Fig.2 Read/write timings of a 16-bit register

4 EV8AQ160工作模式的选择

EV8AQ160可工作在3种模式下,分别为采样率为1.25 Gbps的四通道模式,采样率为2.5 Gbps的双通道模式以及采样率为5 Gbps的单通道模式。这样,用户可根据自身需求进行选择,增强了使用灵活性。

EV8AQ160内部的4路ADC的时钟均由同一外部输入时钟驱动,即4路ADC共用时钟电路。时钟模块接收外部的2.5 GHz时钟,该时钟信号会被2分频为1.25 GHz,以驱动内部的采样时钟。

在四通道模式,同一个1.25 GHz时钟直接驱动4路ADC内核以及跟踪保持(T/H)模块,此时将得到1.25 Gbps的等效采样率。在双通道模式下,同相1.25 GHz会驱动A或C路ADC,反相的1.25 GHz会驱动B或D路ADC,此时在交错模式下将得到2.5 Gsps的等效采样率。在单通道模式下,同相的1.25 GHz时钟驱动A路ADC,同时反相的1.25 GHz时钟驱动B路ADC,同相的1.25 GHz时钟经过90°延迟后驱动C路ADC,反相的1.25 GHz时钟也经过90°延迟后驱动D路ADC,此时在交错模式下将得到5 Gsps的等效采样率。

四通道模式,每路模拟输入均一一对应。双通道模式,可任选其中两路ADC构成一组,本设计将A、B选为一组,C、D选为另一组,2路模拟信号从A路和C路分别输入,如图3所示。此时,A路模拟输入信号将在内部与B路ADC连通。同理,C路的输入信号也会在内部与D路ADC连通。单通道模式,模拟信号可在4路ADC中任选一路输入,输入信号将在内部与其他3路ADC连通。

5 与FPGA的数据接口

图3 双通道模式时钟驱动(模拟信号从A和C输入)Fig.3 Two-channel mode configuration(analog input A and analog input C)

通常ADC的输出与高速逻辑电路相连,进行数据的存储和处理。EV8AQ160设置了两种输出工作模式,当DMUX=1:1时,为优化ADC的功耗,一半的数据输出缓存(L端口数据位)将会关掉,此时的数据输出率最高为1.25 Gsps,4路ADC全部工作时,输出数据宽度为32位;当DMUX=1:2时,全部数据输出缓存均打开,数据输出率最高为625 Msps,4路ADC全部工作时,输出数据宽度为64位。

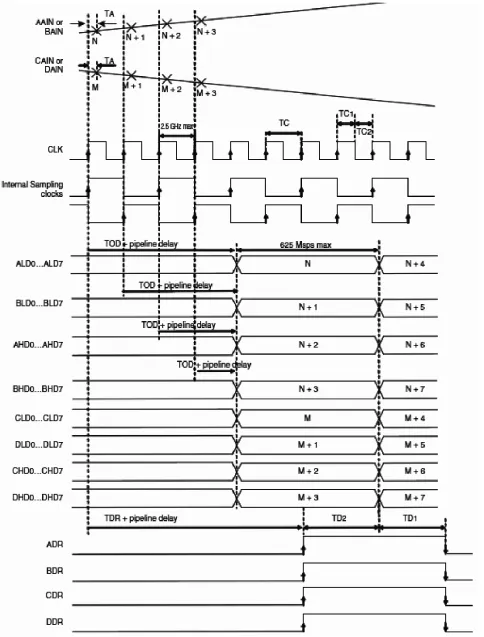

图4 EV8AQ160双通道模式1:2 DMUX模式的工作时序Fig.4 ADC timing in two-channel mode,1:2 DMUX mode

本设计中,ADC工作在双通道模式下,且将A、B选为一组,C、D选为另一组,2路模拟信号从A路和C路分别输入,以DMUX=1:2模式输出,此时ADC的工作时序如图4所示。在 (AAI,AAIN)上的输入将会在 ALD0…ALD7,AHD0…AHD7和BLD0…BLD7,BHD0…BHD7上以交错模式输出。同理,在(CAI,CAIN)上的输入将会在 CLD0…CLD7,CHD0…CHD7和DLD0…DLD7,DHD0…DHD7上以交错模式输出。内部以1.25 GHz进行采样,输出数据的同时输出312.5 MHz同步采样时钟。

图4所示ADC工作时序中,数据输出延迟TOD是一个固定的延时值,TOD加上流水线传输延时就是总的输出延时。为了能让FPGA等接收系统同步接收2路输入对应的输出数据,ADC内部针对每路输出做了延时控制,确保转换数据能在同一相位输出。从图4中可知,1:2 DUMX,A路低8位输出延迟4个时钟周期,B路低8位延迟3个时钟周期,A路高8位延迟2个时钟周期,而B路高8位延迟1个时钟周期。C、D路分别与A、B路延迟控制相同。

ADC输出8路8 bit-625 Msps低电压差分信号(LVDS)逻辑的数据,在采集系统设计中对与其接口器件的性能要求也较高。Xilinx公司Virtex-6系列型号为XC6VLX240T-1156C的FPGA具有高达200个专用LVDS差分逻辑接收通道,双数据率(DDR)LVDS通道发送数据速率高达1.25 Gbps,接收数据速率也高达1.0 Gbps,能够满足接收EV8AQ160输出数据和逻辑控制的要求。由于ADC的输出和FPGA的输入均设计为LVDS逻辑标准,因此ADC可直接与FPGA相连。Virtex-6系列FPGA内部具有专门的LVDS处理单元,可实现LVDS逻辑的串/并降速转换,降低速率后的数据给到内部分布式处理算法(DPA)单元进行精确处理。

图5 用ChipScope Pro抓取ADC的输出数据Fig.5 Output data of ADC using ChipScope Pro to get

本设计中,采用Xilinx公司ISE软件中的ChipScope Pro工具将逻辑分析器、总线分析器和虚拟I/O小型软件核直接插入到设计当中,直接查看ADC输出的数字信号,这些信号在操作系统速度下或接近操作系统速度下被采集,并从编程接口中引出,再将采集到的信号通过ChipScope Pro逻辑分析器进行分析[5]。

首先让ADC工作在采样率为2.5 Gsps的双通道模式下,用测试模式1来检验ADC与FPGA之间的数据接口的准确性。将测试程序下载到FPGA并运行后,用ChipScope Pro抓取ADC的输出数据如图5(a)所示。然后在双通道模式下不使用测试模式,输入2 MHz的正弦信号,用ChipScope Pro抓取ADC的输出数据如图5(b)所示。

从图5(a)中的数据可以看出,各个通道均以约定的格式输出,说明ADC与FPGA之间数据接口已经准确连通。图5(b)中,输入正弦信号时用BUS PLOT工具将抓取到的数据实时画图,得到的波形平滑,计算其信噪比为43.7 dB,根据SNR与有效位数之间的换算公式:SNR=6.02N+1.76 (1)

计算得到ADC的有效位数为7.0 bit。实测表明,EV8AQ160具有较高的性能,整体指标达到设计要求。

6 采样时钟的产生

任何高速模数变换器都对采样时钟的质量非常敏感.采样时钟中的噪声,特别是相位噪声将反映都模数变换中,使得ADC的动态性能降低[6]。为满足EV8AQ160对高质量采样时钟的要求,这里采用低抖动、低相位噪声锁相环时钟芯片AD9520-1提供2.5 GHz采样时钟。AD9520-1片内VCO可从2.27 GHz调节到2.65 GHz,还支持外部3.3 V或5 V供电,频率高达2.4 GHz的VCO/VCXO。AD9520-1支持SPI和I2C接口,片内集成一片EEPROM可通过串行接口编程以及保存用于上电复位的用户定义存储器的设置。有4组共12个LVPECL时钟输出,任何一个LVPECL输出在时钟频率不大于250 MHz时均可重新定义为2个CMOS输出,并且在上电时可自动同步所有的输出。AD9520-1可为高速ADC、DAC、DDS、DUC等等提供驱动时钟,还可应用于高性能无线收发器,自动测试仪器(ATE)以及宽频带通信设施等。实测表明,低抖动、低相位噪声锁相环AD9520-1能够满足EV8AQ160对时钟的要求。

7 结束语

介绍了采样速率高达5 Gsps的EV8AQ160型模数转换器,并将其应用在2.5 Gsps双通道高速数字采集系统中。通过对ADC性能进行测试,证明基于EV8AQ160的数据采集系统采样速率达到了2.5 Gsps且输出数据准确性较高,信噪较好,可以应用到其他高速ADC系统,如现代宽带通信系统、航天航空、测控、医学图像、高速示波器、现代频谱分析仪等。

[1]张宁,许洪光,张钦宇.AT84AD001型ADC在2 GHz高速信号采集系统中的应用[J].电子设计工程,2006(10):41-44.ZHANG Ning,XU Hong-guang,ZHANG Xin-yu.Application of ADC AT84AD001 in 2 GHz signal collection system[J].Electronic Design Engineering,2006(10):41-44.

[2]English e2v Corporation.EV8AQ160 QUAD ADC Data Sheet[EB/OL].http://www.e2v.com/assets/media/files/documents/broadband-data-converters/doc0846I.pdf.

[3]ANALOG DEVICES.12 LVPECL/24 CMOS output clock generator with integrated 2.5 GHz VCO AD9520-1 data sheet[EB/OL].http://www.analog.com/static/imported-files/data_sheets/AD95 20-1.pdf.

[4]Xilinx Corporation.Virtex-6 series FPGA data sheets[EB/OL].http://www.xilinx.com.

[5]田耘,胡彬,徐文波.Xilinx ISE Design Suite 10.x FPGA开发指南[M].北京:人民邮电出版社,2008.

[6]田晓霞,阮林波,田耕.2 Gsps高速数据采集系统的设计与实现[J].微计算机信息,2011,27(3):40-41.TIAN Xiao-xia,RUAN Lin-bo,TIAN Geng.Designand implementation of 2 Gsps high-speed data acquisition system[J].Microcomputer Information,2011,27(3):40-41.