电子式互感器数字接口通信研究

2011-05-11鄢志平邓忠华

鄢志平,邓忠华

(1.广州市电力工程设计院有限公司,广东 广州,510220;2.广州伟钰光电科技有限公司,广东 广州,511495)

1 概述

近年来,电子式互感器的研究发展迅速,尤其是基于Rogowski线圈的电子式电流互感器已进入产品实用化阶段。对于电子式互感器在变电站自动化系统中的推广应用,面临的首要问题是要解决好过程层合并单元与间隔层二次设备以及互感器与合并单元之间的接口与通信。目前,国际电工委员会已制定出相关国际标准IEC60044-7/8和IEC61850,这些标准均详细定义和描述了信息合并单元,并严格规范了合并单元与间隔层二次设备的接口方式,同时也对合并单元与二次设备之间的通信协议做了详细的规定;但作为一次设备的互感器与合并单元通信接口的完整数字格式还没有统一的规范[1]。本文通过对拟定的通信方案仿真研究,结合样机测试验证,介绍了互感器与合并单元数据通信的实验研究结果。

2 过程层互感器数字接口总体设计方案介绍

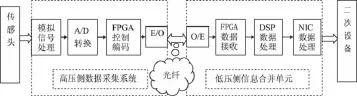

按照IEC61850协议信息分层的观点,所定义的过程层是属于一次设备与二次设备的结合面,或者说过程层是指智能化电气设备的智能化部分。电子式互感器作为过程层设备,根据其各个部分功能的不同,可将互感器分为传感头、数据采集系统、光纤传输及接口、电源功能装置、合并单元;其中高压侧数据采集系统、光纤传输系统、合并单元共同组成电子式互感器的数字接口,负责接收、传输、处理各种信号[2]。

高压侧数据采集系统作为电子式互感器数字接口的重要组成部分,它主要完成对传感元件输出的电流、电压信号的同步高速采样以及对采样值进行信道编码并转换成光信号传输;另一方面,信息合并单元作为电子式互感器数字接口的核心部分,它是连接高压侧数据采集系统与间隔层二次设备的桥梁,主要负责并行接收和实时处理多路数字信号,同时还需要根据采样率要求发出同步采样命令,具有数据处理和数据通信可靠性、实时性要求高,数据通信流量大等特点[3],在此情况下,通用单片机和DSP难以完成任务。鉴于此,本文提出了一种基于FPGA和DSP技术相结合的电子式互感器数字接口实现方案。

高压侧数据采集系统利用FPGA作为与模数转换器件的接口,在单一芯片内实现同步采样控制和数据编码传输的功能;合并单元利用FPGA完成同步采样命令的产生以及多路串行数据的介绍,同时利用DSP的强大数据处理功能实现数据处理和数据输出接口功能。其总体硬件接口实现功能电路可用图1表示。

图1 过程层接口总体结构图

3 FPGA采样逻辑控制电路设计

本文FPGA设计将采用Lattice公司LFXP6系列芯片,以及和其相应的ispDesignEXPERT集成开发环境。ispDesignEXPERT是目前流行的EDA软件中最容易掌握的设计工具之一,它界面友好、操作方便、功能强大,并与第三方EDA工具Synplify(逻辑综合性能最好)和Modelsim(仿真功能最强大)兼容良好,通过它可以进行VHDL、Verilog及ABEL语言的设计输入、综合、适配、仿真和在系统下载。

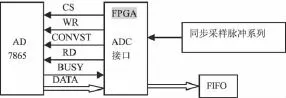

FPGA采样逻辑控制电路主要完成ADC与串行通信线之间的接口功能。它控制A/D芯片对电压/电流互感器输出的二次电压信号进行等间隔周期采样转换,每一次转换完毕后通过并行线读出ADC的转换结果。其硬件原理实现框图如图2所示。

图2 FPGA控制ADC示意图

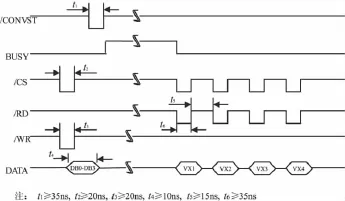

要让FPGA正确控制AD7865按采样周期进行采样转换并且及时读出转换结果,最关键的是要分析AD7865的时序图,弄清楚它的工作过程,然后在FPGA中产生与之相配合的信号时序波形。图3给出了AD7865时序图的关键部分。

图3 AD7865主要时序图

设计时结合AD7865芯片时序图,分析AD7865工作过程如下:

(1)开始转换前,FPGA通过 DB0~DB3向AD7865中的通道选择寄存器写入四位二进制数据确定器件需要转换哪几个模拟通道。

(2)FPGA向AD7865发出转换命令/CONVST,器件在/CONVST信号的上升沿启动AD7865,保持器同时对四路输入模拟量的瞬时值进行采样、保持,然后芯片内控制电路控制依次按顺序对要求转换的模拟通道进行模数转换.在转换过程中,BUSY输出引脚一直处于高电平,提示FPGA转换正在进行。

(3)四路模拟量全部转换完后AD7865输出转换结束信号,BUSY输出引脚变低电平,表示所有转换完成,然后FPGA可以从14位并行数字接口依次读出各路模拟量的转换结果。

设计中,FPGA对AD7865的控制读写时序由状态机来实现。上电后FPGA先对AD7865进行初始化写操作,告诉它对几路模拟输入通道进行转换,然后等待同步采样序列接收器发出的采样脉冲信号SP,收到采样脉冲信号后FPGA向AD7865发出转换开始命令开始对第一路模拟输入通道进行转换,FPGA这时等待AD7865的转换结束信号。当预定的几路模拟输入通道全部转换完毕之后AD7865给出转换结束信号,FPGA收到后依次读出各通道的采样值并存入FPGA内部的FIFO,完成一次采样过程;然后又等待同步采样序列接收器发出的采样脉冲信号,循环往复。使用AD7865模拟通道的路数可以由程序中一个常数CNT来确定,要修改使用的模拟通道路数只需修改此常数值即可,设计非常灵活。

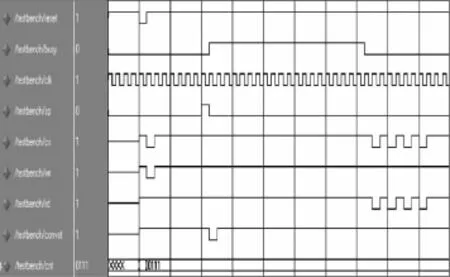

硬件描述语言VHDL程序设计在Modelsim中功能仿真结果如图4所示。图中CLK为时钟信号,用来驱动状态机;输入信号SP是同步采样序列接收器收到的同步采样脉冲,CONVST、BUSY、CS、RD、WR 分别对应AD7865的五个控制信号,CNT是AD7865数据线的最低四位用来向其写入初始化数据以选择相应的模拟通道;整个AD采样逻辑控制过程在系统复位后进行,从图中可以看出FPGA中实现的时序关系满足AD7865时序图的要求,在实际电路板上的实验也证明了程序功能的正确性。

图4 FPGA控制AD7865仿真图

4 合并单元数据接收模块设计

根据样机设计采用的ECT与IMU接口规范,它主要完成的功能包括:负责对合并单元所需接收的多路通用异步串行数据流进行接收、串并转换;然后将接收到的一个链路帧信息内部的多个UART帧有效字节信息组帧还原后,将采样信息送至接收端CRC反校验模块进行检验,以保证合并单元接收到的各路数据正确有效。其大致实现框图可用图5来表示。

图5 信息合并单元结构框图

4.1 UART数据接收模块设计与实现

UART数据接收模块主要完成的任务是从每一数据通道的通用异步串行数据流中不断地提取UART帧内8位有效数据并进行串并转换,同时完成UART帧数据奇偶校验,确保接收的每一帧UART数据正确有效。一帧UART数据接收完成后,模块输出相应的奇偶校验和数据接收完毕标志信号。具体的数据接收过程用状态机描述如下:

(1)状态S1(等待起始位):系统复位后,接收模块的有限状态机复位成状态S1,此时将对内部各种寄存器赋予初值;同时捕捉起始位,判断可能的第一个数据起始位的到来。一旦起始位确定,状态机将进入下一状态S2。

(2)状态S2(求中点):当接收字符长度计数器小于或等于一帧字符长度时,对采样脉冲计数器计数值进行判断,确保每一位数据在中间位置采样接收,条件满足时系统进入下一状态S3准备接收数据位;数据位接收完成后,状态机将返回该状态对采样脉冲继续计数,此时当采样脉冲计数器计数到第15个采样脉冲时,系统进入状态S5,判断一UART帧的结束。接收起始位时,接收端采样值低电平应维持8个采样时钟周期以确定它是一个有效的开始位;

(3)状态S3(数据位接收):将待接收的数据位移入数据接收缓冲寄存器,同时将数据位信息送入奇偶校验寄存器异或进行奇偶校验;数据位接收完成后,状态机重新返回状态S2。

(4)状态S4(等待接收新的数据位):,在此状态下采样脉冲计数器将重置初值,同时接收字符长度计数器进行加1计算;然后状态机下一状态无条件地转入状态S2执行;

(5)状态S5(停止位检测):判断一帧UART数据是否接收完成。如果条件成立,此时接收字符长度计数器清零,同时对数据奇偶结果进行有效性判断,并且下一接收时钟脉冲上述沿时刻状态机将返回S1状态;否则,状态机进入状态S4,等待接收新的数据位。

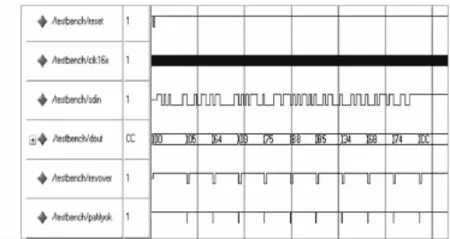

采用上述状态机完成的程序设计非常灵活,状态机对每一位数据接收完成后都对其进行判断,是否为一帧数据的结束(停止位),这使得两帧UART数据帧之间有无空闲位都不会对数据接收端产生影响。VHDL程序设计功能仿真波形如图6所示。

图6 UART数据接收仿真图

仿真图中,系统定义复位信号RESET低电平有效,CLK16X为波特率16倍频的数据接收时钟,SDIN表示为所需接收的通用异步串行数据流,DOUT为待输出的UART帧内有效字节信息,REVOVER为一帧数据接收完毕标志,PATITYOK为奇偶校验正确标志,低电平有效。为了说明设计的正确性,给出了一个链路帧数据的仿真结果,从图中信号DOUT输出的有效字节信息来看,通过与信号SDIN输入的仿真数据进行分析比较,设计结果完全正确。

4.2 链路帧信息还原模块设计与实现

链路层数据还原模块主要完成的功能包括:将UART接收模块接收到一链路帧内的多个有效字节信息按协议中链路层信息帧格式还原,并送至CRC反校验模块进行检验。如果数据校验未发生错误,存入FIFO单元待DSP读取;否则,一帧数据将丢弃。

该程序的设计难点是如何判断所接收到的多个字节数据是否属于一个完整的链路帧数据信息(一个链路帧内容一般包括帧头、帧长度、采样值、采样序号、CRC校验码等信息)。为此,作者在程序设计过程中定义了两个计数控制寄存器A和B。系统复位后,当链路层数据还原模块采样到UART数据接收模块发出的第一个REVOVER低电平有效信号后,启动计数器A对接收字节个数进行计数,同时启动计数器B对接收脉冲时钟ClK16X进行计数,根据一个链路帧信息所含的数据位个数和波特率,程序设计时可以设定一个合适的时间T;当计数器B计数时间t<T时,如果计数器A计数个数N满一帧字节个数,表示此时接收的字节数为完整的一个链路帧数据信息;否则,表明一链路帧数据不是从起始字节位置开始接收起,数据无效,等待接收下一链路帧数据。

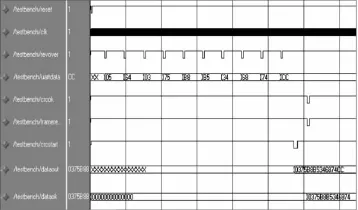

整个过程可用文字说明如下:系统复位完成后,每一个REVOVER有效信号到来时,链路帧信息还原模块将8位UART帧内字节信息并行存入内部接收寄存器。通过启动计数器A和B,判断一链路帧内多个字节信息是否完整接收。如果数据有效,发出 CRCSTART信号,启动CRC反校验模块对接收到的链路帧信息进行CRC校验,等待校验完成之后,如果CRCOK信号有效,模块发出FRAMEREADY信号,通知数据缓存FIFO表示一完整链路帧信息接收OK,同时将信号DATAOK所包含的信息存入FIFO;否则,一帧数据无效,将被丢弃。程序仿真结果如图7所示。

图7 链路帧信息还原模块功能仿真图

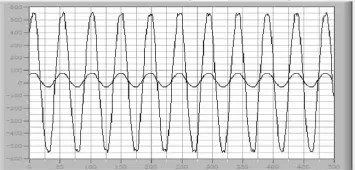

5 过程层数字接口通信的实现

实验中,将空心线圈经采集器输出的数字采样值分别接入合并单元装置定义的A、B、C数据接收通道,在模拟现场额定一次电流400 A的电磁环境下,通过Sniffer协议分析软件对合并单元以太网输出帧的内容准确性进行分析验证。实验结果证明:所设计的过程层数字接口通信完全得以实现;在此基础之上,合并单元持续上电72 h,利用自行开发的分析软件对合并单元以太网输出数据进行跟踪测试,结果未发现合并单元以太网数据输出丢包记录,且所得到的保护和测量信号还原波形完整性良好如图8所示。

图8 过程层数字接口输出数据还原波形

6 结束语

FPGA与DSP相结合的电子式互感器数字接口通信和数据处理方案,充分利用了FPGA由用户定制专用硬件电路的高速、并行处理能力和DSP在已有硬件条件下进行软件编程控制的能力。实验证明该方案满足电子式互感器数字接口高速、稳定的要求。

[1]罗承沐,张贵新,王 鹏.电子式互感器及其技术发展现状[J].电力设备,2007,8(1):20-24.

[2]徐 雁,叶妙元,张 庆,等.光电互感器的应用和接口问题[J].电力系统自动化,2001,25(12):45-48.

[3]刘 琨,周有庆,彭红海,等.电子式互感器合并单元的研究与设计[J].电力自动化设备,2006,26(4):67-71.