3英寸高纯半绝缘6H-SiC单晶的研制

2011-04-18王利杰齐海涛王香泉郝建民严如岳

王利杰,洪 颖,齐海涛,冯 玢,王香泉,郝建民,严如岳

(中国电子科技集团公司第46研究所,天津 300220)

0 引言

半绝缘SiC单晶抛光片是现阶段制备宽禁带固态微波器件的最佳衬底[1,2]。目前,我国已成功研制出3英寸钒掺杂4H和6H晶型半绝缘SiC单晶材料,标志着我国在研制半绝缘性SiC单晶材料方面已经取得突破[3]。众所周知,对碳化硅材料而言,实现半绝缘的技术途径有两条:一条是通过引入深受主杂质与浅施主补偿,实现半绝缘;另一条是通过材料本身的深受主能级与浅施主能级补偿实现半绝缘。后者因为在单晶生长过程中没有人为引入受主杂质,称为高纯半绝缘。目前,国内半绝缘碳化硅单晶研究,主要局限在掺钒材料上,未见高纯半绝缘的报导,国外也只有美国CREE公司实现了高纯半绝缘衬底商品化。早在2003年前后,Nabil Sghaier等[4]分别对掺钒和高纯半绝缘碳化硅衬底与器件性能关系进行了比较研究,得到的结论为,掺钒碳化硅衬底中的深俘获中心影响高频大功率器件的功率输出。因此,制备高性能固态微波器件首选高纯半绝缘碳化硅衬底。本文报导了我们近期高纯半绝缘6H-SiC单晶的研究结果。

1 高纯半绝缘6H-SiC单晶的制备

采用物理气相传输(PVT)法成功制备出3英寸高纯半绝缘6H-SiC单晶。坩埚和保温系统结构设计和材料优选、源粉纯化与合成,以及籽晶粘结等工艺都与生长2英寸掺钒半绝缘6H-SiC单晶一致[5],大尺寸单晶的生长技术,也已有专门讨论[6]。本部分重点描述高纯半绝缘的实现。

PVT生长碳化硅单晶使用的坩埚及其保温系统由不同密度的石墨构成,原料为碳化硅粉末,这些石墨构件和粉末不可避免地吸附空气中的氮,又由于生长环境通常为几帕到几百帕,在这种生长条件下,吸附的氮容易在生长过程中解吸附,并掺入碳化硅单晶。在6HSiC单晶中氮占碳位[7],对应六方和两个准立方氮占位能级分别为 Ec-81.0、Ec-137.6 和 Ec-142.4 meV,是典型浅施主能级,离化能量低,即使在室温下,离化率也很高。可见,在半绝缘碳化硅工艺制备中有效抑制氮占碳位是制备高纯半绝缘碳化硅材料的关键。

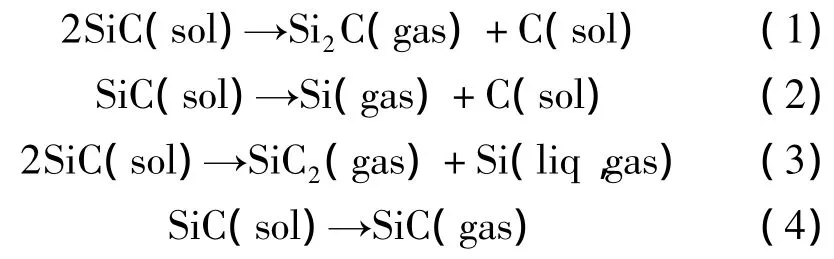

V.D.Heydemann等对氮在碳化硅晶格中的占位规律进行了研究[8],在一个籽晶托上粘两个不同极性面的籽晶,以保证两个籽晶在完全相同的环境条件中生长,从而两个样品中显施主效应的氮浓度的差别主要来自竞位效应。结果表明采用碳面籽晶生长的碳化硅晶体中的氮含量是采用硅面的2~3倍。该结果解释为:碳面生长前沿产生比较多的碳空位,提高了氮占碳位的几率,碳空位越多,氮越容易进入到碳化硅晶体内。可见,尽量减少碳化硅单晶生长前沿碳空位是降低碳化硅晶体内氮含量的重要手段。PVT生长碳化硅单晶[0001]表面生长前沿原子排列示意图,如图1所示。Pons等[9]证实PVT生长碳化硅单晶的传质方式是扩散,因此控制输运到生长前沿的Si、C气相组分即可有效控制碳空位数量。

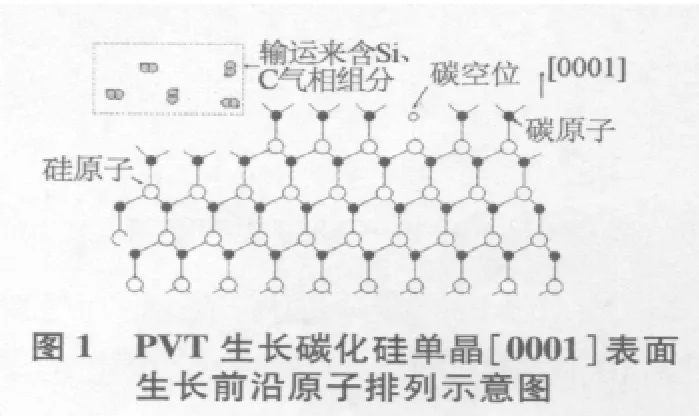

PVT法碳化硅单晶生长室的内壁由石墨坩埚、碳化硅源粉和生长中的晶体表面构成。在高温下,碳化硅源粉发生如下热解反应,即升华[10]:

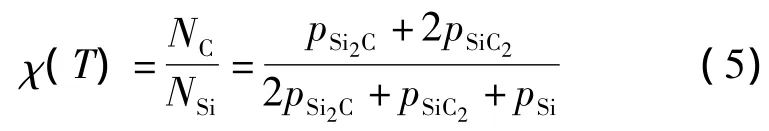

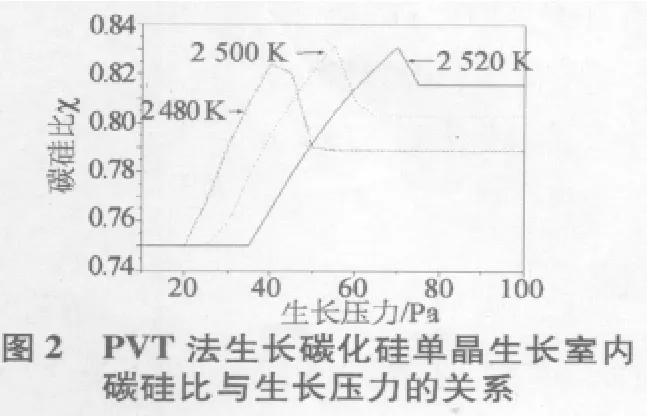

SiC源粉热分解后形成不同的气相组分,反应产物中主要气相组分有Si、Si2C和SiC2,这些组分均由Si和C两种基本元素组成的。PVT法碳化硅单晶生长温度范围为2000 K~2900 K,Si、Si2C和SiC2三组分的平衡分压已有详细计算[9,11]。设 Nc和 Nsi分别表示生长室内C和Si原子的总量,当生长气氛(通常为氩气)压力高于任一组分压力时,生长室内C和Si原子化学计量比χ是温度的函数,可表示为

当生长气氛压力降低时,有些含Si、C组分的分压可能高过生长气氛,部分组分将逸出,使生长室内碳硅比发生变化。这种情况下,碳硅比χ不再仅是温度的函数,还与生长室压力有关。计算2480 K、2500 K和2520 K三个温度下,碳硅比χ随生长室压力变化情况,如图2所示。从图中可以看出,当压力过低时,碳硅比χ与温度和压力都无关,为0.75;对于特定的温度,当压力高过某个值时,碳硅比χ不变,但该χ值是温度的函数,随温度升高而增加。值得特别注意的是:对于任一温度,改变生长室压力,碳硅比χ都存在最大值,且该最大值随温度升高向高压力方向移动,因此,改变生长室压力,可有效控制碳硅比。基于这样的热力学计算结果,实现了碳硅比的控制,进而实现抑制氮元素进入目的。

采用PVT工艺,在较宽的温度范围内都可实现碳化硅单晶的生长。早期大都采用高温的生长方式,其典型特点是生长温度高(>2700 K)、气压高、生长速率高,这种工艺的可控性不强,所生长晶体的质量也较差。本文提出低生长温度、低气压、低生长速率的思路,通常生长速率控制在100~150 μm/h内,可有效抑制包裹体、微管缺陷等的生成。

2 高纯半绝缘6H-SiC单晶的测试表征

晶体生长后,首先经滚圆工艺,将其直径滚成标准3英寸,结果如图3所示。随后进行多线切割,得到23片直径3英寸的切割片,对这些晶片按照生长先后顺序依次编号,然后进行电性能、纯度、深能级中心三方面的测试表征,并根据测试需要对样品进行后续研磨、抛光、划片等加工工艺。

2.1 非接触电阻率测试

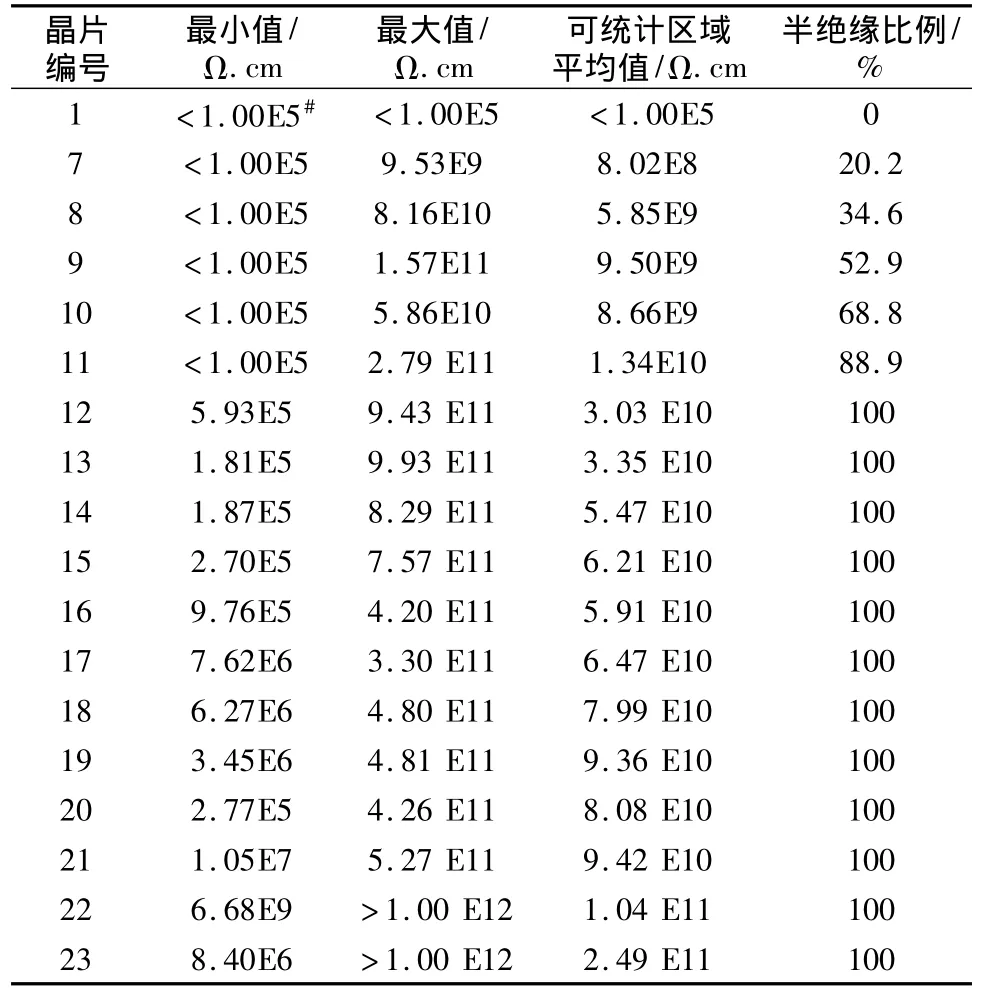

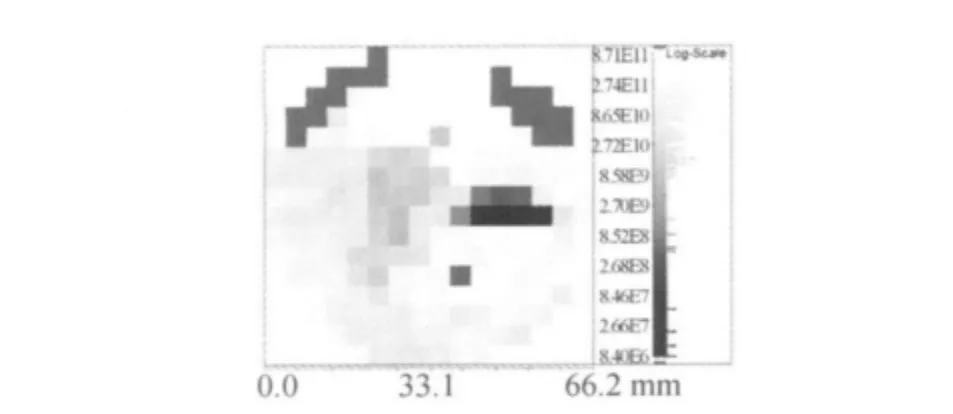

对上述23片6H-SiC单晶切割片逐片进行非接触电阻率面分布(COREMA)测试,测试系统引进于德国SemiMap公司,型号COREMA-WT。测试结果见表1,典型电阻率范围为108~1012Ωcm(实际测试上限是1012Ωcm,下限为105Ωcm),按照 Cree公司电阻率大于105Ωcm定义为半绝缘的原则[12],在23片样品中有12片为100%面积半绝缘。第23号6H-SiC单晶切割片的电阻率面分布图,如图4所示。

表1 同一晶锭23个晶片电阻率统计结果

图4 第23号6H-SiC晶片的电阻率面分布图

从图中同样可以看出:电阻率都大于105Ωcm,最小值为8.40×106Ωcm,最大值超过1.00×1012Ωcm的测试上限,大部分区域在109~1011Ωcm。同时可清楚看出,电阻率分布很不均匀,不同区域间电阻率相差几个量级,这与高纯半绝缘碳化硅材料的固有属性一致[13]。

2.2 杂质浓度的SIMS测试

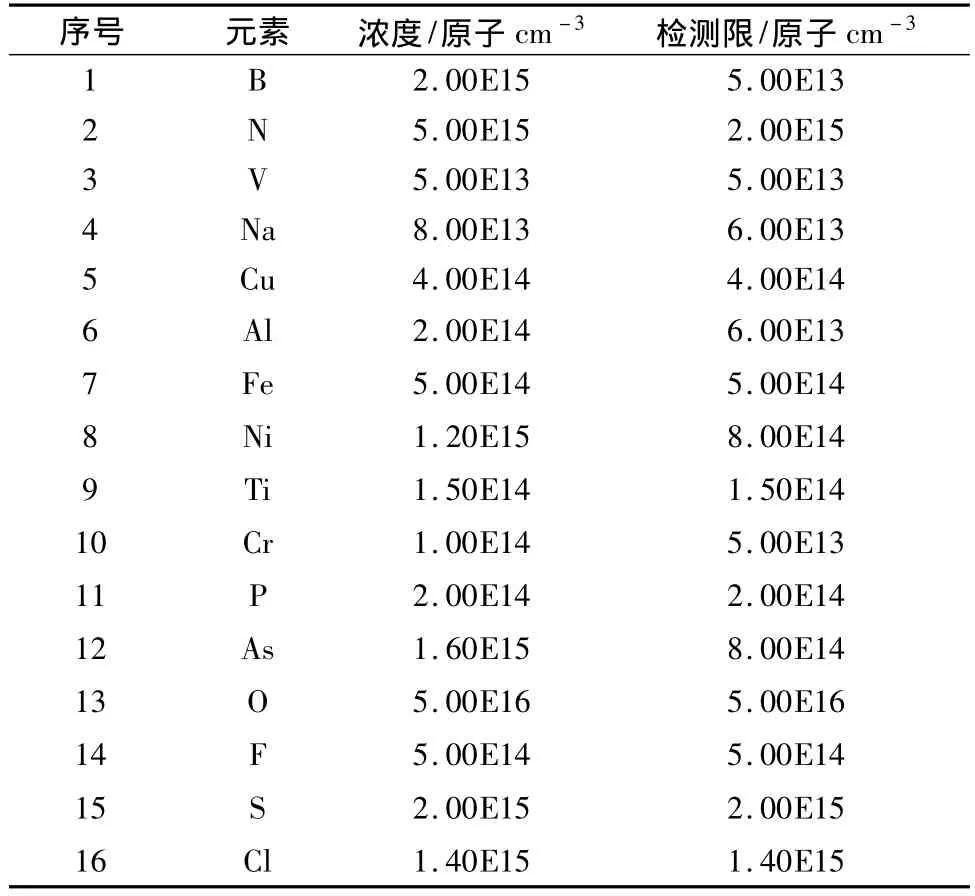

取23号晶片进行SIMS测试,测试前对该晶片进行了研磨和抛光,切取5 mm×5 mm小片多枚,表面溅射金膜后待测。测量在两台法国CAMECA公司二次离子谱仪上进行,型号分别为 IMS-4F和IMS-4F E7,采用和两种一次离子源,用灵敏度因子(RSF)法计算浓度。

对于氮、硼、铝、钒四个关键元素,采用离子注入法定标的方式测试,其他元素采用与CREE公司高纯4H-SiC样品对照的方式测试,结果见表2。从表中可见:第一,氮的浓度达到5×1015cm-3,说明其降低到了被深中心完全补偿的水平[14];第二,其他受主(或可能的受主)元素的浓度,如硼、铝、钒等都远低于氮的浓度,由此可以判定,该样品为深中心补偿形半绝缘碳化硅,即高纯半绝缘碳化硅。

表2 SIMS测量样品中杂质浓度及检测限

2.3 样品的EPR测试

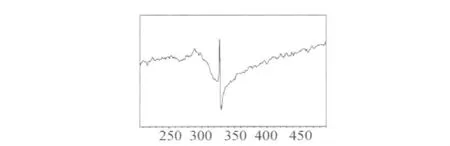

测试样品取自用于SIMS测量的相同晶片,研磨、抛光加工后,切取3.3 mm×5 mm小样片。测试仪器为日本电子株式会社JES-FA200电子顺磁共振波谱仪。测量温度110 K,微波频率9.503 GHz,磁场平行于C轴,结果如图5所示。

图5 高纯6H-SiC电子顺磁共振图谱

图5与N.Y.Garces等[15]测量高纯半绝缘碳化硅EPR图谱相似,图谱中心的峰为带正电荷的碳空位。这与Son N.T.等[14]研究高纯半绝缘碳化硅退火稳定性行为的结论也是一致的,即碳空位、碳空位-碳反位对是高纯半绝缘碳化硅主要深受主中心。

3 结语

研究证实了Son N.T等人的研究结果,碳空位、碳空位-碳反位对在碳化硅中形成深受主能级,可以补偿浅施主能级,从而使所生长的碳化硅材料呈半绝缘导电特性,二次离子质谱(SIMS)检测和非接触电阻率Mapping测试(COREMA)证明了这一结果。

在高纯半绝缘碳化硅材料工艺制备中,尽可能避免氮占碳位,在禁带中形成浅施主能级;另一方面,适当浓度的碳空位是形成深受主能级补偿施主能级使材料形成半绝缘导电的重要条件,因此工艺参数的选择要综合考虑。

设计PVT生长温度和压力等工艺参数,可以控制生长前沿碳硅比和氮占碳位的几率,从而控制生长过程中氮的进入,为实现HPSI工艺生长创造有利的条件。

[1] BICKERMANN M,WEINGARTNER R,WINNACKER A,et al.On the Preparation of Vanadium Doped PVT Growth SiC Boules with High Semi-insulating Yield[J].Journal of Crystal Growth,2003,254(1):390-399.

[2] ZVANUT M E,KONOVALOV V V,WANG H Y,et al.Defect Levels and Types of Point Defects in High-purity and Vanadium-doped Semi-insulating 4H-SiC[J].Journal of Applied Physics,2004,96(10):5484-5489.

[3] HAO J M,WANG L J,FENG B,et al.The Relationship Between Resistivity and Compensation Ration in Vanadium-doped 4H-SiC Grown by PVT Process[C]//13th ICSCRM 2009,Nurnberg,Germany,2009.

[4] NABIL SGHAIER,JEAN-MARIE BLUET,ABDEL KADER SOUIFI,et al.Study of Trapping Phenomenon in 4HSiC MESFETs:Dependenceon Substrate Purity[J].IEEE Transactions On Electron Devices,2003,50(2):297-302.

[5] HAO J M,WANG L J,FENG B.Growth of 2-Inch V-Doped bulk 6H-SiC with High Semi-Insulating Yield[J].Journal of Electronic Materials,2010,39(5):530-533.

[6] 王利杰,冯玢,齐海涛,等.3英寸半绝缘4H-SiC单晶的研制[J].半导体技术,2011(1):8-10.

[7] IRMSCHER K.Electrical Properties of SiC:Characterisation of Bulk Crystals and Epilayers[J].Materials Science and Engineering,2002(B91-92):358-366.

[8] HEYDEMANN V D,SCHULZE N,BARRETT D L,et al,Growth of 6H and 4H SiC Single Crystals by the Modified Lely Process Utilizing a Dual-seed Crystal Method[J].Appl.Phys.Lett.1996,69(24):3728-3730.

[9] PONS M,BLANQUET E,DEDULLE J M,et al.Thermodynamic Heat Transport and Mass Transport Modeling of Sublimation Growth of Silicon Carbide Crystals[J].J.Electrochem Soc.,1996,143(11):3727-3735.

[10] LILOV S K.Study of the Equilibrium Processes in the Gas Phase During Silicon Carbide Sublimation[J].Mater.Sci.Eng.,1993(B21):65-69.

[11] GLASS R C,HENSHALL D,TSVETKOV V F,et al.SiC Seeded Crystal Growth[J].phys.stat.sol.(b),1997(202):149-162.

[12] 4H Silicon Carbide Substrates N-type,P-type,and Semi-Insulating[EB/OL].[2010-05-10].http://www.cree.com/products/pdf/MAT-CATALOG.pdf.

[13] MACMILLAN M F,MITCHEL W,BLEVINST J,et al.Evaluation of Test Methods Employed for Characterizing Semi-Insulating Nature of Monocrystaline SiC Semiconductor Materials[C]//CS MANTECH Conference,Chicago,Illinois,USA,2008:14-17.

[14] SON N T,CARLSSON P,GALLSTROM A,et al.Prominent Defects in Semi-insulating SiC Substrates[J].Physica B,2007,401-402(1):67-72.

[15] GARCES N Y,GLASER E R,CARLOS W E,et al.Behaviour of defects in Semi-insulating 4H-SiC After Ultrahigh Temperature Anneal Treatments[J].Physica B,2007(401-402):77-80.