铜互连氮化硅薄膜沉积技术中电压衰减的研究

2011-02-26桂鹏,汪辉

桂 鹏,汪 辉

(上海交通大学,上海 200000)

1 引言

在现今0.13 μm以下的深亚微米集成电路制造中,后道金属互连工艺在连线的线宽缩小的同时,既要保证半导体器件互连之间的隔离效果,还要承受比以往更高的电流密度。若采用AlCu合金材料作为连线,容易出现由电迁移效应引发的器件可靠性问题。与AlCu合金材料(95% Al-5%Cu)相比,纯铜材料由于具有更低的电阻、更好的抗应力/抗电迁移等显著优点。铜被广泛地应用于0.13 μm以下的深亚微米后道互连工艺中。

然而,铜(或铜离子)易在介电层中扩散,会对介电层产生污染,并且在相同条件下铜离子的扩散速率远大于原子的扩散速率。铜(或铜离子)的扩散对于器件的性能和介电质的可靠性来说是致命的,这种扩散将会导致铜连线之间的电压衰减,如图1所示,有两种可能的漏电通道。

因此在大马士革铜互连制造工艺中,如何消除铜原子(离子)在介电层中的扩散、在阻挡层和介质层的界面上的扩散都是铜互连工艺所面临的一个挑战。在中国内地的第一条后道铜互连生产线的芯片制造实践中,我们遇到0.13 μm和0.09μm的产品在后道铜互连工艺中发生金属层间介电质漏电造成器件失效的问题。我们针对图1所示的两种漏电方式的机理作了深入研究,在不增加新制程和工艺成本的基础上,通过研究,优化了阻挡层(氮化硅)薄膜沉积工艺,解决了后道铜互连电压衰减问题。

2 实验

2.1 大马士革铜互连VBD失效机理

在0.13 μm以下的深亚微米制程中,大马士革铜互连工艺采用氟硅玻璃作为介质层形成对铜线的支撑与阻隔。沉积氟硅玻璃前,一层薄薄的氮化硅薄膜(约30nm~50nm)会被预先沉积在铜的表面。它充当着阻止铜穿透介质层的作用,在铜互连工艺整合中至关重要。虽然嵌入式铜互连得到极大的发展,但是从嵌入结构的制程来看,现今大多用硅烷作为原材料来制备氮化硅。在化学机械抛光后,铜直接暴露在空气中,极易被氧化生成氧化铜。如果在接下来的氮化硅沉积前,氧化铜没有被去除干净,在等离子的轰击下,会产生以下两种危害;第一,铜离子在介质层中扩散;第二,铜离子污染氮化硅和前一层电介质的界面。这两种情况都会造成铜连线之间的导通,引起器件失效。实验显示,最高测试电压为100V时候,有4片晶圆在测试电压低于20V时,就发生失效的例子。

从微观来看,铜连线加上电压后,会产生一个类似于平行板电容器的电场(铜作为金属板),如图2所示。由于氮化硅的介电常数比金属层间介电质的介电常数大,所以图1中1处的电场强度要大于2处。这时候,如果氮化硅沉积时,有铜离子存在于氮化硅和介质层界面上、或者铜离子污染层间介电质,则极易造成铜互连的失效,如图3所示。研究表明,在氮化硅和层间介电质的界面上存在的导电离子(大多是铜离子)是造成铜互连VBD失效的主要原因。这些铜离子产生在氨等离子体预处理以去除氧化铜的过程中,一些铜离子被等离子体轰击到层间介电质上,而在氮化硅预沉积前没有被去除干净;或者是在氮化硅预沉积过程,没有很好地预防控制从NH3Treatment过渡到沉积步骤时,铜硅化物(Copper Silicidation)的形成,如图4所示。

3 试验优化设计

我们选择常见的5层铜连线的产品,在每一层的氮化硅沉积前,都会分成9个不同的子批,分别进行9种不同工艺参数组合条件下的氮化硅沉积。在氮化硅预沉积这个步骤里,根据3种不同的硅烷流量、射频率和预沉积的时间,具体如表1所示。这里仍然用大写的字母代替实际的参数设定值。

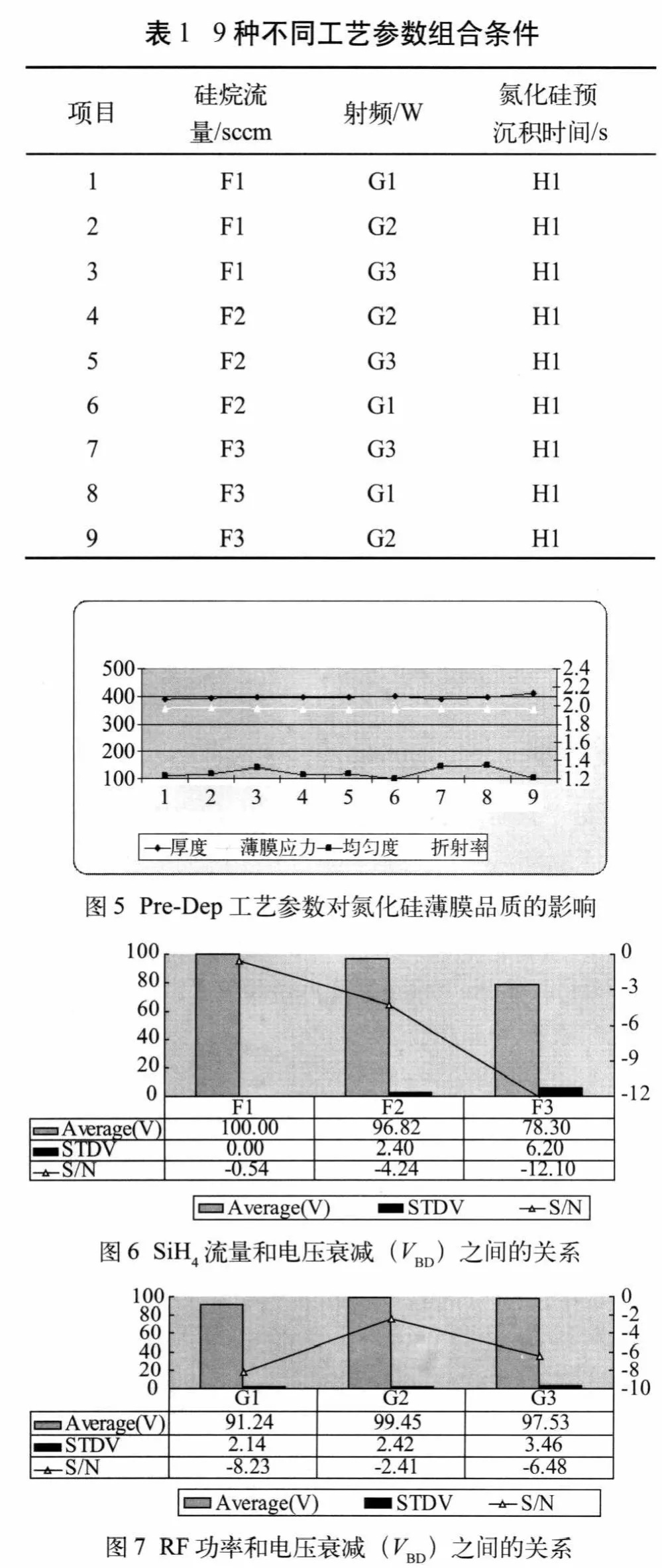

在第四层铜经CMP后,我们收集了氮化硅薄膜沉积前在控片上沉积的氮化硅,然后量测厚度(THK)、折射率(REF)、薄膜的均匀度(uniformity)和应力,如图5所示。

从图5可以看到改变Pre-dep的三个工艺参数(硅烷流量、RF功率和Pre-dep时间)不影响氮化硅薄膜的品质。

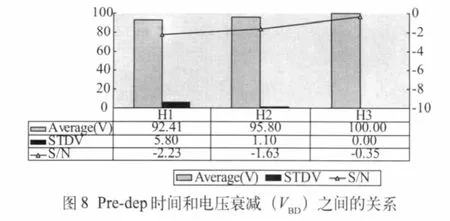

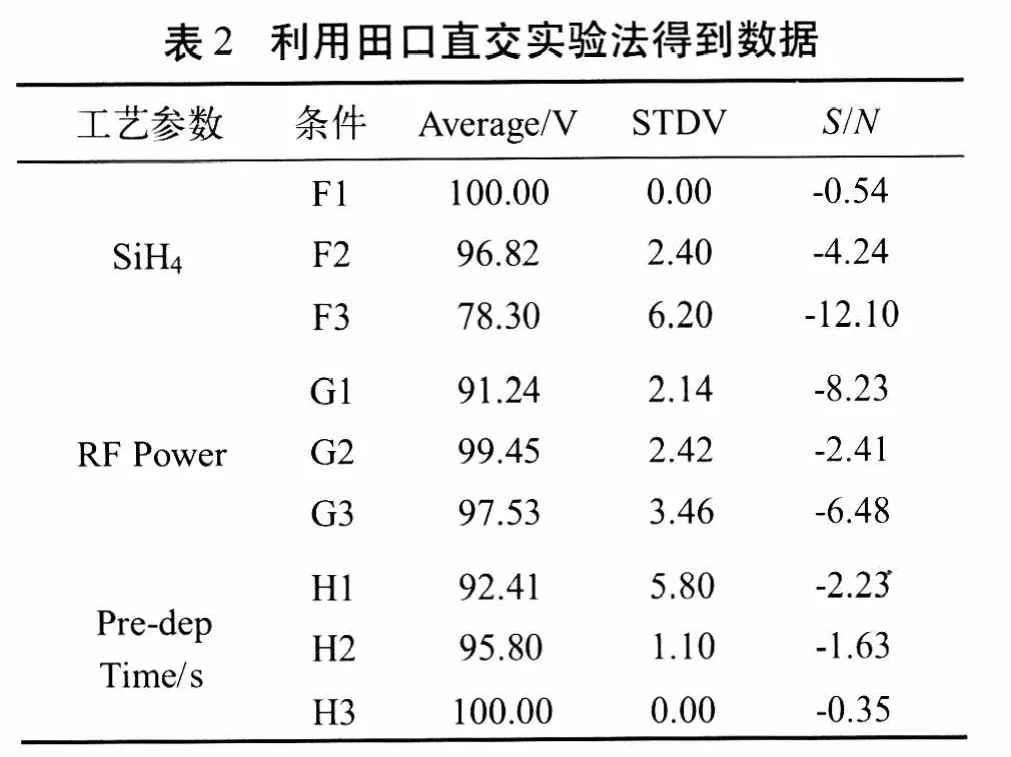

当所有的5层铜连线后和正常的产品一样,经过高温退火,然后去测试这9片晶圆的VBD数值。图6~图8分别是硅烷流量、RF功率的大小和Pre-dep的时间长短对于VBD的影响关系。

可以看出SiH4的流量F1,得到的VBD可达100V,并且此时得到的信躁比(S/N)最大。SiH4的流量是F3时,VBD不到80V。这说明Pre-dep中的硅烷如果流量过大,有少量的硅烷没有被等离子体分解,会和铜反应生成铜的硅化物,可以说Pre-dep步骤中,改变硅烷的流量对于VBD的影响很大。

(1)往来款项核算的变革。在目前实行会计制度的规定下,必须用收付实现制核算高校的资金往来。但是新的会计准则下,高校资金往来必须以权责发生制为基础进行会计核算,高校在期末要对有关应收款和预付款等进行减值测试,采用账龄分析法等对这些账目进行分析,对于可能发生减值的要计提坏账准备。对往来款项进行管理,可以使得反映在账面上的资产价值更加真实。

可以看出RF的功率G2,得到的VBD最好,并且此时得到的信躁比(S/N)最大。试验说明,如果RF功率过大,会在反应腔的showerhead孔洞里面发生micro-arcing,这也会造成VBD失效。

可以看出RF的功率H3,得到的VBD最好,并且此时得到的信躁比(S/N)最大,这说明pre-dep时间H3足以保证在从NH3treatment过渡到Dep的过程中,没有铜的硅化物生成。

综合图6~图8的数据,利用田口直交实验法,可以得到表2。

根据表2,在Pre-dep这一步,最优的氮化硅沉积的参数组合硅烷流量(F1)、RF功率(G2)和Predep时间(H3)。

4 硅烷流量过冲的研究

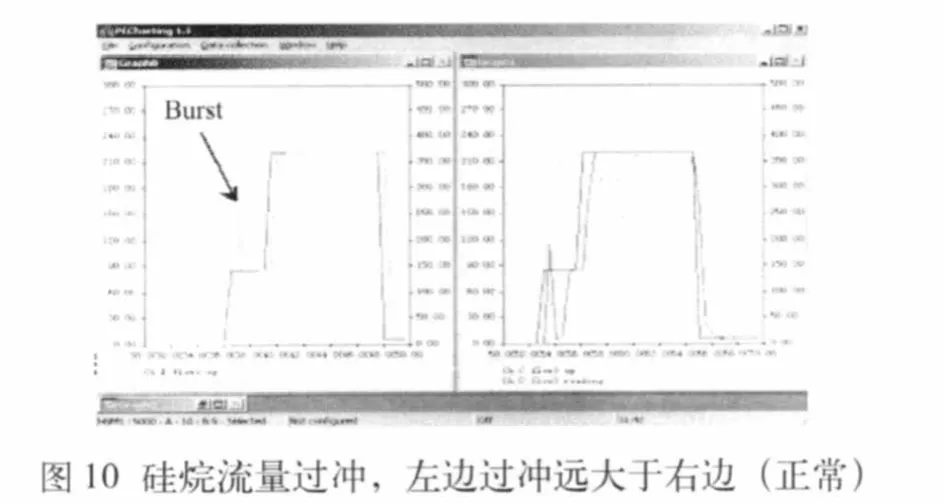

由大马士革铜互连的分析可知,在氮化硅沉积过程中,如果硅烷的流量过大(任何的MFC都有过冲),则没有被电离的硅烷,会在高温下分解成SiH2会和铜反应,生成铜的硅化物。图10显示出SiH4的流量瞬时过大造成的VBD失效。

由图9看到整片晶圆上一共测试30处的VBD,最大值仅有44.46V。失效分析的TEM表明在氮化硅和层加电介质的界面存在有铜的硅化物。

由此我们可以得出,在氮化硅的沉积过程中,由于机台硬件的损坏,造成硅烷流量的过冲,也是导致VBD失效的一个原因。除了定期更换新的MFC或维修外,我们调整了氮化硅沉积的工艺参数,使机台的软硬件更好的工作。从而避免了这样的过冲造成的VBD失效。

5 结论

综合分析上面的三组实验,结合实际生产经验和实验结果,我们认为NH3Treatment和Pre-dep是造成VBD失效(层间介电质沿着图3中1处漏电)的主要原因。

首先,NH3Treatment的目的是去除CMP抛光后,暴露在空气中形成的氧化铜。NH3在等离子体的作用下分结成化学活性很高的NH2-、H+、H等,其中氢将还原晶圆表面的氧化铜。

CuO+2H→Cu+H2O

一旦氧化铜被去除干净,表面剩下的铜原子将直接面对等离子体的轰击而得到能量,如果这种能量大到能够使得铜原子脱离原本的结构,那么铜原子就会被溅射到旁边的FSG或反应腔的其他区域(如showerhead),这也是氮化硅工艺中经常会看到腔体内气体喷淋头上有铜残余的原因。但是总体来说铜被溅射到FSG表面的几率要远远大于溅射到showerhead去。这样铜原子到达FSG表面后,由于它本身的活性,只要一点点的能量,就能造成铜原子在FSG表面扩散。Cu被FSG区域性分离后,就像FSG中的F一样被隔离起来,此时没有较高的活性。但是随着氮化硅沉积工艺第三步过程中硅烷的介入,铜将会形成铜的硅化物(Copper Silicidation),从而恢复活性,造成VBD失效。图11所示为NH3Treatment时,晶圆表面局部的等离子体去除氧化铜的示意图。

另一方面,我们可以优化Pre-dep的参数来防止从NH3treatment过渡到Dep过程中产生铜的硅化物。

到此,我们对氮化硅沉积优化的组合是,在NH3Treatment步骤中RF功率(E1)和NH3Treatment的时间(D1),在Pre-dep步骤中硅烷流量(F1)、RF功率(G2)和Pre-dep时间(H3)。

[1]AMAT. PECVD 200 mm Best Known Method(BKM)Process Recipes[M].2002.

[2]R Rung, H Momose, Y Nagakubo. Deep Trend Isolated CMOS Devices[C].IEEE Int. Electron Device Meeting, 1982.

[3]J Paraszczak, et al. High Performance Dielectrics and Processes for ULSI Interconnection Technologies[C].IEEE Int.Electron Device Meeting, 1993.

[4]E H Nicollian, J R Brews. MOS Physics and Technology[M]. New York:Wiley, 1982.

[5]A C Adams,. Dielectric and Polysilicon Film Deposition[M]. New York:McGawHill, 1983.

[6]H N Yu, et al. 1 μ m MOSFET VLSI Technology:PartIAn Overview[C]. IEEE Trans. Electron Devices, 1979.

[7]C L Hu, J M Harper. Copper Interconnections and Reliability[J].Matt. Chem. And Phy., 1998, 52(5).

[8]P C Andricacos, et al. Damascene Copper Electroplating for Chip Interconnects[C].193rd Meeting of The Electrochemical Society, 1998.

[9]J M Steigerwald, et al. Chemical Mechanical Planarization of Microelectronic Materials[M]. New York:Wiley, 1997.

[10]T Homma.Low dielectric constant materials and methods for interlayer dielectric films in ultra-large-scale integrated circuit multilevel interconnects[J]. Materials Science and Engineering, 1998,23(243).

[11]J S Martin, K J Taylor, J D Luttmer, et al. FSG Process Development for CopperDamascene Technology[J]. IEEE,2001.

[12]Y L Cheng, Y L Wang, et al.Characterization and reliability of low dielectric constant fluorosilicate glass and silicon rich oxide process for deep sub-micron device application[C].Thin Solid Films, 2001.

[13]L M Cook, et al. Throretical and Practical Aspects of Dielectric and Metal CMP[C].Semiconductor International,1995.