基于FPGA的扩频警报信号处理器的设计

2011-01-24吕实诚

齐 鹏,张 宇,任 滨,吕实诚

(哈尔滨理工大学 测控技术与通信工程学院,黑龙江 哈尔滨 150080)

防空警报系统是人民防空的重要一环,不仅仅体现在警报器数量的多少、警报网的覆盖情况是否良好,也体现在警报控制系统能否通过信号处理器接收有线和无线信道传来的各种警报信号,准确地发放各类警报,能正确将警报器工作状态及接收到的各种信号,通过数据编码和加密,经有线或无线信道回传控制中心或控制分中心。显然目前的基于窄带通信技术的警报通信系统已满足不了人防警报对其通信的可靠性和抗干扰的要求。随着扩频通信技术及大规模集成电路、现场可编程器件的飞速发展,为建立抗干扰、可靠新高的警报控制系统创造了条件。

文中以扩频通信为理论基础,以FPGA作为中央控制器的核心,设计了人防警报控制系统中的警报信号处理器。

1 系统模型

射频警报信号经过天线接收下来后,经过混频器和中频滤波器滤波后通过A/D采样,把模拟中频信号转化为数字信号,送入FPGA内对信号进行数字化处理,后续处理包括数字下变频、数据解扩、伪码同步、载波同步、数据解调等。

扩频警报信号处理器结构如图1所示。

图1 扩频警报信号处理器结构框图Fig.1 The block diagram of spread spectrum alarm signal processor

2 系统硬件电路设计

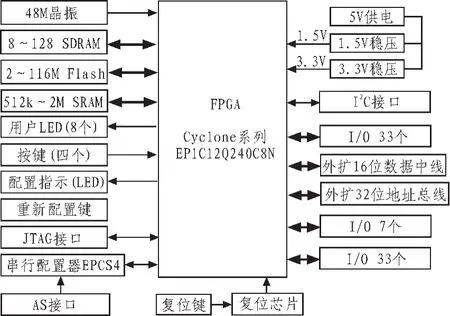

本设计的主芯片选用Cyclone系列的EPlC12Q240C8N,它的硬件资源足以满足设计需要。

2. 1 硬件总体设计

主控单元由CycloneTMEP1C12Q240的及其外围电路组成,EP1C12Q240是整个系统的核心,设计时即包括了基本的硬件资源又扩展了存储器。设计的FPGA电路原理框图如图2所示,电路板的硬件资源使用了CycloneTMEP1C12Q240的FPGA器件;两片2 MbytesNorFlashMemoryAT49BVl63AT-701M×16 bit.两片512 k 字节的 SRAMIS61LV25616AL(256 k×16 bit);两 片 16位总线8 Mbytes的SDRAMK4S641632H;串行配置器件EPCS4。AS接口,通过AS接口可直接对EPCS器件快速编程;JTAG接口,可下载配置到FPGA、调试程序、Flash编程、也可对EPCS器件编程;带I2C接口的E2PROM的复位芯片CAT1025SI-30。

图2 FPGA电路原理框图Fig.2 Block diagram of FPGA circuit

2.2 电源设计

本设计的FPGA芯片所需的3.3 V电源直接由5 V电源经过3.3 V低压差线性稳压器LDO芯片SPX1117-3.3并且滤波以后得到,见图3所示。3.3 V用于给FPGA所有I/O口、核心板上存储电路、串行配置器件、复位电路、LED等供电。

图3 电源电路Fig.3 Power supply circuit

2.3 复位电路设计

本文设计的复位电路如图4所示,复位电路使用了带I2C存储器的电源监控芯片CAT1025JI-30,复位门槛电压为3.0~3.15 V,提高了系统的可靠性。CAT1025包含1个精确的VCC监控测电路和2个开漏输出:RESET和RESET;当Vcc低于复位阈值电压时。CAT1025还含有一个写保护输入(WP),如果WP连接高电平,则写操作被禁止。

图4 复位电路Fig.4 Reset circuit

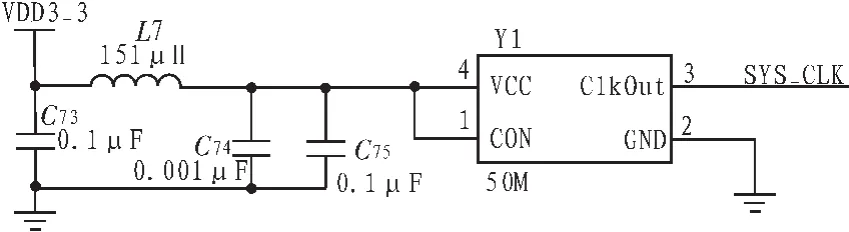

2.4 时钟电路设计

考虑到FPGA内部没有振荡电路,使用有源晶振是比较理想的选择。EPlC6Q240C8的输入的时钟频率范围为15.625~387 MHz,经过内部PLL电路后可输出15.625~275 MHz的系统时钟。当输入时钟频率较低时,可以使用FPGA的内部PLL调整FPGA所需的系统时钟,使系统运行速度更快。设计中注意PLLl使用的是CLK0或CLKl的时钟输入,而PLL2使用的是CLK2或CLK3的时钟输入。一个48 MHz的有源晶振,作为系统的时钟源,电路如图5所示。

图5 晶振电路Fig.5 Crystal oscillator circuit

2.5 Flash存储器的设计

设计中使用2片2 Mbytes的Flash(AT49BVl63AT-70 1 M×16 bit),AT49BVl63AT-70是 ATMEL 公司的 16 Mbytes的Flash。由于使用16位总线接口,可采用Avalon总线的动态对齐方式,要将AT49BVl63AT-70的A0连接到地址总线的A1AT49BVl63AT-70 的 47(n BYTE)、14(n WP)脚均接有一个10 kΩ的上拉电阻,AT49BVl63AT-70不采用字节方式,不进行写保护。电路中对芯片的片选信号线进行了上拉,这样可有效提高芯片工作的可靠性。如图6所示。

为了避免总线上其它的总线型外设在不使用时因意外而造成总线冲突,应将这些外设的片选都上拉(低电平有效时)或下拉(高电平有效)。

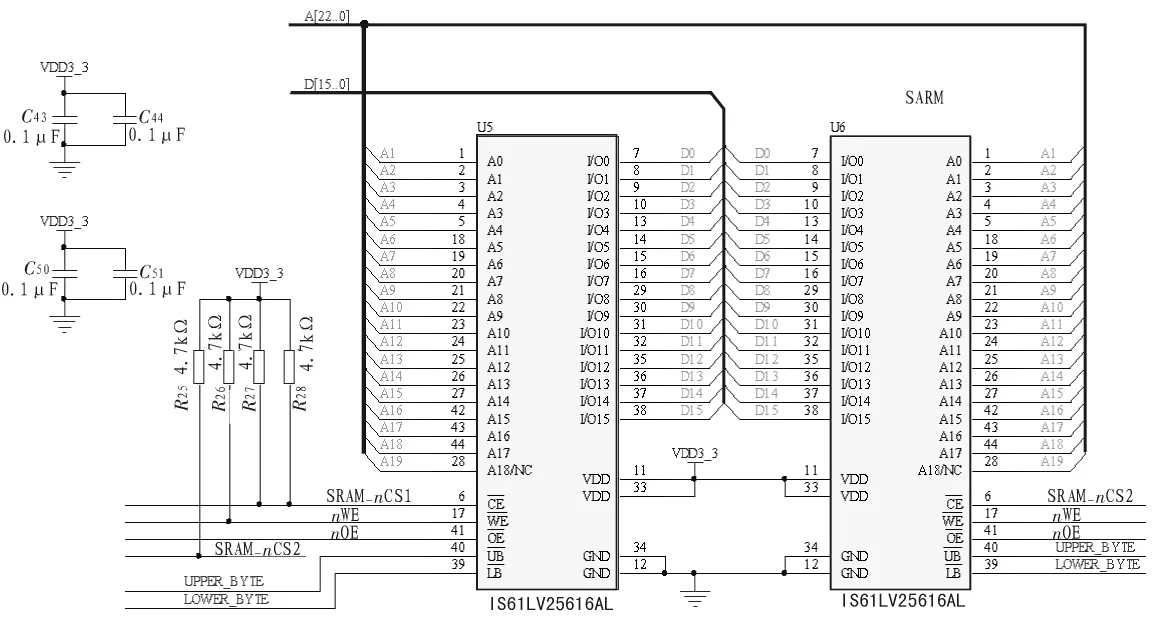

2.6 SRAM设计

SRAM的28 (A18) 脚 用 于 1M字 节 容 量 的IS61LV51216AL。电路中2片SRAM的片选信号独立,数据总线、地址总线、读写信号线n OE和n WE都与Flash共用,并且也与所有挂在总线上的总线型外设主板上的液晶以及外扩总线共用。如果需要使用两片SRAM,则在SOPC Builder中要添加两个SRAM核。2片SRAM的片选信号分别为SRAM_nCS1和SRAM_nCS2。如图7所示。

2.7 串行配置器件设计

Cyclone系列FPGA是基于SRAM查找表技术的FPGA,在器件上电时配置数据必须重新加载。因此必须使用掉电保持的器件来保存配置数据,然后在FPGA上电时将配置数据加载到FPGA中去。串行配置器件具有包括ISP和通用FLASH存储器访问接口等先进特性。如图8所示。串行配置器件设计采用了非常容易使用和连接的3.3 V 4脚接口,并且配置电流小,等待模式时功耗接近于0。EPCS4采用8引脚小外形封装,串行配置器件可重复编程100,000次以上,可通过USB下载电缆、Ethemet Blaster以及ByteBlaster下载电缆对其进行在线编程,也可以通过EPCS的专用数据下载接口AS接口EPCS编程。

3 单元模块功能VHDL实现

3.1 解扩部分实现

VHDL部分语言描述如下:

P1:process(clock_set)variable i:integer:=0;

begin

if(r='1')then

if(clock_set'EVENT AND clock_set='1')then

图6 Flash存储电路图Fig.6 Flash memory circuit

图7 SRAM电路Fig.7 SRAMcircuit

result<=receivecode XOR pn(i);

i:=i+1;

if(i>7)then i:=0;

end if;

end if;

end if;

end process P1;

3.2 解调部分实现

VHDL部分语言描述如下:

P2:process(clock_set)

begin

if(clock_set'EVENT AND clock_set='1')then

q0<=receive_code;

z1<=receive_code XOR q0;

图8 串行配置器件EPCSFig.8 EPCs serial configurat device

end if;

end process P2;

4 结 论

本文利用扩频通信技术和FPGA技术完成了人防警报信号处理器的设计,并对硬件电路设计进行了详细说明,最后用VHDL语言描述了相关功能。本设计满足了人防警报系统现实的需求,对以后人防警报系统的升级有着重要意义。

[1]裴红伟,杨明极,李冬明.扩频通信系统的FPGA实现[J].电子技术,2007,7(6):68-71.PEI Hong-wei, YANG Ming-ji, LI Dong-ming.Spread spectrum communication system based on FPGA[J].Electronic Technology,2007,7(6):68-71.

[2]查光明,熊贤祚.扩频通信[M].西安:西安电子科技大学出版社,2005.

[3]樊昌信.通信原理[M].北京:国防工业出版社,2001.

[4]魏莉.基于扩频的二次人防警报遥控系统的研究[D].哈尔滨:哈尔滨理工大学,2003.

[5]李虎.一种扩频通信调制器的FPGA设计与实现[J].今日电子,2008,8(12):41-43.LI Hu.A design and implementation of spread spectrum communication modulator based on FPGA [J].Electronic Products,2008,8(12):41-43.

[6]张浩.FPGA原理、设计与应用[M].天津:天津大学出版社,2004.