VDMOS器件总剂量辐照阈值电压影响因素分析

2010-12-22赖于树

熊 燕 赖于树

(重庆三峡学院物理与电子工程学院,重庆万州 404100)

VDMOS(Vertical Double-diffused Metal Oxide Semiconductor)器件通过微电子工艺实现了现代应用对电子设备使用过程中的高压大电流的要求,其独特的垂直导电沟道结构使其具有承受电压和电流能力强、输入阻抗高、开关速度快、频率特性稳定等一系列优点,目前广泛应用在战略武器技术、核技术以及空间技术中等功率器件领域.[1]基于此,构成这些电子设备的VDOMS器件不可避免的要处于各种空间带电粒子、射线以及核辐射等强辐射环境中.辐射粒子会与器件相互作用,导致VDMOS器件电学参数发生变化,如开启电压(VT)漂移、跨导(gm)退化、亚阈漏极电流(IDsub)增加、周期噪声(1/f)增加、击穿电压(VBR)降低等等.[2]严重的时候会导致VDMOS器件功能失效,进而导致整个电子设备不能正常工作.

因此,对于 VDMOS器件辐照效应的研究以及如何提高其抗辐照能力具有至关重要的意义.本文从VDMOS结构及工作原理出发,分析了栅源电压和辐照温度对VDMOS器件总剂量辐照条件下阈值电压漂移的影响.

1 器件结构及工作原理

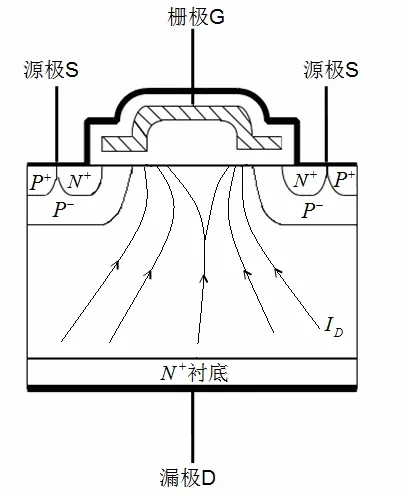

图1为功率VDMOS器件的纵向结构剖面示意图,集成VDMOS器件多个六角形元胞并联组成,多晶硅网格结构将各个元胞的栅极连到一起并埋在源金属电极的下面,二者以SiO2层隔开,导通时电子流经过表面有源区的导电沟道流到 区,然后垂直向下流动.VDMOS工作时栅源电压大于开启电压VT,半导体表面水平沟道会形成强反型层,也就是形成电子流动的导电沟道,此时在漏源电压VDS形成电场的作用下源区电子会以一定的速度漂移,经过外延层直至衬底形成漏极电流ID,如图1箭头所示.如果加在VDMOS栅极和源极之间的电压小于开启电压,则表面反型层无法形成,此时的漏源之间就是一个处于截止状态的PN结,由于耗尽层的存在,漏源之间可以维持一个较高的阻断电压.

2 实验方案

实验采用常规VDMOS器件,器件结构如图1所示,硅衬底材料为偏置电压,实验采用P型辐温度,实验采用N型,电阻率为2Ω⋅cm,采用2μm 的硅栅工艺制备,氧化温度为 850℃,栅氧化层厚度为tox=70n m .沟道长度为3μm .VDMOS器件总剂量辐照阈值电压漂移实验通过60Co源进行,它是稳态辐射源产生射线有两个能量.实验中使用的γ射线的剂量率为0.023gay(Si)/s,由LSC601型剂量计给出,辐照源为类点源,辐照总剂量的标定采用剂量传递的方法,通过重铬酸银剂量计来进行标定.辐照实验通过改变偏置电压和改变辐照温度两个方面来进行.

图1 VDMOS纵向结构剖面及电流ID示意图

3 VDMOS器件总剂量辐照阈值电压影响因素分析

大量研究表明,辐照对功率VDMOS的影响主要是产生氧化物陷阱电荷和界面态电荷.氧化物陷阱电荷通常由氧化物本身的缺陷所形成,一般来说它是属于电中性的,但由于电子和空穴在SiO2绝缘层中的迁移率不同,空穴易于被深空穴陷阱俘获而成为正空间电荷,其结果会使器件电容器的平带电压和阈值电压向负方向移动;界面态位于 Si-SiO2交界处,它的产生不仅使器件阈值电压改变,还会使泄漏电流快速增长以及沟道区载流子的迁移率降低.综合考虑二者,得到阈值电压的变化可以表示为:[3]

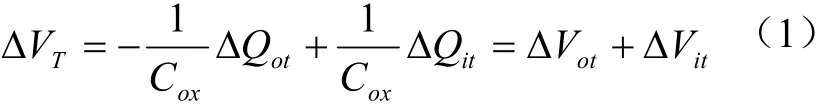

式中,△Qot表示辐照在器件单位面积产生的正空间电荷,△Qit表示辐照产生的界面态电荷,△Qot是辐照后正空间电荷引起的阈值电压变化,△Qit是辐照后界面态电荷引起的阈值电压的变化.

图2是单极型场效应晶体管在典型的实验辐照源情况下的阈值电压随总剂量辐照漂移曲线,由该图可以看出阈值电压漂移和辐照总剂量的函数关系是:P型MOS管总剂量增加,阈值电压单调降低;对于N型MOS管的阈值电压,在总剂量偏小时总剂量增加阈值电压会减小,而当总剂量增加到一定值后,总剂量增加阈值电压也会增加.

图2 VDMOS阈值电压与辐照总剂量的关系

3.1 栅源电压对阈值电压漂移的影响

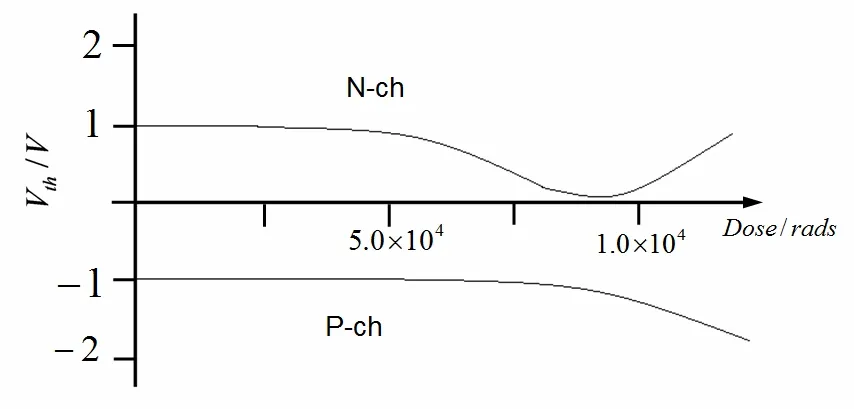

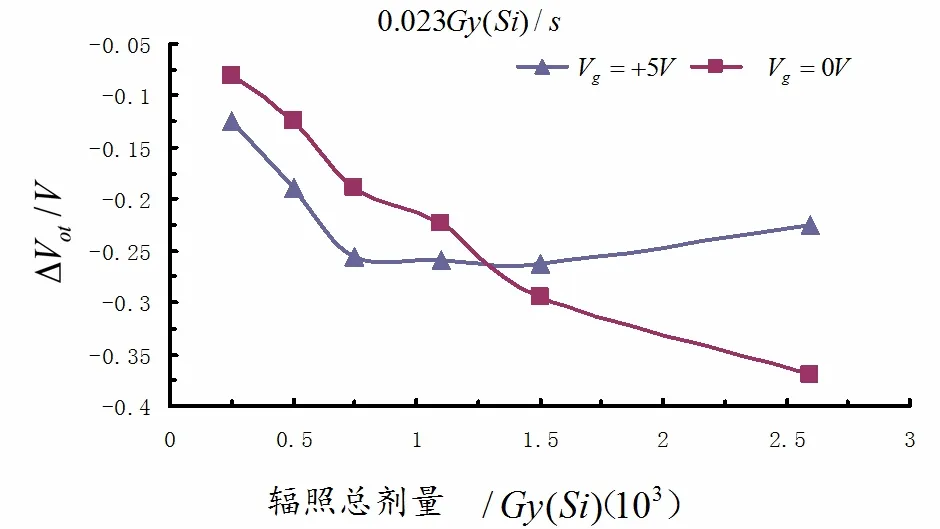

VDMOS受到辐照时栅源电压起着分离和加速感生电子空穴对的作用,在电场作用下,电子和空穴运动方向相反,栅压为正时,电子快速漂向栅极;空穴缓慢漂向 SiO2/Si界面并在通过陷阱区时被陷阱俘获从而建立起正氧化层空间电荷.利用半带电压法[4]将辐照引起的阈值电压的漂移量△Vth分为△Voh和△Vih两部分,从对PVDMOS器件进行不同偏置情况下总剂量辐照效应阈值电压影响的实验数据曲线如图3、4、5所示.

图3 PVDMOS管不同偏置电压△Vth与辐照总剂量关系

图4 PVDMOS不同偏置电压△Vit与辐照总剂量的关系

图5 PVDMOS不同偏置电压△Vot与辐照总剂量的关系

由图3可知,在剂量率为0.023Gy(Si)/s辐照条件下,随着偏置电压Vg和辐照总剂量的增大,器件阈值电压的漂移与其同相变化.通过用平带电压法分离不同电场强度条件下辐照引起阈值电压漂移△Vot、△Vit得到图4和5,由图可知界面态陷阱电荷对阈值电压漂移的影响是负相的,而氧化陷阱电荷引起的阈值电压的漂移变化则比较复杂:当偏置电压较低时由于电场强度原因,电子空穴对的分离不充分并且复合较为严重,建立氧化物电荷密度较小,当偏置电压达到一定值时,此时电场度增强导致电子空穴对复合变弱而分离增强,故△Vit随着之同相增大;当偏置增大到一定数值时,由于陷阱的空穴俘获面积减小等原因,会在界面附近紧靠陷阱区域中形成一个无氧化电荷区域,所以加栅压小的器件△Vot会随着总剂量的增加而增大,此时偏置大的器件△Vot已趋于饱和.

该实验表明,对于低剂量率的总剂量辐照效应,偏置对其阈值电压漂移的影响主要决定了辐照过程中电子空穴对的产生、分离和复合的速度以及空间正电荷的运动速度,而偏置电压不同对辐照效应的影响还要受器件界面态建立速度的制约.阈值电压移动会随外加栅极电压值同相变化,而且正栅压下的移动会大于负栅压下的移动,因为紧靠Si-SiO2界面所形成的正空间电荷层对表面能带弯曲所产生的影响,远远大于栅极附近形成的空间正电荷层时所产生影响.因此,氧化物电荷与辐照正栅极电压的关系有可分为:增长区、饱和区和一个下降区.经过辐照后,在外加栅极电压作用下,测量阈值电压或平带产生的移动在室温下恒定不变.

3.2辐照温度对阈值电压漂移的影响

前面讨论了偏置对VDMOS器件总剂量辐照阈值电压漂移的影响,这些分析都是基于室温情况下得来的规律.以N沟道MOS的阈值电压为例有:

大量参考文献表明,在很宽的温度范围内,QOX和φMS几乎与温度没有关系,因此(2)式中与温度密切相关的只有衬底的费米势φFP,将VT对温度T取导数得:

其中,φFP对T的导数为:

将(4)代入(3)得到

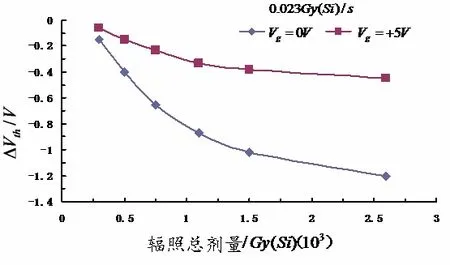

式5中NC、NV、EG与温度关系不大.因此,在考虑辐射对VDMOS器件阈值电压漂移影响时,辐照温度是必须要考虑的问题之一.诸多实验表明,高温辐照规律与室温辐照大致相同,而低温辐照条件下由于氧化层电荷的面宽度比室温下大得多,并且几乎平均分布在整个SiO2绝缘层内,因此其阈值电压漂移与室温不同.笔者选用了常用的N沟道功率VDMOS集成电路进行辐照温度对阈值电压漂移影响的实验,同时,得到实验数据曲线如图6、7、8所示:

图6 NVDMOS不同温度下△Vth与辐照总剂量的关系

图7 NVDMOS不同温度下ΔVit与辐照总剂量的关系

图6是不同温度辐照下△Vth的总剂量关系(实验取了两个温度-30度和27度),图7和图8是不同辐照温度条件下,△Vot、△Vit与总剂量的关系.

图8 NVDMOS不同温度下△Vot与辐照总剂量的关系

由图7和图8可知,当辐照温度降低时,器件界面态的陷阱电荷引起的阈值电压漂移量同相降低,而氧化物陷阱电荷引起的量却增加.基于以上实验分析,我们得到结论,温度对半导体器件辐照引起阈值电压漂移量△Vth,主要是温度的高低决定了界面态建立速度的快慢,主要是由于温度不高时,SiO2中的辐射感生的非平衡的空穴是固定不动的,随着温度的升高,因而界面态建立的速度变快,需要时间变短.

4 结 论

本文对常规硅栅功率VDMOS器件进行了不同偏置电压和不同辐照温度的总剂量辐照效应实验,对实验样品进行了阈值电压漂移的测量,并对获得的数据进行了讨论,得到实验结论如下:对于低剂量率的总剂量辐照效应,偏置不同对辐照效应的影响还要受器件界面态建立速度的影响,阈值电压的漂移与外加栅极电压值同相变化,而且正栅压下漂移大于负栅压;而总剂量辐照时温度降低会导致器件界面态形成速度趋缓,故低温辐照使得阈值电压漂移更加严重.

[1]Taylor.Power MOSFET Design[M].New York:John Wiley & Sons,1993,1-15.

[2]LHOY H,KIM K Y Radiation effects on the power MOSFET for space applications[J].ETRI Journal, 2005,27(4):449-452.

[3]李泽宏,张磊,谭开洲.总剂量辐照加固的功率VDMOS器件[J].电子科技大学学报,2008(7):621-623.

[4]J.W.Schrankler, R.K. Reich,M.S.Holt,D.H.Ju,J.S.T.Huang and G. D.Kirchner CMOS scaling implications for total dose radiation[J].IEEE Trans.Nucl.Sci.,1985,32:3988.