基于CPLD的ARINC429总线接口系统设计

2010-09-05屈凌翔单悦尔

屈凌翔,单悦尔,杨 兵

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

基于CPLD的ARINC429总线接口系统设计

屈凌翔,单悦尔,杨 兵

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

文章首先简单介绍了ARINC429航空总线的应用背景和总线传输协议的基本内容。然后根据ARINC429航空总线标准的要求,提出一种基于ACTEL公司CPLD的透明数据传输系统方案。在QUARTUSⅡ和MODELSIM的设计平台上,该系统成功实现12路ARINC429信号接收和4路ARINC429信号发送的功能,每个通道都包括32×8的数据FIFO,ARINC429字长为32位,主机接口采用16位,429数据速率支持12.5 kbps与100 kbps,数据传输实时可靠,能较好地满足ARINC429通信系统的要求。该电路系统采用正向设计,Verilog HDL硬件语言描述,ACTEL公司A3P250VQG100I实现,规模十四万门左右,采用VQFP100封装,双电源设计,功耗低至0.4W,能较好地满足工业级电路系统低功耗的设计要求。

ARINC429总线;接收发送系统;透明传输;复杂可编程逻辑器件

1 前言

ARINC429数据总线是美国航空无线电公司制定的一种民用航空标准数据总线。它作为波音、空中客车、麦道等飞机上机载计算机及导航设备之间信息交联的主要总线,在我国民用、军用飞机上也被普遍采用。通常ARINC429总线数据传输的接口电路设计都是采用专用芯片实现的,这就使接收发送的通道数量和储存数据的缓存受到限制,并且价格昂贵,尤其不适用于需要备份关键数据的系统。本设计利用CPLD内部丰富的资源,可以增加数据通路,并且使存储容量得到很大提高,同时有效地缩小系统体积,降低成本。模块化设计也使系统的配置灵活度有很大提高。

2 ARINC429总线传输协议

ARINC429 数字信息传输规范阐述了通过一对屏蔽双绞线(数字数据总线)从一个端口向其他系统和设备以串行方式传输数字数据信息的方法。系统规定,在一对传输线上,不允许双向传输数据信息。系统所传输的数据或者是采用二进制表示法(BNR)编码的,或者是采用二一十进制(BCD一二进制编码的十进制)表示法编码,而且字母和数字是根据ISO-5字母编码发送的。这种由源系统提供的数据具有很高的速率,所以能保证数据更新值的微小变化。传输是按“开环”(数据单向流动)方式进行,奇偶校验位(第32位)作为每个数字字的一部分来发送,以便数据接收端进行简单的勘误和数据合理性检验,这样可防止显示错误或可疑的数字字。

ARINC429的发送速度有100kbps和12.5kbps两种,在同一总线不得将两种速度混用,采用了双极回零调制,发送出去的脉冲有三个电平,即高电平(+15V),0电平(0V)、低电平(-15V)。高电平为逻辑1。字与字之间以一定间隔(4位)分开,此间隔作为字同步。数据传输是以电脉冲形式发送的,一个电脉冲就是1位。1个数字字(32位)被分为5段,即标志码(label),第1~8位,源/目的地识别码(SDI);第9~10位:数据区(data);第11~29位:符号状态位(SSW);第30~31位:奇偶校验位(parity);第32位。

3 多通道ARINC429总线接口系统设计

该系统提供有ARINC429标准航空串行数据和16bit宽数据总线:包括4个独立发送通道、12个独立接收通道和可选择操作方式的可编程控制器。每个发送器电路包括一个发送缓存器和一个逻辑控制器,发送缓存器是一个8×32bit的FIFO,而控制逻辑则允许主机给发送器写数据块,并通过主机使能发送器使该数据块自动发送出去。而每一个接收通道包括一个接收缓冲器和一个控制逻辑,接收缓存器是一个8×32bit的FIFO,控制逻辑则完成对接收数据的检测并同时使能主机是否进行读取操作。系统还支持中断工作方式,支持100kbps和12.5kbps串口数据速率,QFP100封装,电源电压3.3V,内核电压1.5V,采用ACTEL公司的A3P250VQG100I器件实现。系统功能实现框图如图1所示,系统主要由发送数据编码器、接收数据译码器、发送缓冲器、接收缓冲器、系统时序控制器、控制和标志寄存器以及主机接口控制器组成。

3.1 时钟产生电路

将系统输入的10MHz时钟信号10MCLK分频成内部电路需要的100kHz时钟、12.5kHz时钟、200kHz时钟、25kHz时钟、200k×25Hz时钟、25 k×16Hz时钟,供内部各个功能部分分别使用。

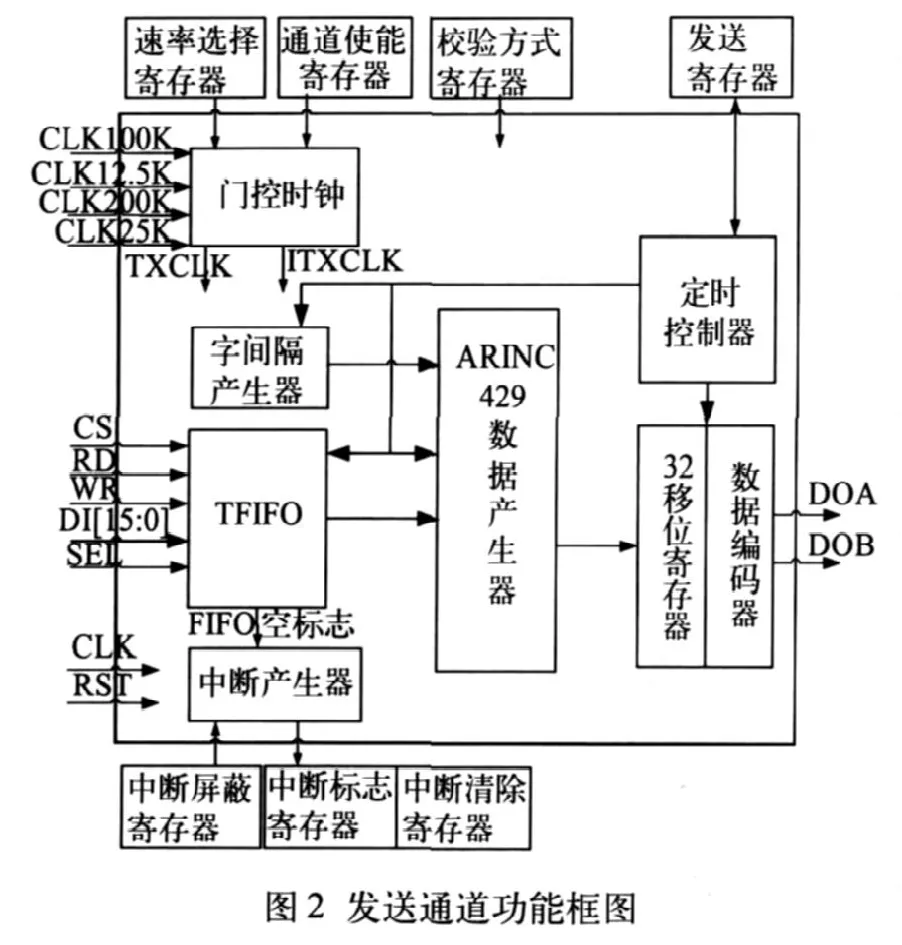

3.2 发送部分电路

发送通道包括数据间隔产生器、发送器定时器、中断产生器、输出移位寄存器和数据编码器等电路(如图2所示)。其中外部模块8×32bit FIFO可由用户进行操作(如装载、使能、非使能等)。首先主机接口控制器通过FIFO地址选通在FIFO不为满的情况下把32bit的ARINC数据并行装载入FIFO中,当FIFO满时则禁止继续写入数据。而当数据发送信号有效时(由主机控制字控制)则FIFO移位时钟被激活,数据被串行移到发送器驱动器上,当FIFO数据发送完为空时则产生中断通知主机继续数据的写入,继续新一轮的数据发送。

基本工作流程为:首先是当FIFO为空时通知主机把一组数据写入FIFO,然后主机写入发送命令后发送通道依次读出数据,最后按照ARINC429字数据格式整理数据并按从低位到高位的顺序发送出去;当发送完一组数据后发送状态寄存器自动清零,并产生FIFO空中断通知主机把另一组数据写入FIFO,再次写入发送命令把数据发送出去。

3.3 接收部分电路

接收通道包括接收器定时器、数据时钟、同步检测器、数据译码器、奇偶校验控器、SDI校验器、输入数据寄存器等电路(如图3所示)。其中外部模块8×32bit FIFO可由用户进行操作(如读取、使能、非使能等)。如果新数据到了,首先进行同步处理判断,如判断同步则进行接收数据并进行奇偶校验,如果数据没有错误则被写入FIFO。而当FIFO为满标志时则禁止接收通道进行写入;只要FIFO有数据则产生中断以通知主机进行读取,而当FIFO为空时中断自动消失。

基本工作流程为:首先是进行数据同步检测,如果成功则进行数据的各种校验处理(奇偶校验/字间隔校验),如果同步检测和数据校验都没有问题则把接收到的数据写入FIFO并产生中断通知主机读取,否则将继续检测数据同步信号或者丢弃错误数据转而重新进行数据的接收处理。当FIFO为满时将禁止接收通道写FIFO,FIFO为空时也禁止主机进行读取操作。

3.4 代码设计与实现

电路设计采用Verilog HDL硬件描述语言编写,在ACTEL公司的A3P250VQG100I器件中实现(如图4所示)。

代码描述部分如下:

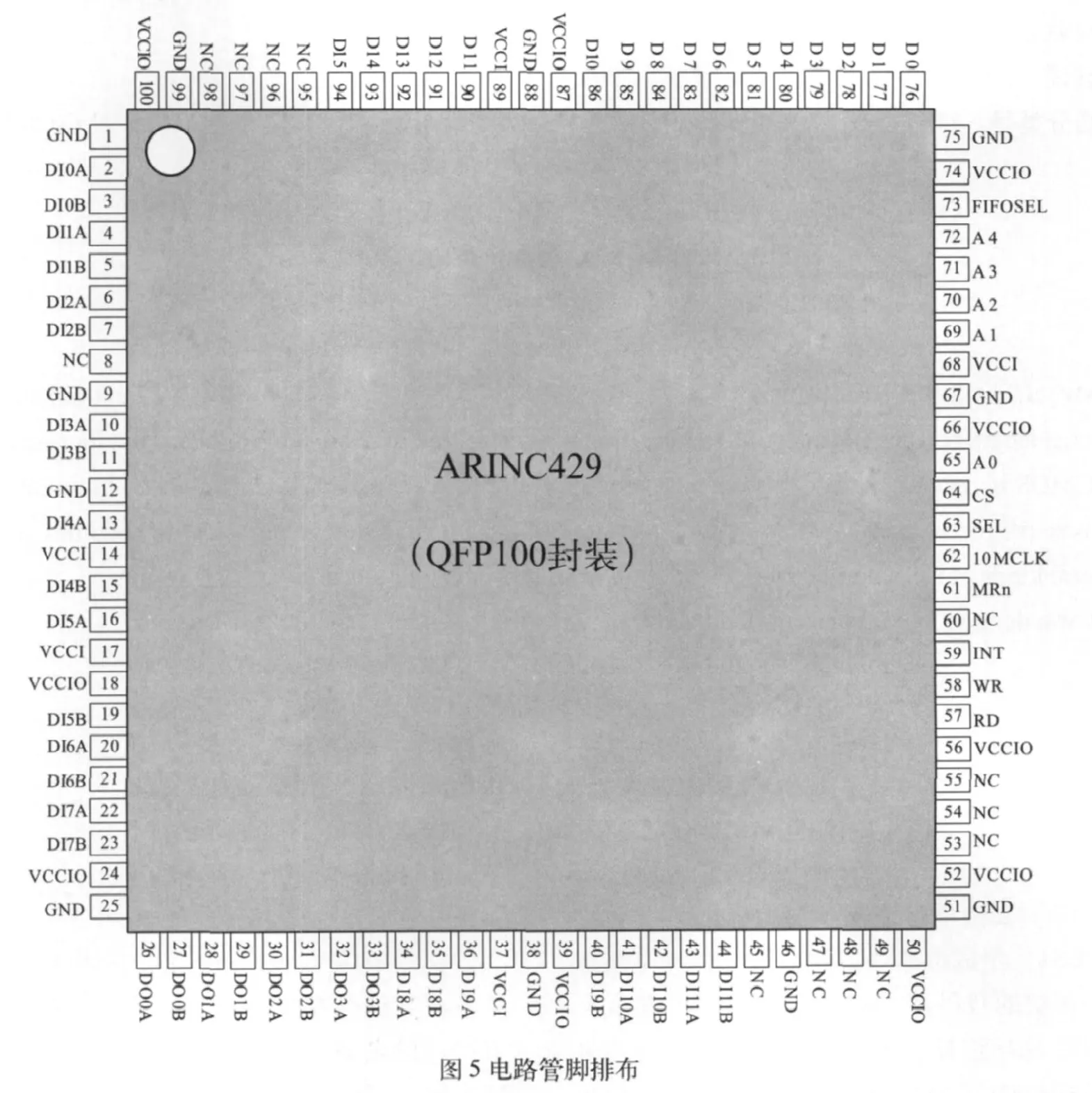

ARINC429系统CPLD实现电路端口顺序描述如图5所示,采用QFP100封装,电源电压3.3V,内核电压1.5V。

4 结束语

该数据传输系统采用了时钟使能设计方案,在QUARTUSⅡ和MODELSIM的设计平台上,成功实现了4发12收的ARINC429总线接口电路,该电路可同时在多个通道下独立地传输两种总线数据。同时该系统还具有良好的可靠性、通用性和可扩展性,实用价值很高。

[1]徐景硕.基于8位单片机的ARINCA29总线接口[J].电子技术,2001,(8):29-31.

[2]王六顺,刘文波,党万胜,等.基于DSP的ARINC429通信板的研制[J].电子技术应用,2000,26(12):47-49.

[3]DEI公司.DEI1016 datasheet[S].2000.

[4]宋万杰,罗丰,吴顺君.CPLD技术及其应用[M].西安:西安电子科技大学出版社,1999.193-198.

The Design of ARINC429 Bus-interface System Based on CPLD

QU Lin-xiang , SHAN Yue-er, YANG Bing

(China Electronic Technology Group Corporation No.58Research Institute,Wuxi214035,China)

The paper introduces the application background of ARINC429 bus and the base content of the protocol. Then a scheme of a transparent data transmission system in accordance with ARINC429 bus standard is proposed based on CPLD,in which twelve input-channels and four output-channels of ARINC429 have been realized by the EAD platform of quartus and modelsim. Each channel includes 32×8 bits FIFO and sustains 12.5kbps and 100kbps data rate. This system still holds a 16-bit-host-interface and ARINC429 word is 32 bits. The data can be transmitted reliably in real-time,and it has been demonstrated that the scheme has fulfilled requirements of ARINC429 communication system quite wel1. The system is realized by Verilog HDL in the device A3P250VQG100I of ACTEL,which includes 400 thousand gates and is packeged by VQG100.The industrial system uses double powers in accordance with low-power-design, therefore its power-consume is only 0.4W.

ARINC429 bus; receiving/transmitting system; transparent transmission; CPLD

TN402

A

1681-1070(2010)09-0024-04

2010-06-29

屈凌翔(1981-),男,浙江人,毕业于电子科技大学,现在中国电子科技集团公司第58研究所九部从事大规模集成电路设计与研究工作。