Simulink在“频率合成”课程自主性实验中的应用

2010-08-23杨路刚刘宏波李丽华

杨路刚,刘宏波,李丽华

(海军工程大学电子工程学院,湖北武汉 430033)

0 引言

频率合成技术是一门在通信、雷达等许多领域得到广泛的应用的科学。目前国内许多大专院校都开设了频率合成相关技术的课程。作为一门与工程应用紧密结合的课程,通过实验教学可使得学生的应用能力、动手能力和创新能力得到极大的锻炼。

频率合成技术的发展经历了直接式频率合成、锁相式频率合成与直接数字式频率合成三个阶段[1]。直接数字式频率合成DDFS代表了频率合成领域新兴的发展方向。现在,DDFS已成为“频率合成”课程中非常重要的一部分。

在“频率合成”课程的实验中,关于DDFS的部分比较多的方案是采用Analog公司的985X系列集成芯片[2]进行演示。学生可以用示波器观察输出信号的波形,或用频率计测量输出频率。这种方法的唯一可控对象只有输出信号的频率(或波形),对于各种中间信号的产生和变换过程是无法观察到的,学生难以理解整个合成信号流程和形成机制。由于实验偏向于演示性,学生参与的机会不多,学生的积极性不易提高。虽然国内一些高校开设了FPGA硬件实现DDFS的实验课程[3],但所需课时较多。

为了更好地使学生理解直接数字式频率合成的机理,我们认为采取计算机仿真实验的方法是可行的。本文基于软件[4]建立了一个DDFS仿真模块,可作为直接数字式频率合成的自主性仿真实验平台。

1 直接数字式频率合成

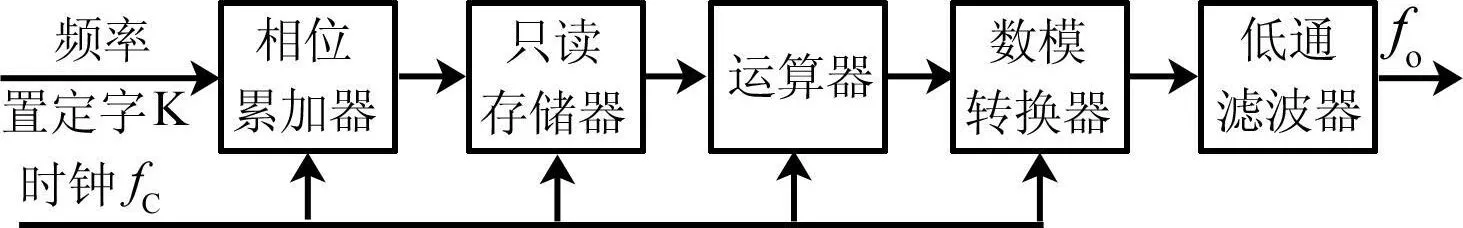

图1为基本的直接数字式频率合成器的框图。

图1 直接数字式频率合成器组成框图

直接数字式频率合成器由相位累加器、只读存储器、运算器、数模转换器和低通滤波器等五个基本单元组成[5]。

以最常见的正弦性直接数字式频率合成器为例,其工作过程如下:

(1)相位累加器在时钟fc的每个周期内累加上由频率置定码K设定的相位增量;

(2)累加的相位量在只读存储器中进行查表,得到在各采样点的输出信号幅度值;

(3)此幅度值通过运算器输出相应幅度的数字脉冲,经数模转换器变换为数字阶梯波;

(4)数字阶梯波经低通滤波器平滑滤波后输出设定频率 f0的正弦连续波。

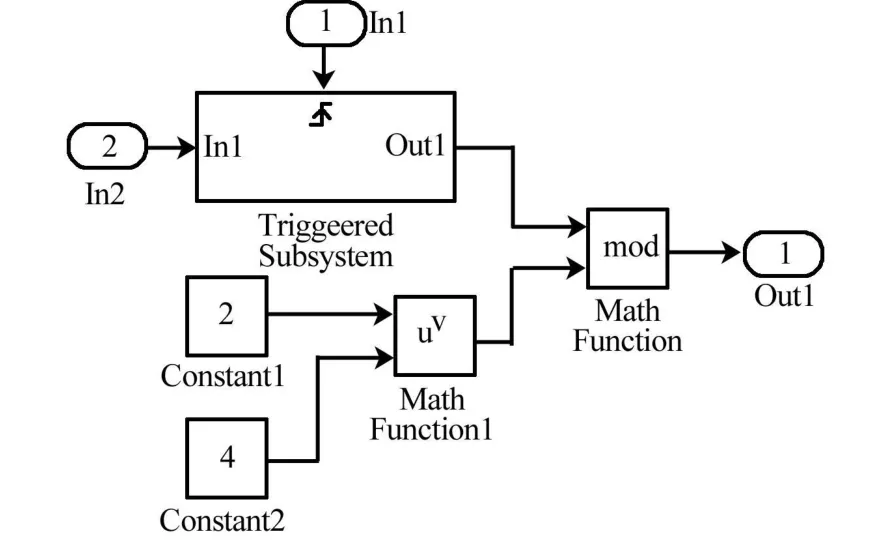

根据上面阐述的工作机制,设相位累加器的字长为M,亦即累加2M/K次到达满量,完成一个输出信号的周期,于是可计算出合成器的输出周期T0和输出频率:

在实际电路中,频率置定字K一般是由寄存器给定的。通过改变K,合成器就可以得到不同的输出频率 f0。

2 仿真设计

2.1 仿真模型

在Simulink环境下搭建的DDFS仿真模块如图2所示。

图2 DDFS的Simulink仿真模块

该模块主要由脉冲发生器子模块(Pulse Generator)、频率置定字子模块(Control word)、相位累加器(Phase Accumulator)子模块、查找表子模块(ROM Table)、低通滤波器子模块(Analog Filter Design)和方波转换子模块(Relational Operator)等组成。

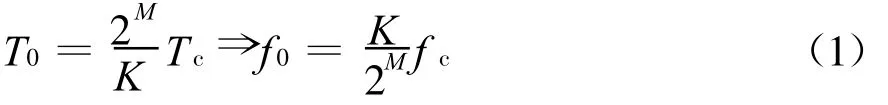

2.2 相位累加器子模块

相位累加器子模块是整个模块设计的关键,其核心是触发子系统(Triggered Subsystem),如图3所示。

图3 相位累加器子模块组成

触发子系统属于Ports&Subsystems库[6],是一个可直接受时钟脉冲触发控制的子系统。其中定义了一个S函数(用户自定义函数),作用是在时钟脉冲的控制下周期性累计常量K。

触发子系统输出的累加量应当是周期性循环的。如果相位累加器的字长M取为4,则累计器计数应以24=16为周期。这里的做法是通过一个数学函数,对累加数取模16的余数作为输出。输出信号类型(Output signal type)设置成real,采样时间(Sample time)设置成跟随触发子系统的时钟。

2.3 查找表子模块

查找表使用的是Lookup Tables库中的“Direct Lookup Table(n-D)”模块,该模块可以配置成标量、矢量或矩阵元素类型的查找表。

将查找表维数(Number of table dimensions)设为1,从查找表中选择输入数据方式(Inputs select this object From table)设置为选择元素(Element)。由于累加器字长为4,在不考虑截断误差的情况下,ROM表中应包含24=16个元素值(相位值)。

在幅度归一化,即量化区间为[0,1]的情况下,相位值与对应幅度值的关系如表1所示。

表1 相位值与幅度值的对应关系

2.4 低通滤波器子模块

低通滤波器选用巴特沃思型[7]。为了提高合成信号的稳定度选择阶数为3,也可选用其他类型的滤波器。

分析阶梯波的频谱组成,应当选取截止频率比较低的低通滤波器使得平滑效果较好,但此截止频率又必须保证输出信号能够顺利通过。根据低通采样定理,输出信号的频率最大值 fomax=fC/2,故选取最佳截止频率为 fC/2,能够保证对于不同的频率置定字K电路都能正常工作。

对于一些需要方波输出的场合,可以再通过一个比较器,参数取为0。当输出正弦波处于正半周期时,输出为高电平(1),处于负半周期时,输出低电平(0),即可起到正弦波整形为方波的目的。

3 仿真结果

为了检查此仿真模型能否正常工作,可通过设置不同的K值和时钟频率来进行验证。以K=1为例,此时输出频率的理论计算值 fo=K×fc/2M=1×30/16=1.875 MHz。在Model Property中对模块赋初始值:K=1,fC=30MHz,利用16个相位点的正弦幅值直接作为查表数据(即不考虑量化误差);

进行仿真后,观察各显示模块。图4为输出信号fout的波形,其频率为1.875MHz,与理论计算值完全吻合。设置其他的输入条件,也能得到相同的结论,证明了该仿真电路可以正常运行。图5为经过正弦信号整形后输出的方波波形。

图4 输出正弦波波形

图5 输出方波波形

通过仿真还可以观察到DDFS电路各中间信号的变化。图6显示的是相位累加器输出波形,为一周期性数字阶梯波;图7显示的是ROM输出波形,为接近于正弦的周期性波形。这些信号在以往的硬件电路实验中是观测不到的。

图6 相位累加器输出波形

图7 ROM输出波形

在此仿真模块的基础上,学生可以充分发挥想象力,做出一些改进。如改变ROM存储的幅度值,可以实现锯齿波和三角波等不同类型的信号输出;如增加移相的子模块,可以研究如何用DDFS实现调频信号发生器;如增加用于截短二进制码的子模块和频谱分析子模块,观察各级控制字的截短对DDFS输出相位舍位噪声和有限字长效应噪声[8]带来的影响。在硬件实验中,由于受到外围电路等硬件条件和教学课时的限制,这些研究往往是难以进行的。

在实验中,学生通过选择子模块、设置参数来搭建直接数字式频率合成器的过程中可以认识到电路各部分的作用,通过对中间信号的观察加深了对电路工作机制的理解。通过修改仿真模块进行各种研究提高了学生的积极性。可见,基于Simulink的仿真实验可作为“频率合成”课程硬件实验之外的一种很好的补充。

[1] 周冬成,曹旭峰,王永斌.锁相与频率合成[M].北京:国防工业出版社,2005

[2] 刘伟,胡仁杰,王峥.基于 AD9850芯片的信号发生器的研究[J].苏州:电工电气,2009,(11):19-22

[3] 李文渊,陈红林,束海泉.直接数字频率合成器的教学实验[J].南京:电气电子教学学报,2002,24(5):64-66

[4] 钟麟,王峰.M ATLAB仿真技术与应用教程[M].北京:国防工业出版社,2004

[5] 许小俊,谢克明,闫高伟.DDS在Simulink中的仿真设计[J].太原:太原理工学报,2006,37(2):154-157

[6] 高美珍,洪家平,程晓林.MAT LAB仿真在电子电路课程中的应用研究[J].武汉:高等函授学报(自然科学版),2006,19(5):6-9

[7] 李文磊,刘士荣,陈征,等.MA TLAB在自动控制理论实验中的应用[J].北京:实验技术与管理,2006,23(2):68-71

[8] 李志坚,曾大治,龙腾.DDS相位截断杂散分析[J].北京:信号处理,2009,25(11):56-59