一种LDO极零点跟踪的频率补偿电路设计*

2010-08-11杨林张涛

杨 林 张 涛

(武汉科技大学 武汉 430081)

1 引言

由于具有低输出噪声、低漏失电压、低静态电流、快速瞬态响应以及低成本等优点,LDO线性稳压器在高性能便携式设备,尤其是以电池供电系统中得到了越来越广泛的应用。传统的频率补偿方法是利用输出电容的等效串联电阻(ESR)产生一个零点进行补偿,以改善其稳定性,然而这种频率补偿方法并不是最佳的[1~3]。一方面输出电容的ESR会随温度变化而变化,导致引进的零点会漂移,达不到最佳补偿;另一方面,通常这种频率补偿方式的主极点在输出节点位置,而稳压器工作在较宽的负载电流范围,因此主极点在不同负载电流的情况下会有很大的变化,严重影响了环路的稳定性。本文提出了一种新颖的动态零极点跟踪频率补偿电路,使环路内部产生一个随负载电流变化的补偿零点。该零点用以抵消LDO系统内部主极点位置随负载电流变化给环路稳定性带来的影响,使得LDO线性稳压器的稳定性不受负载电流大小的影响[4]。

2 传统的LDO频率补偿方法

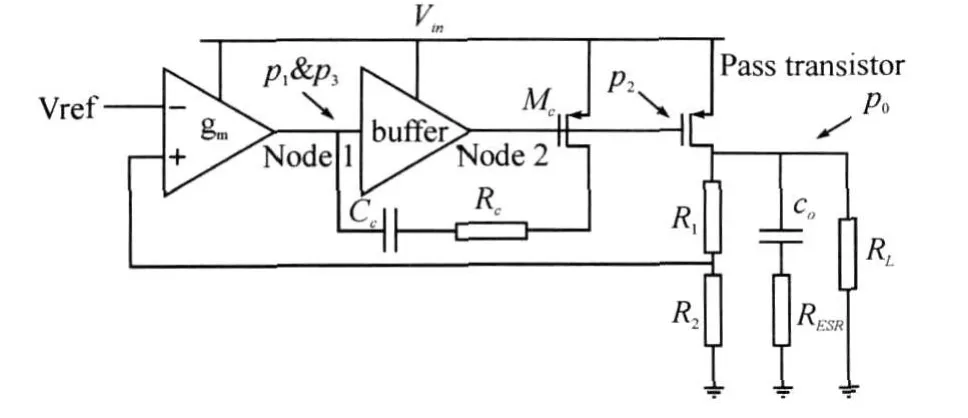

传统LDO稳压器的系统框图如图1所示,环路中存在三个极点,分别位于误差放大器输出端的极点p1,电压缓冲器的输出端的极点p2以及LDO输出端的极点po。这三个极点可分别表示为:p1=1/r1◦c1;p2=1/r2◦c2;,其中r1,c1,r2,c2分别表示节点1,2的对地电阻和电容。λ为调整管的沟道调制参数。通常p1,po为低频极点,位于单位增益带宽内。另外,环路中亦存在一个零点zESR=1/RESR◦co。

图1 典型LDO功能框图

传统的LDO就是利用这个零点来抵消 p1以保证环路的稳定性和足够的相位裕度,然而,如果RESR太大的话,则零点会处在低频位置,这样会导致环路的带宽增加,从而使三个极点均落于单位增益带宽之内,影响环路的稳定性;如果RESR太小的话,则零点会处在一个较高频率位置,零点会位于单位增益之外,补偿不到p1,从而在单位增益带宽内有两个没有补偿的极点,这样系统也不稳定。所以在一定负载条件下,RESR需要在某一范围内才能使环路稳定。此外,RESR还受到环境温度、电压和频率的影响,所以频率稳定性不能得到可靠的保障[5~7]。

3 跟随负载电流变化的动态频率补偿

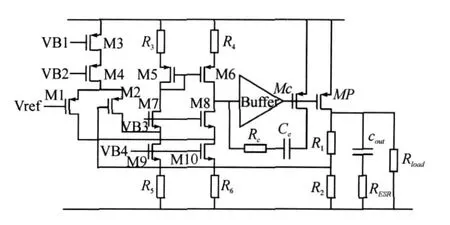

针对上述问题,本文提出一种跟随负载电流变化的频率补偿方式。其功能方框图如图2所示。

图2 改进频率补偿的LDO简化功能框图

图2与图1的主要区别是前者在后者的基础上增加了串联R,C网络(Mc,Rc,Cc)连在误差运放的输出结点作频率补偿。PMOS管Mc检测输出电流,并工作在深线性区,由于其漏源电压Vds=0,此时Mc作为一个电阻工作,其导通电阻为Ron=其中 VG S为Mc亦即PMOS调整管的栅源电压。又知PMOS调整管工作在饱和区,所以VG S-Vth=由于流过PMOS调整管的电流Ids与负载电流Iout几乎相等,即 Ids=Iout,因此可得当负载电流增大时,Ron减小,起到跟踪负载的效果。下面来分析环路的零极点情况,结点2和输出结点处的零极点与图1中的相同。我们重点研究结点1处的零极点。结点1处的零极点可表示为:zc=1/rc◦cc,p1=1/(r1+rc)◦cc,p3=1/(r1∥rc)◦c1。(通常 p1远小于 p3,c1远小于c3),其中rc=Rc+Ron。所以zc可用于跟踪并抵消掉LDO的输出极点po,p1变成了环路的主极点,p3是高频极点,对环路的稳定性影响很小。另外,p2仍处于高频位置。

4 电路实现

根据上述思想,设计了如图3的LDO电路。

图3 本文提出的动态补偿方案

其中M1~M10,R3~R6组成一个折叠式共源共栅运算放大器,构成LDO的误差运放部分,R3~R6使运放的输出阻抗更高,确保误差运放的输出位置为主极点位置。Mc为输出电流检测管,对输出电流进行采样,从而调整 Mc本身的可变电阻值,进而改变补偿零点位置,使之跟随输出极点的变化,从而实现动态补偿的目的。Buf fer一方面起到隔离误差运放与调整管的作用,使原本的由于调整管寄身电容引入的低频极点变为两个高频极点,从而改善环路的稳定性;另一方面,Buf fer能更快的驱动PMOS管的栅极,提高瞬态响应[8~10]。

5 仿真验证

该电路采用smic 0.35μ m CMOS工艺来实现。仿真结果如图4所示,在输入电压为4V,输出为 3V的条件下,扫描负载电流,从 0mA到100mA,整个系统相位裕度均在 65°以上,系统稳定。图5为典型应用条件下(50mA)环路频率响应曲线,环路的单位增益带宽为468kHZ,相位裕度为67°,环路稳定。图6给出负载电流从0mA变化到100mA的负载变化瞬态响应。从图中可以看出,瞬态响应过冲小于50mV,且没有振铃现象。

6 结语

在分析传统LDO稳压器频率补偿方法的基础上提出了一种新型的动态密勒补偿电路,与传统LDO利用ESR进行补偿的方法相比,该电路不仅结构简单、增益高、带宽高,大大提高了LDO稳压器的性能指标,而且大大降低了对外部电容的ESR要求,从而在提高性能的同时,降低了LDO稳压器的应用成本。

[1]毕查德◦拉扎维.Design of analog CMO S integrated circuit[M].西安:西安交通大学出版社,2003:309~327

[2]G.A.Rincon-Mora.Current efficient,low voltage,low drop-out regulators[D].Ph.D.dissertation,E-lect.Comp.Eng.Dept.,Georgia Inst.of Technol.,Atlanta,1996

[3]ESR,Stability,and the LDO Regulator[M].Texas Instruments,Dallas

[4]R.Reay,G.Kovas.An unconditionally stable twostage CMOS amplifier[J].IEEE J.Solid-State Circuits,1995,30(5):591~594

[5]K.N.Leung,P.K.T.Mok,W.H.Ki.A novel frequency compensation technique for low-voltage lowdropout regulator[J].Proc.IEEE Int.Symp.Circuits Systems,1999,5:102~105

[6]G.A.Rincon-M ora,P.Allen.Optimized frequency shaping circuit topologies for LDOs[J].IEEE Trans,Circuits Syst.II,1998,45(6):703~708

[7]Phillip E.Allen,Douglas R.Holberg.CMOS Analog circuit design[M].北京:电子工业出版社,2005:359~400

[8]R.Reay,G.Kovas.An unconditionally stable twostage CMOS amplifier[J].IEEE J.Solid-State Circuits,1995,30(5):591~594

[9]K.C.Kwok,P.K.T.Mok.Pole-zero tracking frequency compensation for low dropout regulator[J].2002 IEEE Inter.Symp.on Circuits and Systems(ISCAS'02),2002,4(5):735~738

[10]C.Stanescu.Buffer stage for fast response LDO[J].2003 International Semiconductor Conference,2003,2(9):357~360