基于FPGA的斯特林制冷机控制系统

2010-07-30傅雨田

朱 鹏 傅雨田

1 引言

近年来,斯特林制冷机在设计和工艺技术上都有了较大突破,尤其是分置式结构、间隙密封、柔性板弹簧支撑、线性直线电机驱动、主动减振等技术的突破使得斯特林制冷机获得快速的发展。由于斯特林制冷机具有工作范围宽、启动快、效率高、操作简便等优点,国内外已将斯特林制冷机广泛应用于空间领域[1]。

传统的斯特林制冷机控制系统,多采用单片机作为核心控制器件,这些控制器运算速度慢,抗干扰能力差,复位不可靠,存在程序“跑飞”的风险。FPGA内部是全并行体系结构,有着运行速度快、编程调试方便、集成度高等优点,非常适用于变频系统实现脉宽调制;且FPGA使用硬件实现运算,抗干扰能力强,不存在程序跑飞的风险;通过使用IP核,可以在FPGA内部模拟单片机结构,实现较复杂算法的运算,集成度高,方便快捷。

本设计针对进口的牛津型分置式斯特林制冷机,膨胀机采用气动式膨胀腔结构,压缩机采用对置式双直线电机结构,压缩机活塞与冷头排出器的运动相位差固定,压缩机工作频率固定为50 Hz。为了实现对其温度闭环控制,设计了使用FPGA作为核心控制器的制冷机控制方案,着重介绍对压缩机双直线电机的驱动控制。

2 控制系统结构

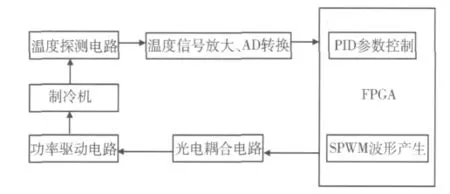

控制系统的核心控制器件采用Actel公司生产的ProASIC PLUS系列FPGA,负责总线接口、温度数据采集处理、PID控制算法的实现以及SPWM波形的产生。整个设计除温度测量电路外,全部由数字电路组成,抗干扰能力强,可应用于航天领域。

控制系统的框图如图1所示,温度探测电路负责给温度二极管提供1 mA的稳恒电流,并读取温度二极管上的电压信号;温度电压信号经过放大电路放大后再经AD转换,送入FPGA中作为PID模块的输入参量进行运算处理。光电耦合电路负责前端控制器电路与后端功率驱动电路的隔离,同时起到保护核心控制器和隔离干扰的作用。功率驱动电路采用逆变H桥电路,由智能功率模块(IPM)驱动4个功率MOSFET,产生双极性SPWM电压波形,同时给压缩机的两个直线电机供电[2-3]。

图1 控制系统框图Fig.1 Control system framework

本系统中控制量为压缩机中直线电机的行程,可以通过控制电机两端电压来实现;反馈量为制冷机冷头的温度。为实现对温度的精确控制,需要对系统的热动力特性做一定的了解,并反映到控制器PID算法的参数整定中。

3 SPWM波形的生成

直线电机采用电压型SPWM波形驱动,而SPWM波形使用直接数字频率合成技术(DDS)、用不对称规则采样法产生。DDS技术是从相位概念出发直接合成所需要波形的一种新的频率合成技术,可以根据要求产生不同频率的正弦波,本设计中用于产生固定频率为50 Hz的正弦波。不对称规则采样法是既在三角波的顶点对称轴位置采样,又在三角波的底点对称轴位置采样,也就是每个载波周期采样两次,这样形成的阶梯波与正弦波的逼近程度会大大提高。由于采用的智能功率模块(IPM)的输出特性,最终加在电机两端的电压是双极性SPWM电压波形[4]。

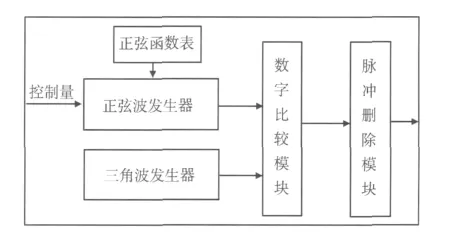

SPWM波形发生器在FPGA中实现,功能模块如图2所示。FPGA中的SPWM模块包括总线接口模块、系统时钟模块、三角载波发生器、取样地址发生器、正弦波取样模块、数字比较器模块、脉冲删除模块。

图2 SPWM波形发生器Fig.2 SPWM wave generator

三角载波发生器采用简单的加减计数器实现,载波频率与系统时钟频率和计数器范围有关。设计中采用将三角波中位线上移的方法,以避免负数的运算。9位寄存器从0加计数到511,再从511减计数到0,实现一个周期的三角波,不断循环就形成中位线位置为256的连续三角波。

正弦波的产生采用DDS设计思想,将完整的正弦波离散化,采样1 024个点,存储到片外的EEPROM中,使用时通过设定的存储器地址读取需要的正弦值;为节省存储器资源,也可根据正弦波的对称性,采样半个周期的正弦波,实际设计时再进行取负处理。通过改变取样地址的变化步长,就可以改变正弦波调制波的频率,从而实现不同频率的SPWM波形。

取样得到的正弦波值先与调制深度相乘,再加上256,然后送入到数字比较器与实时生成的三角载波进行时钟同步比较,当正弦波数值大于或等于三角波数值时,比较器输出高电平;反之,比较器输出低电平。

由于直接比较生成的SPWM波形会在正弦调制波的波峰和波谷产生很窄的脉冲,这些脉冲会导致H桥中功率MOSFET的频繁开关,增加了系统功率损耗的同时,也减少了开关管的寿命。因此,有必要删除这些窄脉冲。通过计算功率MOSFET的开关时间,确定脉冲宽度的阈值,设定脉冲删除字的大小,删除小于阈值的窄脉冲。

图3是调制深度分别为λ=0.75和0.9时得到的仿真图,spwmdata是窄脉冲删除前的波形,spwmout是窄脉冲删除后的波形。可以看出,在λ=0.75时的波形图中,脉冲宽度都没有小于阈值,因此没有删除窄脉冲;而λ=0.9时的波形图中,在正弦调制波的波峰和波谷处的窄脉冲都被删除。

图3 调制深度为λ=0.75和λ=0.9时的仿真图Fig.3 Simulation waveform when modulation depth λ=0.75 and λ=0.9

进行功能仿真后,将程序通过Actel公司的Libero IDE v8.5综合布局,加载到 ProASIC PLUS系列FPGA中,进行硬件验证。图4是调制深度分别为λ=0.75和0.9时在H桥两侧用示波器得到的SPWM波形图,通道ch1和通道ch2测量的分别是H桥两侧电机接线端的波形。图中ch1和ch2的波形完全反相,说明在半个周期内同一桥臂的两个MOS管都是反复开关,最终H桥输出的电压为双极性SPWM波形。同仿真结果相同,λ=0.75时的波形图中窄脉冲没有被删除;在λ=0.9时,正弦调制波的波峰和波谷处的窄脉冲被删除,验证了窄脉冲删除模块的功能特性。

图4 调制深度为λ=0.75和λ=0.9时H桥两侧输出波形图Fig.4 H-Bridge output waveform when modulation depth λ=0.75 and λ=0.9

4 温度PID控制

要使得制冷机工作性能稳定,必须对制冷机运行过程中的参数进行测量和控制。不同斯特林制冷机的结构不同,热力学特性有差异,参数具有不确定性,仅仅使用硬件电路实现具有很大的局限性。本设计中采用FPGA作为核心控制器,FPGA稳定性强,可以内部模拟80C51单片机,通过硬件实现复杂的数据运算,通过软件实现参数可变的温度控制算法[5]。

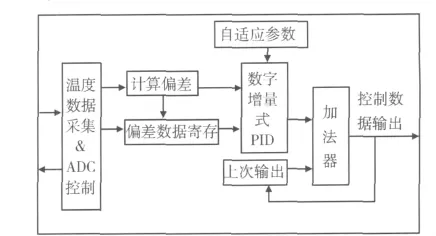

PID算法是最常用、简单且成熟的算法。数字PID算法分为位置式PID控制算法和增量式PID控制算法,前者为全量输出,直接控制执行机构的位置,且与过去状态有关,计算复杂;后者输出为执行机构位置增量,实现起来简单,可大大减少控制器的计算量,设计中采用后者进行计算。

通过积分分离、自适应等方法对基本的数字PID算法进行改进,使得制冷机启动速度加快,降温迅速,且可大大提高系统的温度控制稳定性。

本设计中使用FPGA实现数字增量式PID算法,可分为如图5所示的温度数据采集模块、偏差计算模块、PID计算模块、自适应参数模块、数字加法模块,其中PID计算模块又可细分为比例模块、积分模块和微分模块。

图5 数字PID算法模块Fig.5 Digital PID module

温度数据采集模块读取AD转换器输入的温度数据,并与温度设定值进行比较,得到温度数据的偏差值。自适应参数模块通过比较偏差值的大小,改变数字增量式PID算法中的比例、积分和微分参数,改善系统的响应速度和精度。PID计算模块通过对温度偏差的比例、积分、微分运算,得到对控制量的改变值,与上次输出结果相加后得到控制量的大小,本设计中控制量为SPWM波形的调制深度λ。

5 结论

使用FPGA分别生成SPWM波形和实现数字PID算法在很多文献中都有论述,但把两者统一在一片FPGA中还很少有文献提及。本设计中使用一片FPGA实现斯特林制冷机的温度闭环控制系统,同时实现SPWM波形发生器和数字PID控制器。FPGA实现的SPWM波形时序性好,波形稳定,抗干扰能力强;与时钟同步的数字PID算法能进行并行运算,具有快速、高效的特性。由于FPGA的高稳定性和可靠性,使得本设计能够应用在空间斯特林制冷机的温度闭环控制中。

1 陈国邦,颜鹏达,李金寿.斯特林低温制冷机的研究与发展[J].低温工程,2006(5):1-10.

2 贾旭鹏,姜继善,于秀明,等.斯特林制冷机温度闭环控制系统的探讨[J].真空与低温,2006(9):176-179.

3 李元明,于秀明,贾旭鹏.基于DSP的星载小型化斯特林制冷机控制器设计[J].真空与低温,2007(3):35-37.

4 杨旭东,张 强,韩雪晶.SPWM的FPGA实现方法[J].微计算机信息,2006(22):146-148.

5 白瑞林,江吕锋,王 建.基于FPGA的模糊自整定PID控制器的研究[J].仪器仪表学报,2005(8):338-738.