一种双核SoC调试系统的设计与验证

2010-05-31虞致国魏敬和

虞致国,魏敬和

(中国电子科技集团公司第58研究所,无锡 214035)

1 引言

传统的SoC构架在提高系统整体性能上已出现了一些瓶颈,多核SoC 正成为集成电路设计的研究热点之一[1]。多核SoC指的是一个SoC中包含2个或2个以上的处理器核,这些处理器的类型可能是异构的[2]。由于性能和功耗等方面的原因,高性能嵌入式系统多采用片上异质多处理器系统。在开发复杂SoC应用时,芯片的调试手段直接关系到开发的效率和进度,决定了应用的质量。没有调试硬件环境支持的追踪调试已经不能胜任复杂SoC的应用[3]。

另一方面,在SoC开发过程中,调试系统本身的验证非常重要。对于调试系统的验证,由于没有相应的RTL验证环境,一般都放在FPGA原型验证阶段进行,并借助于一些逻辑分析仪对仿真波形进行采样分析,延长了系统验证时间且降低了验证效率[4-5]。

在某控制双核SoC的硬件设计基础上,提出了一种基于JTAG的片上调试系统设计方案;基于SystemVerilog DPI[7]和Real View调试器,提出了一种双核SoC的片上调试系统虚拟验证环境。在该验证环境中,利用DPI将软件调试器集成到验证过程中,可完成RTL级的JTAG调试接口仿真与验证。该方法能够将以前FPGA原型验证发现的调试系统错误提前到系统仿真验证阶段,缩短了系统周期,提高了验证效率。

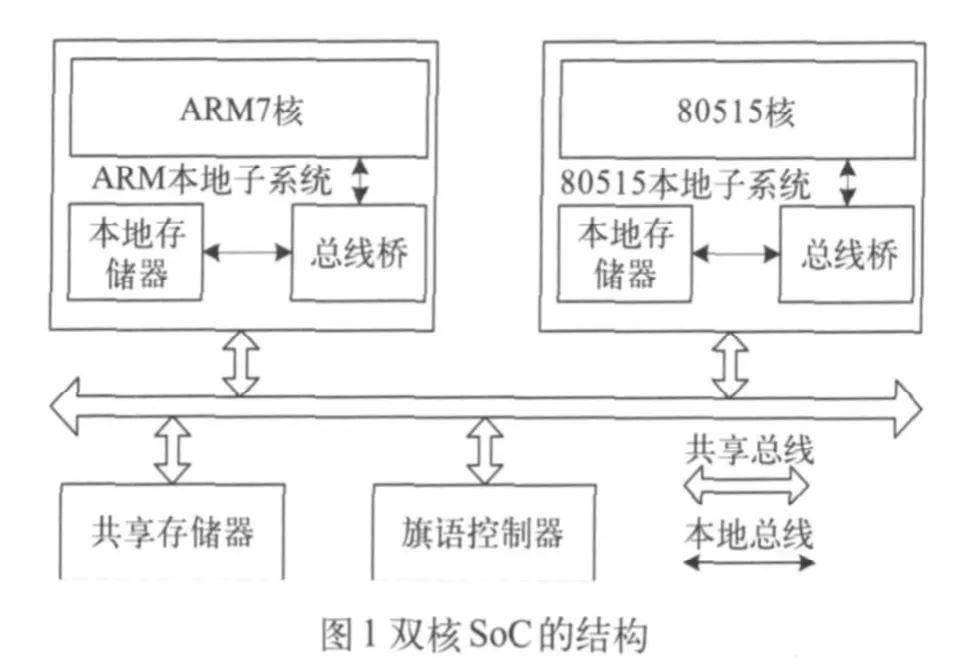

2 异构双核SoC的结构

某异构双核SoC面向工业控制、多媒体应用及其他消费类电子设计,其结构如图1所示。该SoC包括一个高性能具有较强运算能力的ARM7以及一个控制能力较强但占用资源较小的80515处理器核。整个SoC有以下几个主要部分:ARM7子系统、80515子系统、共享总线以及共享存储器。另外,SoC还包括PLL、时钟及复位模块和相关的配置单元。双核通过共享固定内存单元的机制进行通讯,来协调完成各种操作。

3 调试系统设计

3.1 调试系统软件

ARM调试软件采用RealView[6]调试器,该调试器在综合性能调试环境下提供最合适的调试功效。80515调试软件采用Keil公司开发的Keil C51。Keil uVision集成开发环境开放了调试器与目标硬件接口,即Advanced Generic Debug Interface(AGDI)。器件厂商只要为它们自己的8051产品设计专用的驱动程序(动态链接库DLL),就可以使Keil IDE的调试器在不改变图形界面的情况下支持不同的硬件链接方法。

3.2 调试系统硬件

调试硬件设计如图2所示,包括ARM和80515各自的调试系统、交叉触发模块。该SoC的同步调试主要分为两类[8]:(1)单步、运行和停止(由用户操作发出的命令);(2)交叉触发(处理器运行过程中被触发,需要在片内预设配置寄存器进行控制)。对寄存器和存储空间的访问,没有采用同步机制,而是采用单核机制实现。

调试同步的寄存器在交叉触发模块(C r os s Trigger)中集中控制实现。Cross Trigger包含三个寄存器:交叉触发命令广播寄存器、软件断点同步配置寄存器、硬件断点同步配置寄存器。交叉触发模块向CPU核发布命令来实现单步/运行/停止的同步执行功能、软/硬件断点的同步。

4 调试系统的验证

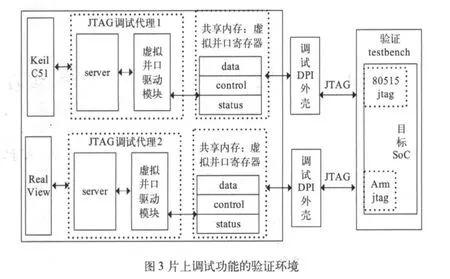

4.1 调试验证环境

结合集成调试环境和目标芯片,可构成一个片上调试功能的验证环境(如图3所示)。该环境在UNIX环境中运行。集成调试环境为软件调试器,包括RealView调试器、Keil C51调试器,JTAG调试代理、虚拟并口驱动、共享内存区。为了实现验证Tes t b en ch和集成调试环境的连接,我们基于SystemVerilog DPI编写了一个调试DPI外壳。通过DPI,SystemVerilog可以调用所有的C/C++/System C的功能函数,实现对共享内存区的数据访问。

在调试验证环境中,我们用C语言开发了一组程序,用以实现对并口内存区的访问。在调试外壳中,使用简单的i m p o r t声明把C函数导入到SystemVerilog中。验证环境中利用C语言函数调用共享内存中的数据。调试DPI外壳和验证Testbench一起采用VCS进行编译。

4.2 验证Testbench的设计

验证Testbench采用SystemVerilog[7]实现,验证Testbench结构如图4所示。验证Testbench模拟目标芯片及芯片外围环境,包括目标SoC、外部存储器、时钟、复位等,采用RTL代码及其他行为模型描述。在验证过程中,用HDL函数$readmem读入功能仿真程序的十六进制文件(.dat)。

4.3 验证过程

仿真软件采用Synopsys公司的VCS软件。该软件是编译器、仿真器和其他一些工具组成的工具集。调试DPI必须编译并链接到Verilog仿真器。

仿真中,RealView和Keil C51界面把数据写到内存中的虚拟并口数据区,TAP中调用调试DPI外壳从这个数据区中交换数据,这样就在仿真器上实现了与主机调试软件的通信。RealView和Keil C51本身支持源码级调试,只要调试代理正确地实现了RealView及Keil C51的远程调试协议,本验证系统就可实现源码级调试。

5 结论

调试接口的设计是多核SoC设计中的重要环节,调试系统验证对于SoC的设计非常重要。基于JTAG接口和操作系统的基础,文中实现了某控制多核SoC片上调试功能,可实现芯片的调试控制和存储访问。在此基础上,提出和设计了一种基于SystemVerilog DPI和Real View、Keil C51已有调试功能的SoC调试系统验证环境。利用该平台,在RTL仿真验证时便可以通过JTAG对基于ARM核 的SoC进行调试,这使对SoC的调试从以往的FPGA验证提前到RTL仿真验证阶段进行,可有效缩短集成SoC设计周期,并提高SoC验证效率。

[1]成杏梅,刘鹏,钟耿,等. 嵌入式MPSoC的调试功能实现[J]. 计算机辅助设计与图形学学报,2008,20(4):438-445.

[2]邵利群,张文婷. 异构多处理器系统芯片的设计与研究[J].中国集成电路,2008,17(3):49-52.

[3]凯思·诺顿. 嵌入式系统的挑战[J]. Information Quartely,2004,1:45-46.

[4]韩可,邓中亮,施乐宁,等.针对JTAG调试的RTL验证环境设计原理[J].电子测量技术,2008,31(1):72-76.

[5]虞致国,魏敬和. 一种基于JTAG的SoC片上调试系统的设计[J].微电子学与计算机,2009,26(5):5-8.

[6]ARM Limited.RealView Debugger Version 3.0TraceUser Guide[EB/OL].http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0322a/Babgijgj.html/ARM DUI 0322A.pdf.

[7]Standard for SystemVerilog-Unified Hardware Design[C].Specification and Verification Language.IEEE Std 1800-2005.

[8]扈啸,李杰,陈莉丽,等. 多核处理器YHFT-QDSP的调试系统[J].计算机工程,2008,30(9):116-118.