VDMOSFET低导通电阻改良研究

2010-02-26陆宁

陆 宁

(上海贝岭电子有限公司,上海 200233)

1 引言

由于VDMOSFET具有输入阻抗高、驱动简单、开关速度快和热稳定性好等优点而被广泛应用于各类功率电路中。如今电子产品对低功率的要求越来越严格,如何有效改良VDMOSFET的导通电阻以降低消耗功率,成为有必要解决的问题。本文介绍了通过在引线孔蚀刻时采取soft-etch工艺来改良导通电阻的方法。

2 VDMOSFET导通电阻模型

2.1 理论模型

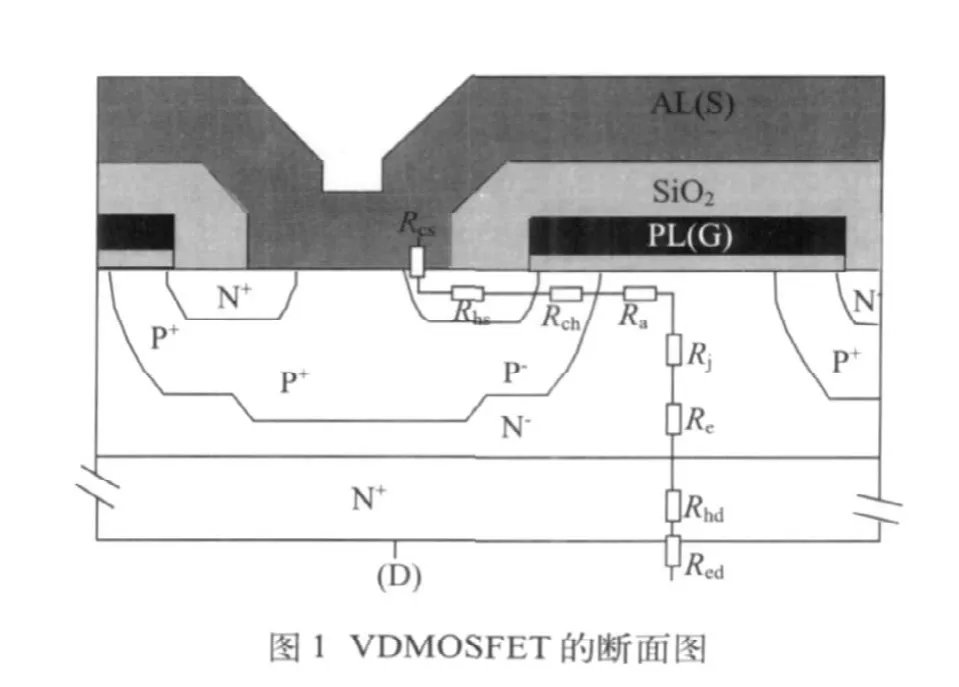

图1是VDMOSFET的示意图。导通电阻可以分成以下几个部分:源极接触电阻Rcs,源区体电阻Rhs,MOSFET沟道电阻Rch,积累层电阻Ra,寄生结型管电阻Rj,外延层电阻Re和衬底电阻Rhd,以及漏极接触电阻Red。一般来说,漏源极接触电阻和漏源区体电阻在正常工艺条件下可以做得很小,且与器件结构的参数关系不大。对导通电阻起主要作用的是Rch和Ra、Rj以及Re。这几个电阻均与结构参数密切相关。因此,VDMOSFET的导通电阻可近似表示为:

2.2 实际情况

由于在实际大生产中,往往在材料参数一定的情况下,导通电阻有临界或者偏大的情况。虽然上述的源极接触电阻Rcs和漏极接触电阻Red对导通电阻的影响不大,但是实际情况下是有影响的,而且不可忽略。以下就是通过引线孔刻蚀工艺的改进来降低源极接触电阻Rcs,从而进一步降低导通电阻。由于先前出现过引线孔未刻蚀干净的现象,导致器件参数异常,因此对于引线孔刻蚀要做重点研究。

3 改良刻蚀工艺降低导通电阻

3.1 理论基础

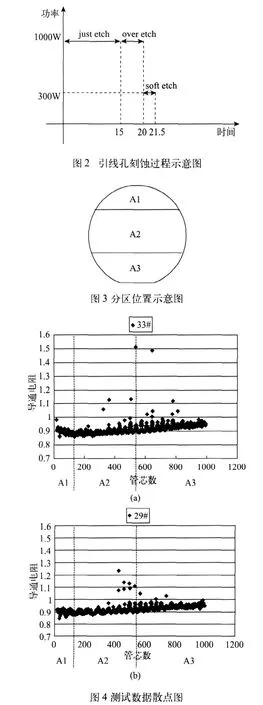

在VDMOSFET加工过程中大量用到等离子体刻蚀,具体引线孔刻蚀中,需要刻蚀的磷硅玻璃(PSG)较厚而且均匀性不好,这就增加了刻蚀的难度,同时也对器件参数的一致性提出了挑战。实际应用中,氧化层的刻蚀功率相当大,如果过刻蚀量调整不好的话,对器件的参数有很大影响。如引线孔中氧化层刻蚀不净或者过刻严重,可能导致布线后铝和引线孔的硅之间接触电阻(Rcs)过大,严重影响导通电阻。试验结果表明,由于刻蚀功率较高,虽然有一定的过刻蚀,还是不能满足参数一致性的要求。在这种情况下,提出了soft-etch这种工艺方案。其方法如下:由于氧化层的不均匀,导致引线孔刻蚀的不均匀,这样大功率的过刻蚀对引线孔的硅就会造成较大的损伤,而且这种损伤无法修复。因此,采取在过刻蚀阶段后增加一步小功率的刻蚀,把大功率刻蚀过程当中损伤的硅去除掉,这个过程就叫soft-etch。图2为引线孔刻蚀过程示意图。

3.2 实验方案及测试结果

根据soft-etch工艺需求,实验中硅刻蚀量为20nm~30nm,这样才能有效去除损伤的硅层。为了验证soft-etch工艺的可行性,利用步进光刻机的特点,对一枚硅片分3次曝光,以便使实验有一个比较明显的结果。对比示意图如图3所示。

取一枚硅片并分3次曝光,以实现试验的目标,同时也节省试验硅片数,还可以做明显的对比。从上往下,A1区域在过刻蚀完后采用100W小功率刻蚀;A2区域在过刻蚀后采用1000W功率刻蚀;A3区域在过刻蚀完后用湿法的F108溶液进行处理。测试数据散点图如图4,测试方法也按试验顺序测试。

实验共有5枚硅片,在这里只取其中的2枚数据散点图(图4的a和b),其余情况跟这两枚相似。从散点图可以明显看出,A1区管芯的导通电阻值趋向最小,稳定在一个值;A2区的导通电阻值比较散乱且偏大;而A3区虽然也比较稳定,但总体导通电阻有偏大的趋势,这也是不可取的。

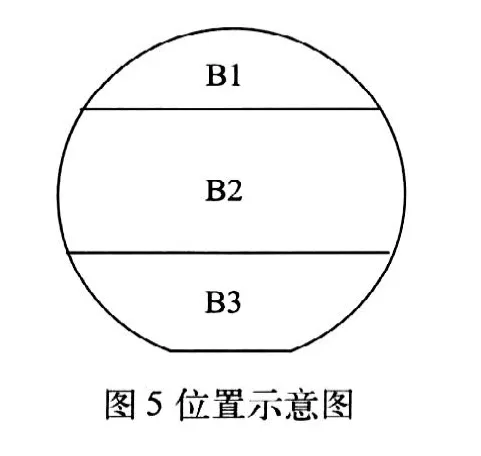

有了以上的数据以后,就要寻找最佳功率来实现soft-etch工艺。这次选择在相同气体流量和工作压力下,采取不同的功率来实现。B1区采用100W,B2区采用300W,B3区采用500W工艺,其实验方法如图5所示(只抽取其中的2枚数据)。

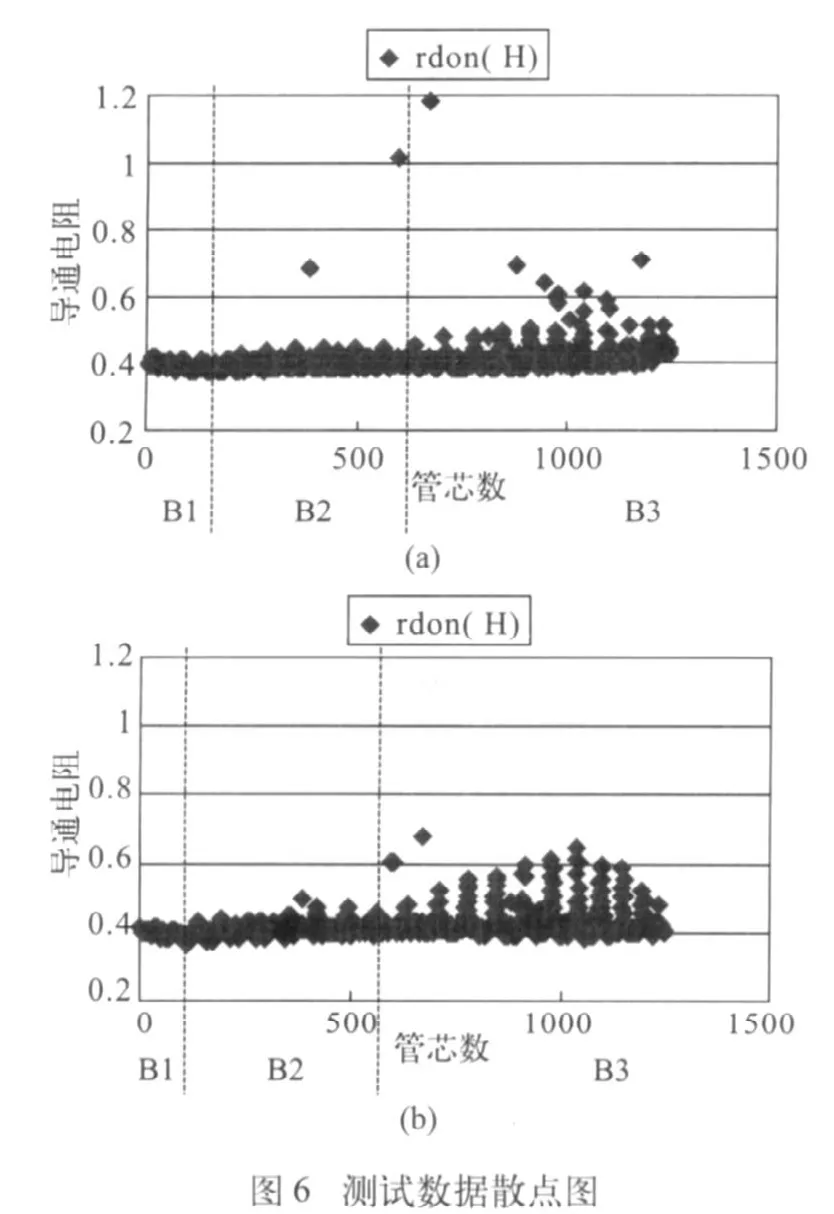

其试验结果散点图如图6的(a)和(b)。测试数据表明,100W和300W功率相对稳定,且导通电阻也比较稳定;500W功率下刻蚀的导通电阻比较散,且有偏大的趋势。结合实际设备情况,决定取刻蚀功率100W。在实际过程中重复多次多品种实验,结果非常理想,限于篇幅不再把数据一一列出。

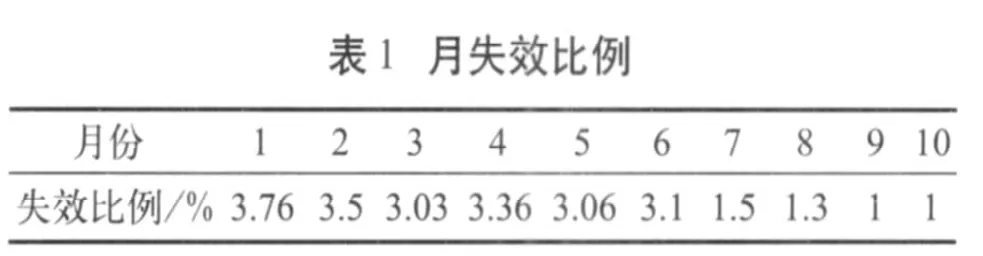

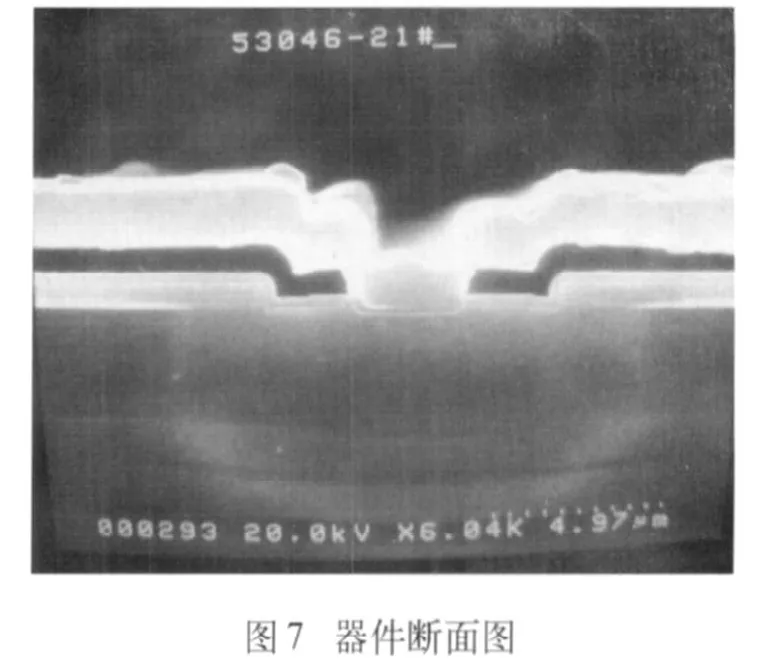

目前,此工艺已全面投入运行,并在实际生产中取得了非常好的效果。对导通电阻的失效批数占整月投料批数的比例做了统计,统计结果如表1。为了验证工艺的正确性,对实际器件做了扫描电镜图片,证实对硅去除量是20nm~30nm左右,如图7。

4 结论

以上试验结果都是实际数据,而且已投入生产,是通过实践检验得出的。由此可见,VDMOSFET中的soft-etch工艺对改良导通电阻非常有效,达到了预期的效果。

[1]维捷斯拉夫·本达,等. 功率半导体器件理论及应用[M].2005.248-256.

[2]刘永,张福海.晶体管原理[M]. 2002. 357-361.

[3]石广源,等.低压VDMOSFETRon的最佳比例设计研究[M].2002.

[4]MODERN POWER DEVICES B.JAYNT BALIGA[S].1987.