基于FPGA的无线传感器网络SoC验证平台设计

2010-02-26虞致国黄召军陈子逢万书芹

虞致国,黄召军,陈子逢,万书芹,魏 斌

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

随着嵌入式系统、无线通信、网络和微电子机械系统等技术的快速发展,具有感知、计算和无线网络通信能力的传感器以及由其构成的无线传感器网络引起了人们的极大关注[1],进一步低成本、小型化的无线传感器网络SoC需求也越来越迫切。在SoC的设计过程中,功能验证为极其重要的步骤,其目的是要保证设计数据和设计规范的一致性。研究表明[2],验证在集成电路设计过程中要占50%~80%的工作量,验证是影响项目开发进度的关键因素。一个快速、完备、系统的功能验证平台对于SoC的设计来说非常重要,可有效缩短设计时间和提高设计质量[3]。随着FPGA技术的快速发展,其速度、规模不断增大,成本不断降低,使得FPGA验证已经成为SoC设计的一个重要验证手段。它具有验证周期短、能真实反映硬件结果等特性。

针对8位无线传感器网络SoC,本文构建了一个基于FPGA的硬件原型验证平台。该验证平台能够进行软硬件协同验证,具备较强的逻辑分析和诊断能力,从而提高SoC流片成功率,加快SoC的开发。

2 WSN SoC结构

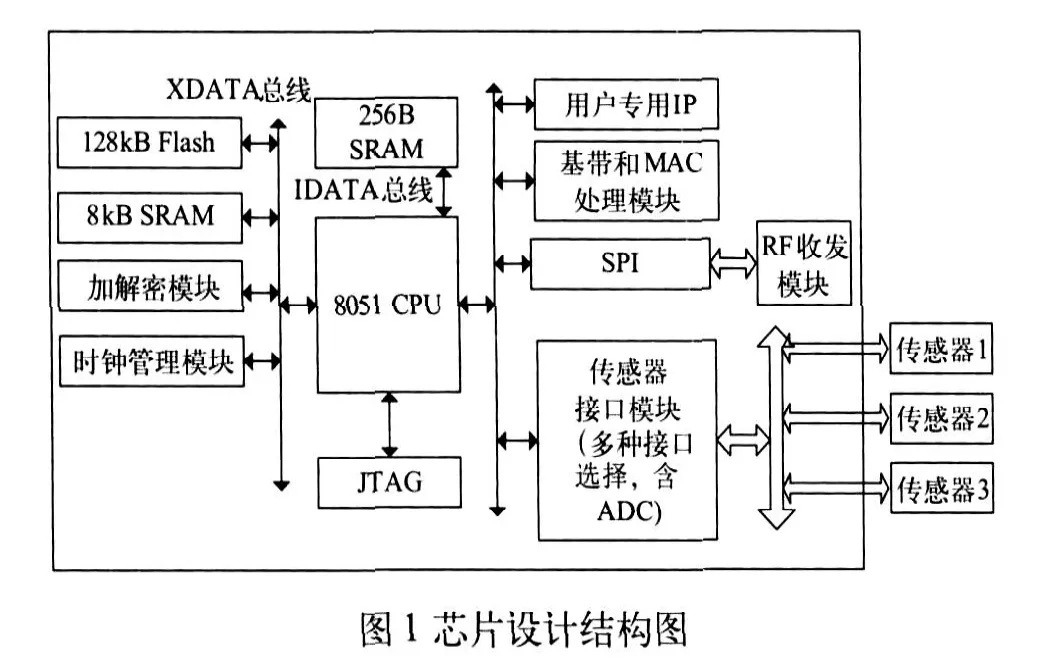

WSN SoC采用8051核为核心,包括用户专用IP模块、基带和MAC处理模块、传感器接口模块、加解密模块、存储器模块、通用外设、能量管理模块等。SoC硬件结构如图1所示。该8051核的指令和MCS-51兼容,指令单周期执行,且提供了指令地址空间可擦写功能,并在核内部集成了一个调试接口(OCI)。8051核具有三种地址空间:XDATA地址空间、IDATA地址空间、SFR地址空间,并对应三条总线。传感器数据采集接口模块采用多种标准的传感器接口,传感器信号经ADC采集后交给协议处理模块处理。片内SRAM(XDATA空间)为8k字节,Flash为128k字节,数据SRAM为256k字节(IDATA地址空间)。为了减轻CPU的负担及占用时间,在芯片中加入了AES模块来独立完成加解密操作。AES其分组长度和密码长度都是可变的,分组长度和密码长度可以独立地指定为128比特、192比特或者256比特。

3 基于FPGA的验证功能平台

3.1 原型板的设计

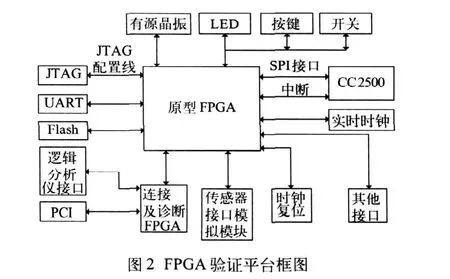

基于FPGA的ASIC原型验证平台框图如图2所示。验证板包括原型FPGA、连接及诊断FPGA、低速率ADC、射频(RF)接口芯片、传感器接口模块、常见外设等。RF模块采用SPI接口进行控制,时钟及传感器模块采用I2C模块进行控制,Flash模块采用在FPGA上进行外挂。

3.2 FPGA的选择

原型FPGA、连接及诊断FPGA采用Xilinx的Spartan-3A系列产品XC3SD1800A,规模相当于180万门。其内部包括1512kB的块RAM,260kB的分布式RAM,最大用户引脚519个,时钟管理单元(DCM)8 个[4]。

原型FPGA实现WSN SoC芯片的数字部分,包括CPU、AES、存储单元、系统复位模块、存储器接口、常用外设等。

3.3 射频芯片的选择

原型系统的射频芯片采用Ti公司的CC2500,该芯片是一超低功耗、低成本的无线收发模块。CC2500集成了一个高度可配置的调制解调器,支持不同的的调制格式,包括FSK、GFSK、OOK和MSK,其数据传输率最高可达500 kbps[5]。

CC2500为信息包处理、数据缓冲、脉冲发送、空闲信道评估、连接品质指示和电磁唤醒等功能提供了额外的硬件支持,有四种主要状态:接收(RX)、发送(TX)、空闲(IDLE)和休眠(SLEEP)。

CC2500主要设定为在2.400GHz~2.4835GHz的ISM(工业、科学和医学)和SRD(短距离设备)频率波段。CC2500通过4线SPI兼容接口(SI、SO、SCIK和CSn)配置,这个接口同时用作写和读缓存数据。

3.4 传感器接口模块

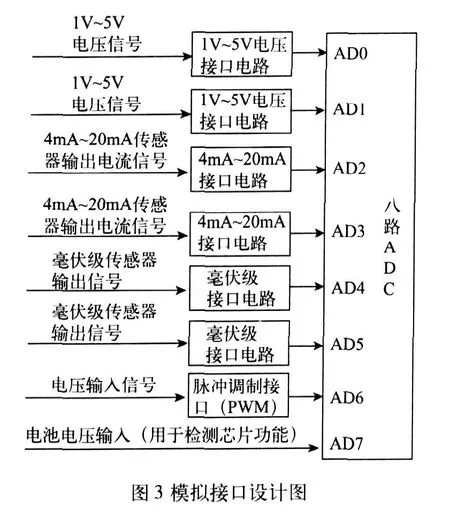

传感器采集外部的温度、压力、光强和磁场等需要采集的物理信息,并将上述物理量转化为系统可以识别的原始模拟电信号,通过积分电路、放大电路的整形处理,最后经过A/D转换成数字信号送处理器模块。对于不同的探测物理量,传感器模块将采用不同的信号处理方式,需要设计相应的传感器接口电路,同时需要预留相应的扩展接口,以便于扩展更多的物理信号量。

无线传感器网络SoC核心利用的8051CPU核作为微处理器,片内集成控制单元及多种接口,利用硬件实现模拟接口(如4mA~20mA电流转换电压接口、0~5V电压转换接口或PWM输出接口)与数字接口(包括CAN总线接口、SPI、IIC以及UART口)。

考虑现场采集信号的多样性及各种传感器输出信号的差异,系统考虑外接以下几种传感器输出信号,因此模拟接口的设计分为以下几类:

(1)两个毫伏级电压信号输入通道;

(2)两个4mA~20mA电流信号输入通道;

(3)两个1V~5V电压信号输入通道;

(4)一个电池电压输入信号通道,方便检测系统芯片。

模拟接口的示意图如图3,各接口电路分别用来实现将相应的输入信号转换成0~1.8V的电压信号供A/D模块采样。

3.5 SoC原型验证平台扩展能力

外围部件也是原型验证板上不可或缺的一部分,可以验证SoC中各个接口IP能否与8051核、外部接口单元、硬件驱动、操作系统协调工作等。板上集成了常见的系统接口,如UART、SPI、IIC、GPIO等,来方便验证板的使用。

为了增强对原型验证系统的调试及诊断能力,实现对FPGA设计内部节点的监督,增加了一块FPGA与原型FPGA相连。运行过程中,被监测信号点的信号值存入SRAM,PC机可通过DMA方式读取SRAM中的信号值,从而实现了软件读取原型机运行过程中的数据,增强了原型机的诊断能力。

4 基于原型系统的验证

4.1 验证流程

在SoC原型验证系统上进行系统原型验证可以分为三个步骤,逐次递进。首先验证硬件平台各个模块的正确性,其次验证软件平台的正确性,最后进行整个SoC设计的原型验证。

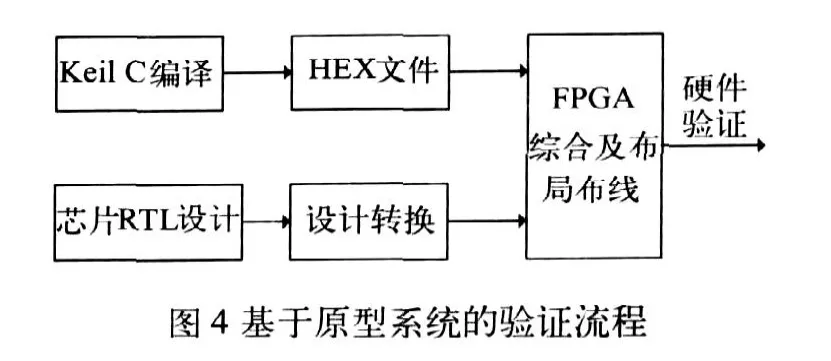

使用8051的C语言或汇编程序编写无线传感器网络协议的程序,采用Keil集成开发环境编译成hex文件。然后通过Xilinx的ISE相关工具生成相应的ROM文件。其流程如图4所示。

4.2 设计转换

采用FPGA原型系统来验证ASIC设计,首先要把ASIC设计转换成为FPGA设计。转换主要涉及到存储器、时钟等方面。存储器在ASIC设计中调用代工厂的Memory硬模块,转换为FPGA设计时需要改为采用FPGA的blockRAM模块。在ASIC中时钟是采用时钟树(含门控时钟)、PLL来进行设计的。转换成FPGA设计后,时钟树采用FPGA中的全局时钟资源,PLL采用其DCM。对于门控时钟,改用FPGA内带有时钟使能的寄存器。

4.3 传感器网络节点芯片的验证

在进行SoC整个设计原型验证前,必须保证各个模块工作正常、接口符合时序要求。

一个完整的SoC调试系统通常包括调试主机、调试协议转换器、调试目标芯片三个部分。调试主机运行调试软件,提供给开发者与目标系统交互的友好界面,它不直接实现对底层目标硬件的支持。通过开发支持Kei l集成开发环境的AGD I接口(Advanced Generic Debugger Interface),能够实现主机端Keil 软件与8051 IP核的联合调试。

为了调试WSN SOC,只需要为其设计专用的驱动程序(动态链接库DLL),就可以使Keil IDE的调试器在不改变图形界面的情况下支持不同的硬件链接方法。结合集成调试环境和目标芯片,可构成一个片上调试功能的验证环境。

在调试环境完备的情况下,WSN SoC的FPGA原型验证是一个从外设模块到核心模块、从简单程序到复杂协议的过程。

首先,利用原型验证外设接口。利用CPU验证来验证存储器系统能否正确读写,支持各类读写行为。在存储器验证完毕后,可以针对各个外设用小程序进行指令级验证。在此基础上,开发给予CPU的测试程序,利用程序独立访问各外设接口,如串口、SPI口、I2C口等。在此过程中,利用编译好的程序加载到存储器,运行程序,观察8051、存储器和外设三者之间的数据传输情况,从而验证外设的功能和性能。运行测试程序时,可把系统运行到特定时间和步骤的执行结果提取出来并自动比较是否正确,并把结果传递到PC主机。其次,进行无线网络协议的验证,包括Zigbee协议栈软件程序的验证、相关应用的验证等。

5 结束语

功能验证是SoC的关键技术之一,贯穿整个设计过程。本文设计了一种WSN SoC的基于FPGA的功能验证平台,克服了传统原型验证的一些缺点,不仅可以通过实际器件获得输入激励,还可以通过计算机输入激励获得结果进行比较,具有较好的移植性和一定的普遍应用性。在SoC平台原型验证过程中,可以先从硬件模块的原型验证到模块级的小程序验证,再到操作系统的运行验证,最后到整个SoC所有应用程序的原型验证。

[1]郑朝霞.无线传感器网络节点芯片关键技术的研究与实现[D].华中科技大学,20080521.

[2]Rashinkar P,Paterson P,Singh L. System on a Chip Verification Methodology and Techniques[M]. [S.1]:America Cadence Design Systems,Inc.,2002.

[3]张珩,沈海华.龙芯2号微处理器的功能验证[J].计算机研究与发展,2006,43(6):974-979.

[4]刘涛,王凯,李晓民,等. 曙光5000芯片组系统级功能验证平台[J].计算机工程与科学,2009,31(11):37-39.

[5]虞致国,魏敬和.基于FPGA的ARM SoC原型验证平台设计[J].电子与封装,2007,7(5):25-28.

[6]刘振文,邓毅华,彭友斌.基于CC2500的2.45GHz RFID系统设计[J].电子技术与应用,2008,7:76-78.