一种高线性度CMOS自举采样开关

2010-02-26潘小敏黄言平陈珍海

潘小敏,黄言平, 陈珍海

(1.无锡市商业职业技术学院,江苏 无锡 214153;2.北京华航无线电测量研究所,北京 100013;3.中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

随着CMOS集成电路工艺技术的迅速发展,芯片集成度不断提高,片上系统(SOC)是现在集成电路发展的趋势。在数字电路处理速度极大提高的情况下,如何快速采样模拟信号并对其进行量化,是系统能否高度集成的一个关键环节。模数转换器(ADC)电路是实现从模拟到数字的转换接口,对于ADC电路的实现,需要用到大量的数据采样开关。作为ADC系统与外界的接口,采样开关的性能优劣直接决定了ADC所接收到的信号纯度和真实性。对于CMOS工艺,采样开关一般通过MOS管来实现。随着采样时钟频率的提高,传统MOS采样开关的线性度不断下降,制约了ADC电路的动态范围,已经无法满足高速度、高精度模数转换器对采样信号动态性能的要求。

为减小采样MOS开关的非线性失真,可以采用互补型CMOS开关[1],由宽长呈一定比例关系的PMOS开关和NMOS开关并联而成,该方法减小了传统MOS采样开关由于栅源电压随输入信号电压变化所产生的非线性,但是开关导通电阻的非线性变化仍然存在,并限制着MOS采样开关动态范围的进一步提高。通过采用栅压自举采样开关[2~5],固定MOS采样开关的栅源电压可以更彻底地克服输入信号变化带来的开关导通电阻的非线性特性。本文设计了一种高线性度CMOS采样开关,可以克服输入信号变化带来的开关导通电阻的非线性特性,具有非常优越的动态特性。

2 MOS采样开关的非理想特性分析

图1所示为一个简单的采样保持电路,它包括一个开关和一个电容。其中,Vin为输入信号,MOS管Ml为采样开关,C为保持电容,Vout为采样保持电路的输出信号。CK为采样控制时钟信号,其高电平为电源电压AVDD,低电平为AGND。

在采样阶段,CK为高电平,Ml导通,Vin对电容C充电,Vout跟踪输入信号,随Vin变化而变化;在保持阶段,CK为低电平,Ml截止,C将保持采样结束时刻的电压值Vin,从而完成一次采样过程。由于MOS开关具有的非理想因素,对采样电路在速度和精度上产生影响。

当电路处于采样期间时,晶体管Ml导通,且工作在线性区,可以将MOS管Ml视作一个阻值为Ron的电阻,其大小为:

可见,Ron是一个与输入信号Vin和衬底偏置电压VSB相关的非线性电阻。MOS开关的非线性导通电阻不但会产生热噪声,而且引入的非线性误差、相移误差制约着采样保持电路的带宽和性噪比的提高,也限制了信号的输入范围,尤其是采样开关对整体电路系统的性能有着重要的影响。

MOS开关的导通电阻对采样保持电路会引入三个方面的误差源。第一个误差源是由于输入开关的导通电阻和采样电容组成的RC网络的有限带宽引入。当MOS开关导通的时候,导通电阻和开关的尺寸以及栅源电压有关,在采样时,开关的导通电阻和采样电容就构成了一个RC网络,限制了带宽。随着电源电压的降低,MOS管的过驱电压下降,促使MOS管导通电阻进一步增大,从而增加电路的RC时间常数,这将会直接导致采样保持电路输入带宽和“跟踪”输入信号能力的降低,从而严重影响电路的采样功能。采样RC网络的-3dB频率是:

第二个是开关导通电阻产生的热噪声。热噪声从频谱上来说,基本上类似理想的白噪声。MOS开关的导通电阻产生的热噪声通过电容耦合到电路的输入端成为等效噪声的主要部分。对于处于线性区的MOS管而言,其热噪声主要来源于沟道电阻。采样开关引入噪声的方差与采样电容Cs成反比,即KBT/Cs(KB是Blotzman常数,T是热力学温度,Cs是采样电容),所以通常把这个噪声叫做KT/C噪声。所累积的热噪声的功率只与电容大小有关,而与电阻的大小无关,因此要减小开关的KT/C噪声,就必须增加采样电容的大小。

第三个误差源是由于采样开关的非线性导通电阻所引入的。在图2中,Ron两端的电压随输入电压不断变化,根据电压分配关系,Cs上保持的电压也会有非线性的失真。

对于中频采样应用的高速高精度ADC来说,ADC的精度要求、速度要求和有效输入信号带宽要求特别严格。因此应该尽量减小导通电阻Ron,增大采样带宽,同时尽量增加置Ron的线性度来减小采样过程的失真误差。

根据式(2),对于采用固定尺寸的采样电容,为了减小导通电阻,在其中MOS管载流子迁移率u和单位面积栅氧化层电容Cox不变的情况下,增加MOS开关宽长比W/L和MOS管的过驱动电压Vgs-Vth,可以减小导通电阻的阻值。但由于增加MOS开关宽长比W/L会增大MOS开关的各个寄生电容,影响高频特性,因此增加MOS开关宽长比W/L的效果也是有限的。

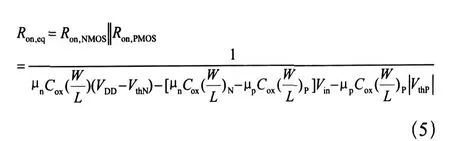

3 互补型CMOS开关

CMOS采样开关由一对PMOS管和NMOS管组成。它们的栅极分别由一对互为反相的时钟所控制,为高电平时,NMOS与PMOS同时导通,根据式(1),可分别得到NMOS管和PMOS管的导通电阻Ron(忽略体衬偏效应的影响):

由上式可以看出,当输入电压增大时,NMOS管导通电阻会显著增加。而对于PMOS管,它的导通电阻随输入电压变化的情况与NMOS管完全相反。将PMOS管与NMOS管并联使用便得到CMOS开关,CMOS开关的导通电阻Ron,eq为:

由上式我们可以看到,假设NMOS管和PMOS管的阈值电压不随输入信号电压变化,只要选择宽长呈一定比例的PMOS和NMOS,理想情况,若unCox(W/L)n= upCox(W/L)p,CMOS开关的导通电阻与输入信号无关。然而,实际中由于衬偏调制效应,NMOS管和PMOS管的阈值电压是随输入信号电压变化而变化的。因此,互补型CMOS采样开关的线性度仍然受到一定限制。仿真结果显示,在A/D转换器精度要求在10位以上时,CMOS采样开关将无法满足要求。

4 高线性度CMOS自举开关电路

前面已经讨论过MOS管的源极电压为输入电压随着输入变化而变化,栅极电压如果为恒定值(比如电源电压VDD),则Vgs将会随着输入信号而变化。若忽略衬偏效应,认为阈值电压Vth为常数,则Vgs的变化会引起导通电阻的变化并使采样网络线性度降低。

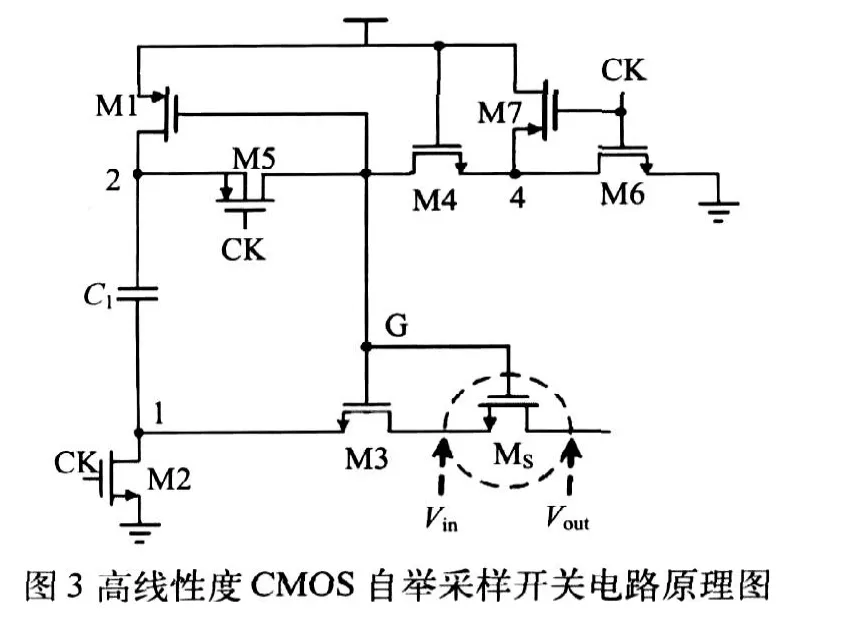

通过采用栅压自举开关可以很大程度上解决Vgs随着输入信号而变化的问题,如图3所示。其连接关系如下:MOS管M1、M2的源极分别接电源电压和地,漏极分别接电容C1的上下极板节点2和节点1,栅极分别接节点G和时钟CK。MOS管M5的源极、栅极、漏极分别接到节点2、CK、节点G、衬底和源极短接。MOS管M4、M7的漏极和MOS管M6的漏极接在一起,称为节点4。MOS管M4的栅极、源极分别接到电源电压和节点G。MOS管M7的栅极、源极分别接到CK和电源电压。MOS管M6的栅极、源极分别接到时钟CK和地电压。MOS管M3的源极、栅极、漏极分别接到节点l、节点G和信号输入节点Vin。开关MOS管Ms的源极、漏极分别接输入节点Vin、输出节点Vout,栅极接节点G。

在图3中,栅压自举开关的工作受时钟CK控制。时钟CK为高电平时,MOS管M2、M6导通,MOS管M7截至,M4导通,使得MOS管M1也导通;电路通过MOS管M1和M2对电容Cl充电,使得电容Cl两端的电压接近电源电压VDD,从而在电容Cl上存储了VDD×Cl的电量。当时钟CK从高变低时,MOS管M2、M6截止,MOS管M7导通,M4导通;电源通过MOS管M4、M7对结点G的对地寄生电容充电,使得结点G电压升高,MOS管M1截止,M5、M3导通;输入信号通过MOS管M3抬升电容Cl下极板电压直到其值等于输入电压Vin;由于电容Cl上存储的电荷在时钟CK变化过程中没有放电回路,存储在其上的电荷保持不变,电容Cl上极板的电压就会同步上升,直到其值等于VDD+Vin,开关管Ms栅源电压为电源电压VDD。

根据式(1),此时导通电阻为:

可以看出与式(1)相比,Ron变为一个与输入信号Vin无关,而仅与衬底偏置电压VSB相关的非线性电阻,线性度得到了很大的提高。

5 仿真结果

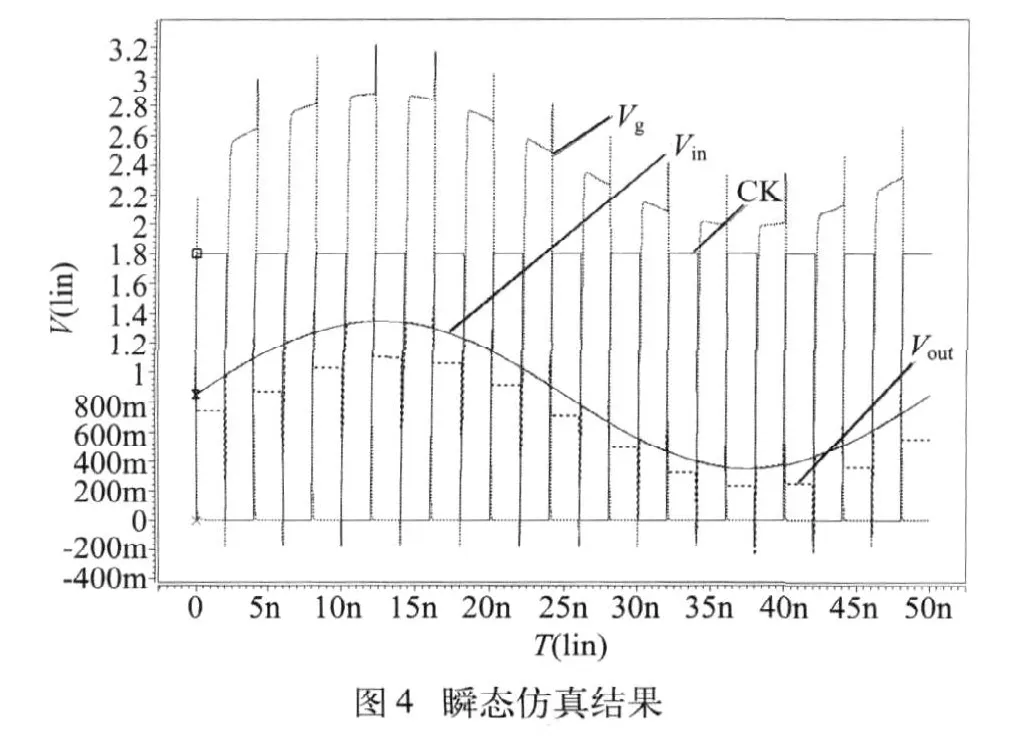

采用SMIC 0.18μm标准CMOS工艺的BSIM3模型,利用HSPICE模拟软件对电路进行了仿真。图4所示为所设计高线性度CMOS自举采样开关电路的瞬态仿真波形图。在CK为高电平时,开关管Ms栅压信号Vg为低电平,开关管Ms关断截止,输出信号Vout保持不变;在CK为低电平时,开关管Ms栅压信号Vg跟随输入信号Vin并保持栅源电压为Vgs=VDD不变,开关管Ms导通,输出信号Vout跟随输入信号Vin,符合前面的理论分析。

图5所示为所设计的高线性度CMOS自举开关采样结果,做FFT频谱分析得到输出频谱,可以看出本文设计的高线性度CMOS自举开关在100MSPS采样速度的条件下,对于2.48MHz正弦输入信号采样得到输出结果的SFDR(无杂散动态范围)为101.5dB,可以适用于16位精度的ADC应用要求,说明本文设计的高线性度CMOS自举开关有良好的线性度,符合前面的理论分析。

6 结论

本文分析了MOS采样开关非线性的来源和互补型CMOS采样开关的不足之处,实现了一种高线性度CMOS自举采样开关。所设计的高线性度CMOS自举开关的导通电阻只与电源电压、MOS管载流子迁移率、单位面积栅氧化层电容、MOS管宽长比和MOS管阈值电压有关,消除了采样MOS管因栅源电压变化所引入的非线性。仿真结果表明所设计的高线性度CMOS自举开关的SFDR达101.5dB,可以适用于16位精度的ADC应用要求,非常适合应用于高速高精度模数转换器中。

[1]Allen P E, Holberg D R, Razavi. CMOS Analog Circult Design[M]. New York:Holt, Rinehart and Winston,1987.

[2]TOdd L B, David H R, Daniel F K, et a1. A cascaded Sigma-delta pipeline A/D converter with 1.25 MHz signal bandwidth and 89 dB SNR [J]. IEEE J Sol Sta Cire,1997,32(12):1896-l906.

[3]Andrew M A,Pau1 R G. A 1.5V 10-bit 14.3 MS/S CMOS pipeline analog to digital converter[J]. IEEE J Sol Sta Circ, 1999,34(5):599-606.

[4]Dessouky M, Kaiser A. Input switch configuration suitable for rail-to-rail operation of switched opamp circuits[J]. Elec Lett,l999,35(1):8-10.

[5]Troutman P R. VI SI limitations from drain-induced barrier lowering[J]. IEEE Trans Elec Dev,1979,26(4):461-469.