基于FPGA技术的涡流信号数字阻抗分解的设计与实现

2024-08-01孙伟成

关键词:FPGA;涡流信号;阻抗分解中图分类号:TP274;TN741 文献标识码:A

0 引言

随着国家对工业发展的需求越来越大,涡流检测技术发展也越来越快。其具有非接触、灵敏度高、检测速度快等优点,是工业无损检测中的主要检测手段。在涡流检测系统中,提取检测信号中的缺陷信号是最主要的步骤。目前,市面上大部分涡流检测系统和设备主要利用阻抗分解的原理进行设计。因此,研究涡流信号的阻抗分解方法具有非常重要的意义。传统的涡流信号阻抗分解方法主要采用硬件电路进行处理,即通过搭建模拟电路以实现涡流模拟信号的处理。这种方法不仅具有硬件电路系统复杂、调试难度大、系统通用性和稳定性差等不足,而且涡流信号容易受噪声信号的干扰,检测信号质量差,测量精度较低。随着计算机技术和数字处理系统的发展,数字化发展成为一种趋势。其中,采用大规模现场可编程逻辑门阵列(field programmablegate array,FPGA)技术可以实现涡流信号阻抗分解的数字化处理,其具有设计灵活、适应性强、模块化移植简单等高性能数字处理的特点。采用先进的数字处理方法实现涡流信号的阻抗分解成为一种可能。

1 涡流信号阻抗分解的原理

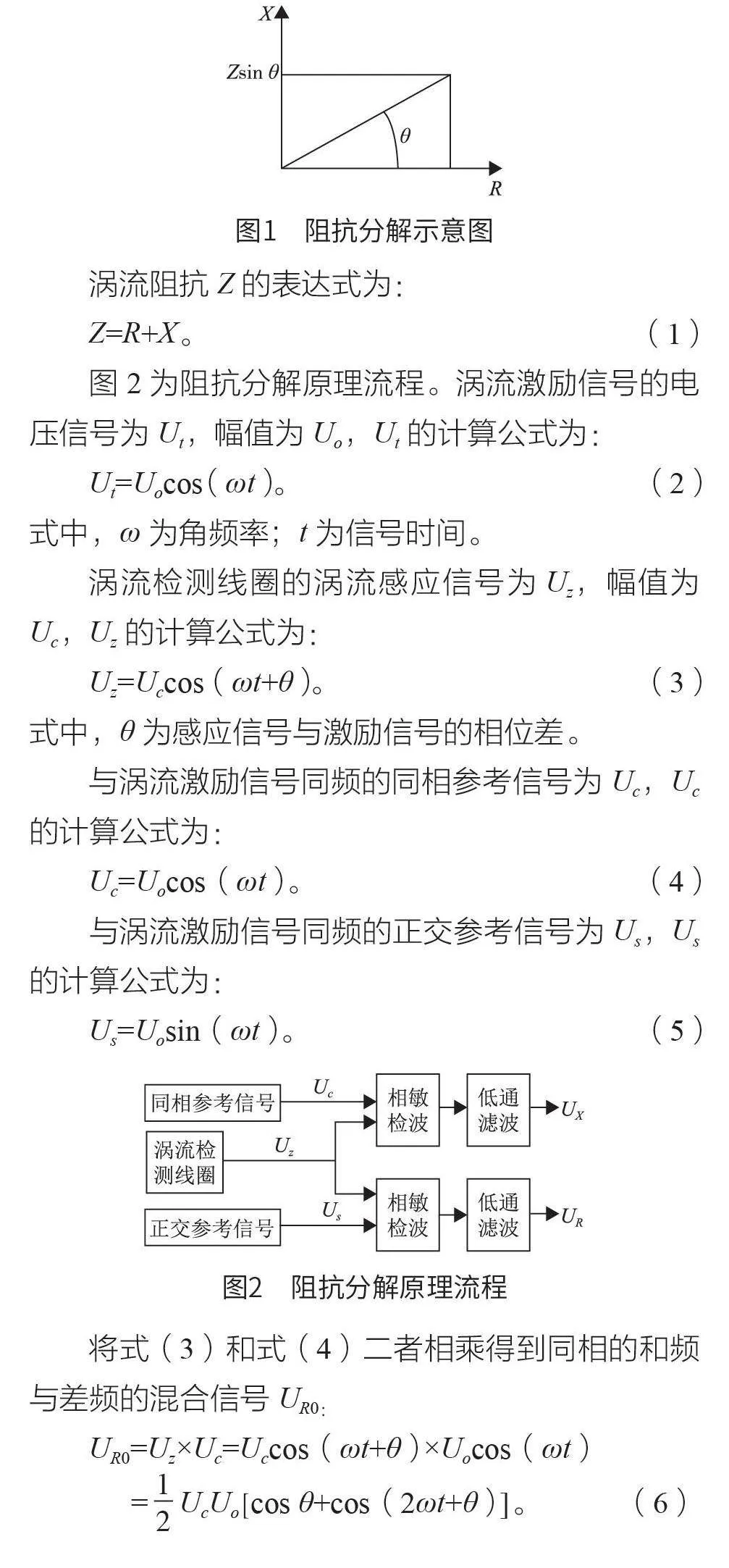

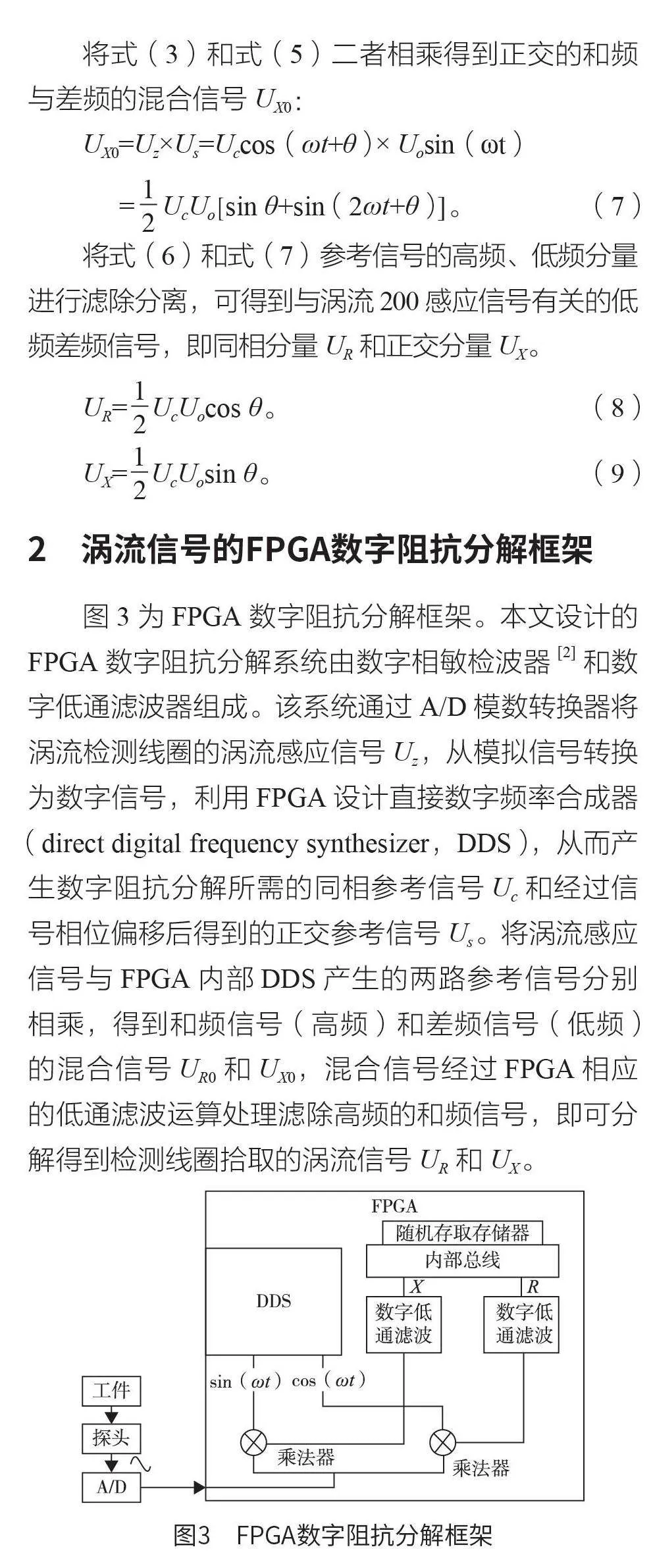

涡流检测技术是利用检测线圈来拾取被检工件表面的涡流信号变化,通过对涡流信号进行阻抗分解来反映被检工件表面阻抗的变化,从而反演出工件表面是否存在缺陷以及缺陷的大小和性质[1]。因此阻抗分解是涡流信号处理的关键环节。图1 为阻抗分解示意图,阻抗分解的原理是将检测线圈拾取的涡流信号进行正交分解,分别得到涡流信号的实部(电阻分量R)和虚部(感抗分量X),从而实现涡流信号的阻抗分解。

3 数字相敏检波器的设计与实现

本文主要利用FPGA 技术设计两个产生正交参考信号的DDS 来实现数字相敏检波处理[3-4]。将标准正弦波幅度数据存储在FPGA 的只读存储器(read only memory,ROM)中。通过输入不同频率对应的频率控制字做累加算法,将结果作为ROM的查询地址,即可输出正交参考信号幅值。图4 为FPGA 逻辑分析仪抓取的正交参考信号。

将正交参考信号幅值与A/D 模数转换器得到的涡流感应信号进行相乘,即可实现数字相敏检波处理。本文采用FPGA 自带的乘法器IP 核实现乘法运算。

4 数字低通滤波器的设计与实现

式(6)和式(7)相乘后的结果中含有一个倍频的高频分量,可以使用数字低通滤波器来去除这个分量[5-6]。假设涡流激励信号频率为1000 kHz,则其倍频分量为2000 kHz,因此需要设计一个截止频率为 1000 kHz 的低通滤波器滤除倍频高频分量。本文使用MATLAB 工具,设计数字低通滤波器,采用Hamming 窗函数法来实现数字低通滤波器参数计算,得到阶数为31 阶的低通滤波器模型。使用MATLAB 工具对该数字低通滤波器模型进行幅频响应分析,如图5 所示。

将该数字低通滤波器模型系数输入FPGA 低通滤波器的代码中,实现数字低通滤波功能,完成涡流数字阻抗分解的重要环节。

5 涡流信号数字阻抗分解实验验证

为了验证涡流信号数字阻抗分解的有效性,将该设计方案的涡流检测系统激励信号频率设置为500 kHz, 发射挡位为 3挡, 前置放大增益为12dB,以 0.2m/s 的速度检测不锈钢钢板试块上宽为0.2 mm, 长为20mm, 深分别为0.2mm、0.5mm、1mm 的缺陷。经过系统软件处理,将阻抗分解后的数据波形显示在笛卡尔坐标系上并且以阻抗信号的形式表示[7]。根据实部和虚部的变化,显示检测线圈涡流阻抗信号变化。涡流阻抗信号如图6 所示,阻抗信号幅值大小与裂纹大小呈正相关,实现了涡流信号的阻抗分析,达到预期设计效果。

6 结论

本文在阐述涡流信号阻抗分解原理的基础上,详细地介绍和分析了基于FPGA 技术的涡流信号数字阻抗分解系统的设计步骤和实现方式,并利用实验验证了该设计方法的有效性,具有良好的实用价值。