基于FPGA的访问控制列表并行查找设计与实现

2024-06-03许芮铭

许芮铭,武 刚

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引言

一直以来,公共机构、大型团体、企业等对网络信息传输的安全性都有较高的要求,在其网络系统中部署的网关、防火墙等均以网络访问控制技术作为实现相关安全功能的核心技术之一[1-2]。具有网络访问控制技术的设备在收到报文后,提取关键字并送入访问控制列表进行查表,根据匹配结果实现报文控制。访问控制列表的查表性能、表项数量等,直接决定相关设备的吞吐率、处理时延、规则数量等核心性能指标[3]。随着5G、光通信等网络通信技术的不断发展,大数据、云计算、远程办公等应用获得爆发式增长,网络规模大幅度扩张,业务复杂度提高,网络节点间的通信带宽大幅增加,对网络设备中访问控制列表的性能需求也随之水涨船高。

访问控制列表的实现方式主要有三态内容寻址存储器(Ternary Content Addressable Memory,TCAM)、散列表、FPGA等[4]。TCAM方案查表性能强,容量较大,但存在成本高、功耗大的问题[5]。散列表方案在范围匹配、模糊匹配等场景中,需要复杂的映射和管理[6]。FPGA方案性能较低,表项数少,使用范围受限[7]。IPv6地址的大位宽给FPGA方案的表项存储和匹配逻辑设计均带来了挑战。本文提出了一种改进的可扩展FPGA实现方案,采用优化的并行查找设计,改进的表项组织,有效提升了表项匹配性能,大幅增加了表项数量,可支持10 Gbps以上网络吞吐率,数千条IPv6范围匹配规则,大幅扩展了FPGA方案的适用场景。

1 访问控制列表工作原理

访问控制列表的基本工作原理如图1所示,主要分为关键字解析和提取、查表控制、表项存储、数据缓存、处理决策等。设备从端口接收到网络报文后,首先进行报文头解析和五元组提取,并将报文暂存至数据缓存中[8]。访问控制列表的查表控制模块利用五元组关键字,通过读取规则表项进行匹配:若匹配吻合,则表明命中规则;若全部失败,则表明未命中。当同时命中多个规则时,模块选取优先级最高的规则。根据查表结果,处理决策单元将报文从数据缓存中读出并分发至相应的功能模块,实现对报文的转发、丢弃、上传等操作。设备的管控单元通常使用CPU实现,根据用户的输入生成访问控制列表的表项,实现表项的增、删、查、改等管理功能。

图1 访问控制列表的基本工作原理

2 访问控制列表的FPGA实现

2.1 访问控制列表存储与匹配单元设计

访问控制列表的规则表项存储在FPGA芯片内嵌的块存储器(Block Random Access Memory,BRAM)中,规则的匹配采用线性比较器,即比较器依次从BRAM中读出表项,并与查找请求中的五元组匹配,完成遍历后输出结果。为充分利用存储资源,需要针对性设计表项格式。以XC7K325 T FPGA为例,其BRAM以36 Kb为一个最小单元,深度最小为72 Bit×512的形式。由于存储表深度越深,线性比较器遍历全部表项所花费时间越多。因此,需要使用尽可能小的存储表深度设置。规则表关键字为支持IPv6的五元组,其中网际互联协议(Internet Protocol,IP)地址的低4字节值使用8 Bit分别表示最大和最小值,以支持范围匹配;源、目端口号分别使用4 Bit表示最大和最小值,以支持范围匹配;具有优先级字段以区分不同优先级。规则表采用IPv4兼容地址设计,因此可以支持IPv4/v6双栈,且IPv4支持全地址范围匹配。

以太网最小报文长度为64 Bit,10 Gbps速率时最小报文的包频率约为14.881 Mpps,平均每个报文传输时间约为67 ns。当FPGA工作频率为250 MHz时,单周期时间为4 ns,遍历512 Bit深度的BRAM需要2048 ns,这段时间内,满带宽情况下大约有30个报文到达设备需要处理,因此,单个比较单元需要能同时最大处理30个报文。

匹配单元功能实现如图2 所示。该模块例化1个BRAM作为规则表存储单元,还有查表请求分发逻辑、请求缓存、匹配逻辑以及查表结果输出逻辑。请求缓存和匹配逻辑一一对应,其数量可以通过参数进行配置,以实现不同的查找并行度。匹配单元循环读取规则表存储单元中的表项内容,并提供给匹配逻辑进行关键字比较使用。输入的查表请求通过查表请求分发模块,依次送往各个缓存,同时进行关键字匹配。每个查表请求在遍历完所有表项后,又通过查表结果输出逻辑按顺序依次输出,形成并行操作。进行遍历时,匹配单元模块始终采用高优先级命中结果覆盖低优先级结果的方法,确保最终命中输出的一定是最高优先级的规则表项。

图2 匹配单元功能实现设计

2.2 可扩展的并行查找设计实现

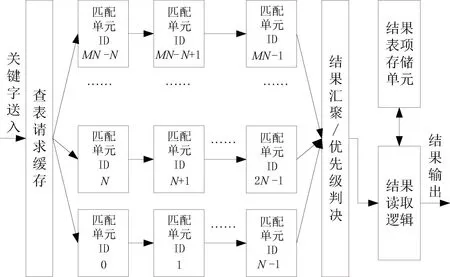

可扩展的并行查找设计将匹配单元首尾相连,即可形成一个流水查找处理链,实现规则表项数量的扩展。考虑到过长的流水深度会导致查找时延过大,本文所提方案并行例化多条流水查找处理链,形成二维的匹配单元阵列,可在流水深度较低的情况下实现大规模的规则表项,其实现架构如图3所示。

图3 可扩展二维并行匹配处理矩阵架构

流水级数和并行数都可以通过参数配置实现快速可扩展重构,以确定不同规则表项数量,当流水级数为N,并行度为M时,可以实现85×N×M条表项数量。每个匹配单元均根据其在矩阵中的位置配置一个独特的模块编号mod_id,以实现规则表项的编号和访问。查表关键字送入请求缓存后,同步送往多条并行的流水查找处理链中,经过多级匹配,最终输出各条链路中优先级最高的命中结果。在结果汇聚和优先级判决模块中,本文所提方案再次根据优先级选择出查表结果。根据命中标志和索引值,结果读取逻辑从一个统一的结果表项存储单元中读出规则表对应的处理方式,作为最终的查表输出。

3 实现结果

测试访问控制列表并行查找功能,选用的型号为XC7K325 T,该型号为网络通信处理领域中大量应用的主流型号,具有326000个等效逻辑单元、12.5 Gbps收发器,可支持10 Gbps速率的网络协议处理,具有一定的典型性。访问控制列表功能单元的设计参数设定为如下:匹配单元采用8×8的二维矩阵,最大支持的规则表项数为5440个,匹配单元中的并发匹配逻辑设计为30个。

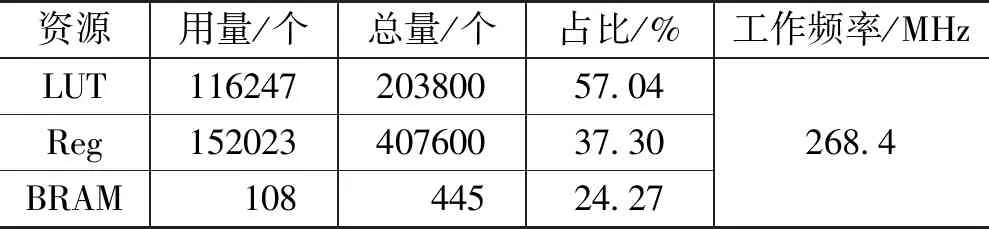

经过开发工具的综合以及布局布线,得到的FPGA逻辑、存储资源消耗以及运行频率如表1所示。可以看到,该芯片实现相关查找功能的资源占用较为宽裕,工作频率也较高,这说明该设计在支持表项数、查找性能等关键技术指标方面还有一定的提升空间。

表1 FPGA资源占用与工作频率情况

测试环境采用网络测试仪生成网络业务流,采用单板环回的方式进行性能测试评估,利用评估板的板载SFP+网络接口与网络测试仪的10 Gbps以太网接口进行环回互联。通过计算机控制终端向评估板下发5440条不同的五元组规则策略,并对网络测试仪配置对应五元组的网络流。评估板收到报文后,经过查表再将对应报文环回到网络测试仪中,以此来评估查表性能。

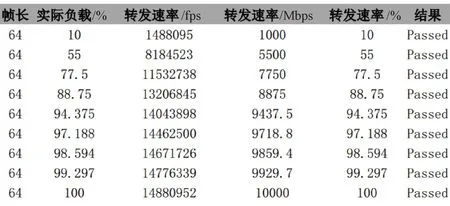

运行满足RFC2544标准的包吞吐率测试,得到如图4所示的测试结果。可以看到本模块可以支持长度为64 Bit的IP报文在10 Gbps以太网中的100%带宽通信查表需求。

图4 查表性能测试结果

4 结语

本文提出了一种利用FPGA实现的访问控制列表并行查找设计方案。所提方案通过改进表项存储格式和匹配方式,充分利用了FPGA中BRAM的存储容量,可以支持较大规模的IPv6范围匹配五元组规则表项。本文所提方案通过并行匹配逻辑提升了查表处理性能,采用可扩展的二维并行匹配处理矩阵的架构,可以在不影响查表性能的情况下,灵活地实现表项数量的扩展。经过测试,该方案可以在XC7K325 T上,实现超过5000条规则表项,并支持10 Gbps的以太网通信速率,且相关实现具备进一步提升规模和性能的潜力。