面向FLASH存储器应用的电压自举电荷泵电路设计

2024-04-10陈智峰陈煌伟陈继明陈铖颖黄渝斐

陈智峰,陈煌伟,陈继明,陈铖颖,黄渝斐

(厦门理工学院光电与通信工程学院,福建 厦门 361024)

随着平板电脑、智能手机等便携式设备的快速发展和大力普及,人们对于移动存储设备的要求在不断提高,也对非易失性存储器提出了新的要求。FLASH存储器作为非易失性存储器最为重要的门类,得到了广泛的应用[1]。电荷泵是一种高电压发生电路,它被广泛应用于非易失性存储器电路中,其作用是提升电源电压,实现存储器的擦除和重复编程。电荷泵是存储电路的重要组成部分,其输出电压纹波的大小直接影响存储信息的精确性[2-3]。在电源管理模块中,如何降低电荷泵的功耗是设计者所需要重点考虑的因素。因此,设计一个转换效率较高的电荷泵对于降低存储器的功耗具有重要意义[4]。

从 Dickson 电荷泵发展至今,出现了多种电荷泵的拓扑结构。其中,开关电容型电荷泵因具有效率高和电路结构稳定的特点,受到了越来越多设计者的青睐。在该结构设计过程中,开关管栅极电压可能会小于开关管源漏极电压,这导致开关不能完全打开或关闭。为了保持栅极完全导通,同时尽可能减小导通电阻,提高输出效率,在升压过程中栅极需要具有较高的电压。为解决这一问题,文献[5]提出了一种栅极增压开关结构。然而,由于该电荷泵需要具备5 mA的带载能力,需要很大的开关管的尺寸,增加了整体的版图面积和功耗。文献[6]提出了一种通过输出正负电压的电荷泵结构来增加时钟频幅,并通过将电荷泵的两端输出连接到振荡器,再连接到电荷泵开关管栅极来实现。而文献[7-8]则提出了通过添加二倍器以增加时钟频幅来解决这一问题。但是,这种方法仅适用于级联数小的电荷泵,当级联数较大时,通过二倍器增加的时钟频幅可能不足以开启开关管,因而降低了电荷泵的效率。基于以上考虑,本文设计了一款具有高电压选择电路的FLASH 存储器的闭环电荷泵升压电路,通过高电压选择电路进行开关管电压的栅压自举,产生了高效率且低纹波的输出。

1 电荷泵电路架构

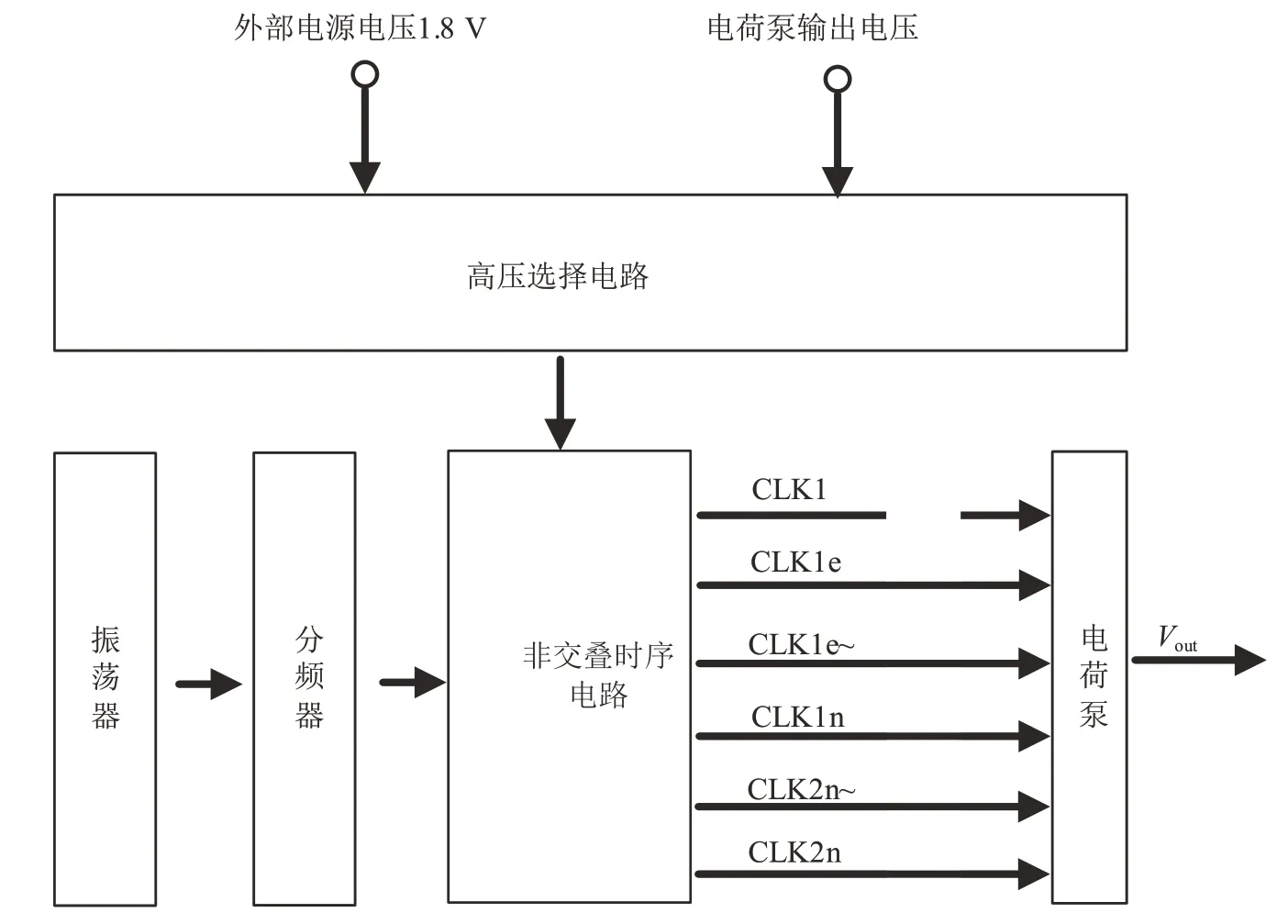

本文设计的电荷泵架构如图1所示,它主要由振荡电路、分频电路、非交叠时序电路、电荷泵和高压选择电路组成。在Flash 应用中,电路对频率的要求不高,因此电荷泵采用环形振荡器作为振荡器,并使用D触发器构成的分频器进行分频。该电路的工作方式为:振荡电路生成方波信号,经过分频器分频成为电荷泵所需的开关频率,然后非交叠时序电路生成电荷泵各个开关所需的时序,进而由电荷泵产生高电压。

图1 电荷泵架构框图Fig.1 Charge pump architecture

高电压选择电路的目的是为了确保电荷泵电路在工作时,MOS 管的栅压保持高于源漏电压,避免漏电,影响电压输出。高压选择电路的设计保证了电荷泵的工作效率,同时确保了电压的稳定性。此外,电荷泵的工作状态也可以通过监控Vin和Vout的电压差来控制。这种设计可以保证电荷泵的工作效率和稳定性。

2 电路设计

2.1 电荷泵电路

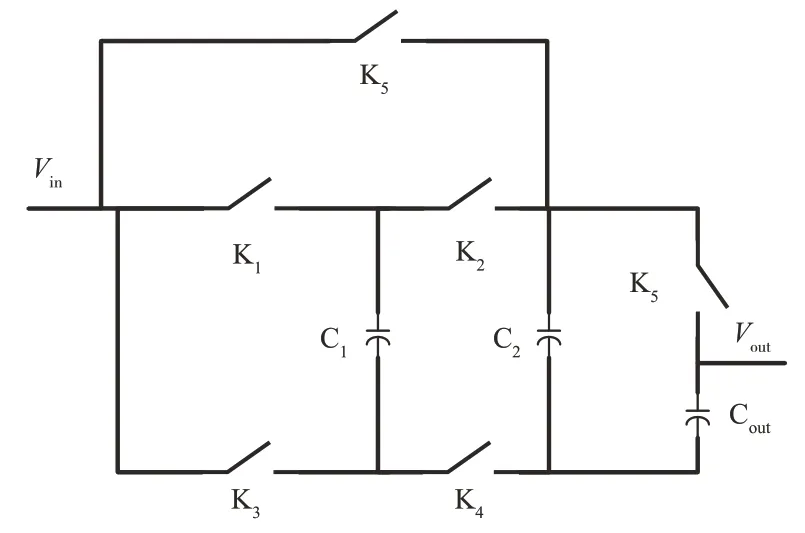

根据文献[9]进行理论推导,电荷泵工作分为充电阶段、跳变阶段和输出阶段3个阶段。

1)充电阶段。开关K1、K4、K5处于闭合状态,其他开关处于断开状态。C1和C2电容的上极板电压为Vin,电容两端的电荷总量为

2)跳变阶段。开关K2和K3保持闭合状态,而其他开关均处于断开状态。由于C2电容两端电压不能立即发生跳变,因此C1电容上极板被Vin充电到2Vin,然后C1电容上的电荷被转移到C2中进行平均分配。此时,两个电容上的电荷总和为

3)输出阶段。由上述两个阶段的电荷守恒可得,在跳变阶段后期,开关K6在短暂的时间内导通。在这个瞬间,泵电容C1和输出电容C2的电荷被转移到输出电容Cout上,最终Cout的电压达到Vout。

由文献[10]得,输出电压纹波是由升压电容C2导通时的大小引起的,即

式(4)中:Vripple为输出电压纹波;Ipump为跳变阶段电荷泵的电流;Fclk为开关频率;Cload为负载电容。升压电容为图2中的C2电容。

图2 电荷泵原理图Fig.2 Charge pump schematic

电荷泵的输出效率[11]可表示为

式(5)中:IL是输出的电流;Vout是输出的电压;Iin是输入电流;VDDA是电源电压;Pout是输出效率;Ploss是损失效率。

该结构无需反馈调节和频率环路补偿,大大降低了设计的复杂性。此外,电路没有skip模式调节引起的过大纹波,并具有较大的负载能力、较高的效率和最小纹波。

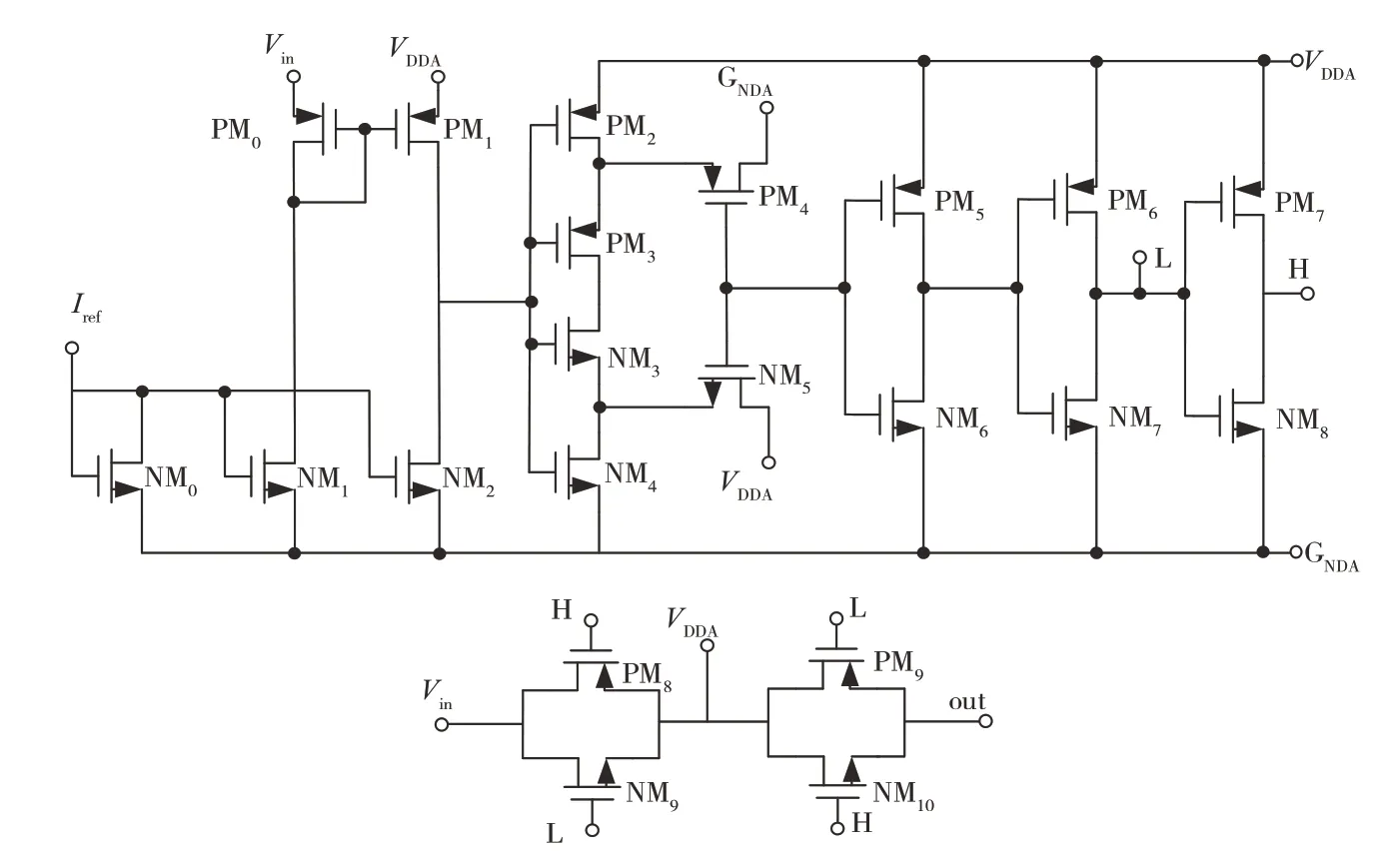

2.2 高电压选择电路

本文的高电压选择见图3。在本文电路设计中,当Vin大于电荷泵的Vout时,时钟的高电平由VDDA源控制。相反,当电荷泵的Vin小于Vout时,时钟的高电平由Vout控制。该电路的主要组成部分包括纳安级偏置电路、电压比较电路及施密特触发器。这些部分由反相器提高驱动能力处理后,通过L、H 两个信号控制的开关选择输出为Vin或Vout。电路的工作原理为:Vin与VDDA经过PM0和PM1的处理,若Vin大于VDDA,PM1截止,NM2的导通将地信号传递至节点A,从而使得节点A输出0电压。若Vin小于VDDA,PM1导通,VDDA即被传入节点A,从而使得节点A 输出VDDA。继而,节点A 的输入信号经过施密特触发器,被整形为方波,并产生如下数字逻辑:当Vin大于VDDA时,施密特触发器输出低电平;当Vin小于VDDA时,施密特触发器输出高电平。接着,反相器对波形进行二次整形,最终产生了相位相反的两相方波信号,用以控制两个CMOS开关。这些开关决定了是将电源电压Vin输出给VDDA,还是将电荷泵电压Vout输出给VDDA。

图3 高电压选择图Fig.3 High voltage selection circuit

高电压选择电路的out 端口连接时钟模块的电源,高电压选择电路作为解决方案具有明显优势。它解决了开关电容型电荷泵中开关管无法完全打开或关闭的问题,确保栅极具备足够的电压来保持完全导通状态,从而使得电荷泵的效率得到了提高。此外,高电压选择电路在满足带载能力的同时,实现了较小的开关管尺寸,从而减小了整体版图面积,并降低了功耗。而且,它能够适应较大级联数的电荷泵,提供足够的时钟频幅来驱动开关管,进而提高电荷泵的效率。

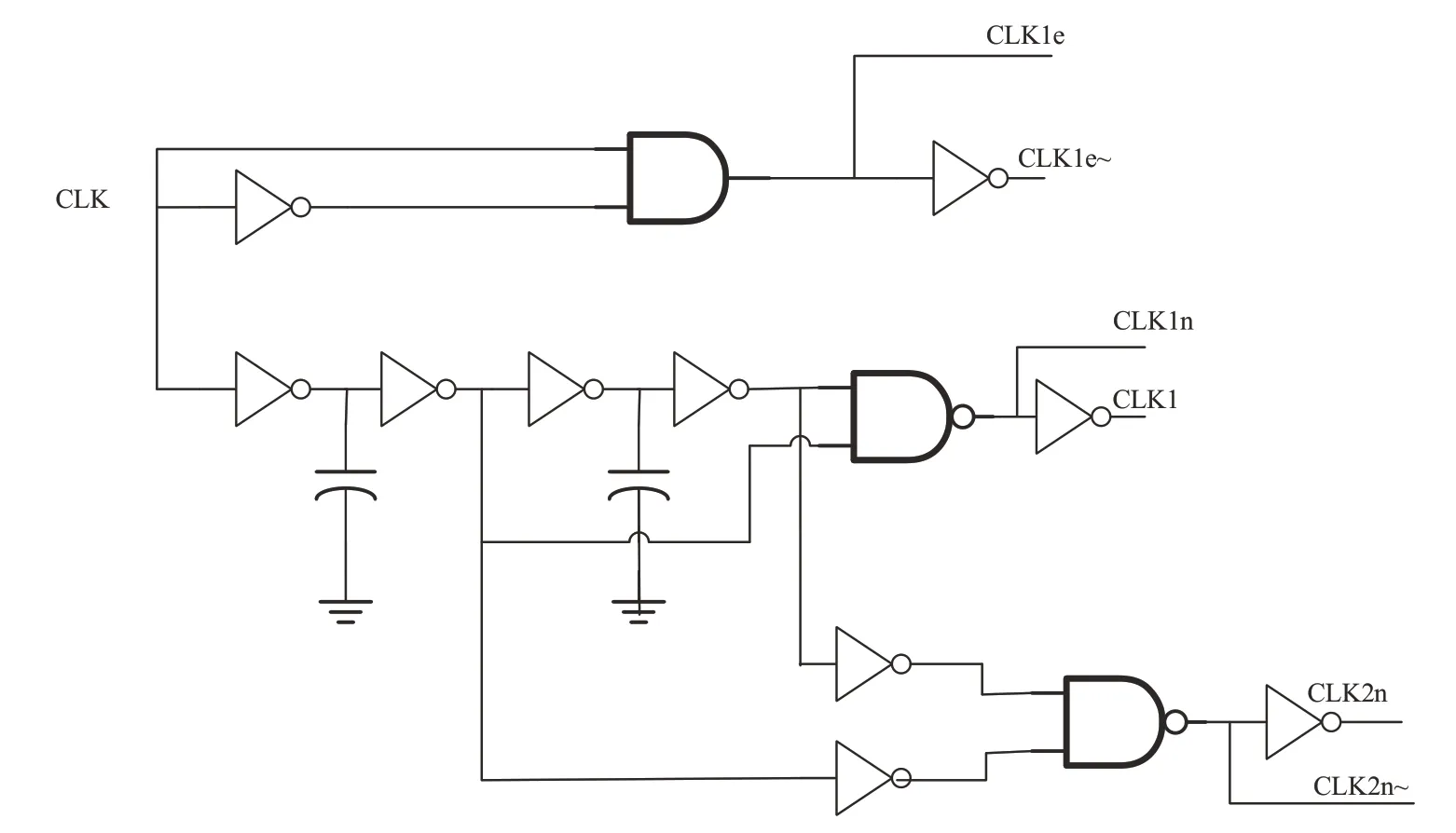

2.3 非交叠时序电路

为了保证电路的稳定性,避免因为同时导通的开关造成死区,产生电荷回流现象,在设计电路时必须采用非交叠时序电路。非交叠时序电路要求每个阶段结束后,所有的开关都应该闭合。电荷泵需要的时序由反相器和倒比管生成延时,经过不同时序的信号通过与门和非门输出。本文的非交叠时序电路见图4。

图4 非交叠时序电路Fig.4 Non-overlapping timing circuit

同时,非交叠时序电路可以预防死区现象的发生,使得电路的稳定性得以提高。死区是电路中的一种现象,它造成了电路的不稳定,甚至导致电路的故障。因此,采用非交叠时序电路是电路设计的必要步骤。

3 仿真结果与分析

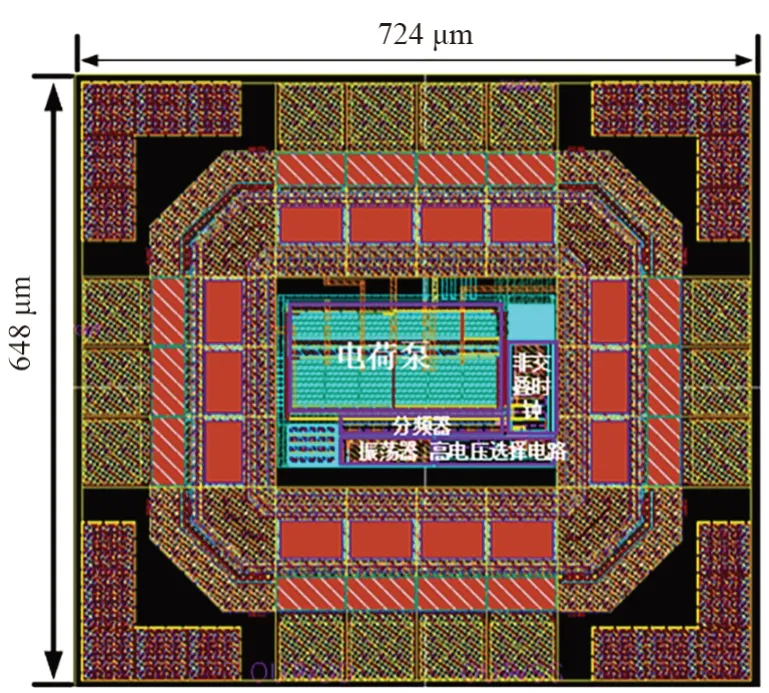

电荷泵电路采用中芯国际CMOS 0.18 μm 1P6M 工艺进行设计。电源电压为1.8 V,电路版图见图5,面积为724 μm×648 μm。

图5 电荷泵整体版图Fig.5 Charge pump layout

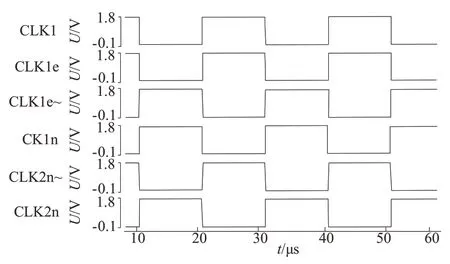

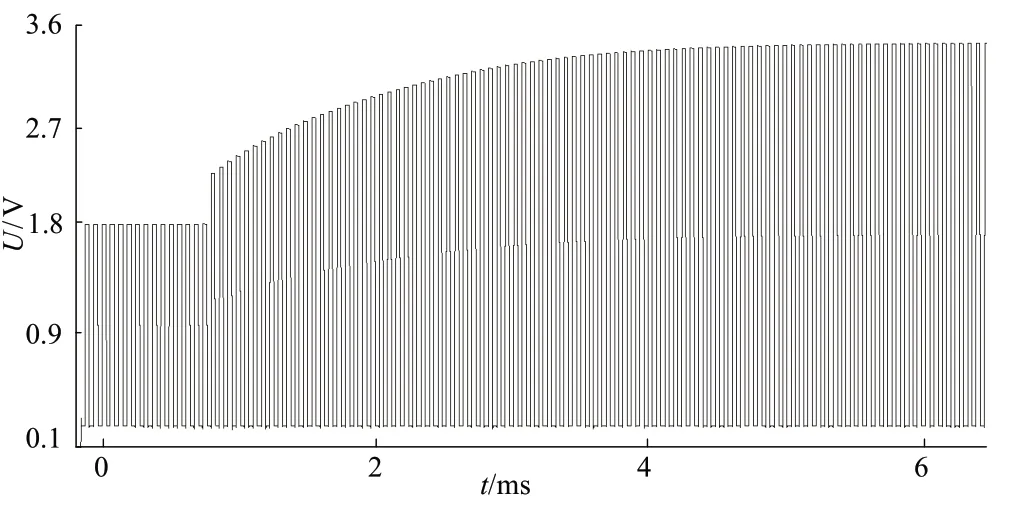

仿真结果见图6~图7,可见非交叠时序电路正常工作,时钟信号稳定。在高电压选择电路的作用下,时钟电压实现了栅压自举。电荷泵的输出信号仿真结果也证明了高电压选择电路的正确性。同时,电压纹波的仿真结果证明,高电压选择电路有利于输出电压稳定性的提高。因此,本电路通过和高电压选择电路的配合使用,可以提高电荷泵的输出电压,同时保证整体电路内部信号的稳定。需要注意的是,在应用过程中,需要进一步评估电荷泵的稳定性和电压纹波对系统性能的影响,以便对系统进行更进一步的优化。

图6 非交叠时序Fig.6 Non-overlapping timing

图7 时钟栅压自举输出Fig.7 Clock gate voltage bootstrap output

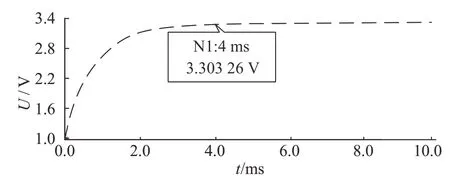

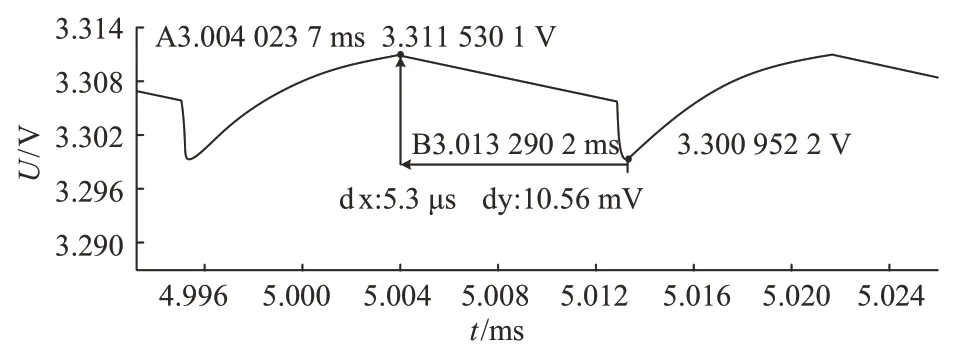

电荷泵输出电压如图8 所示。由图8 可见,在电源电压为1.8 V、带载为5 mA 的情况下,电荷泵的输出电压达到3.3 V,这主要得益于高电压选择电路的配合使用。如果没有使用高电压选择电路,电荷泵的输出电压只能达到2.5 V。此外,对输出的电压纹波进行了仿真,结果见图9。由图9 可见,电压纹波大小仅为10 mV,说明高电压选择电路不仅提高了电荷泵的输出电压,而且还提高了输出电压的稳定性。

图8 电荷泵输出电压Fig.8 Charge pump output voltage

图9 电荷泵输出纹波Fig.8 Charge pump output ripple

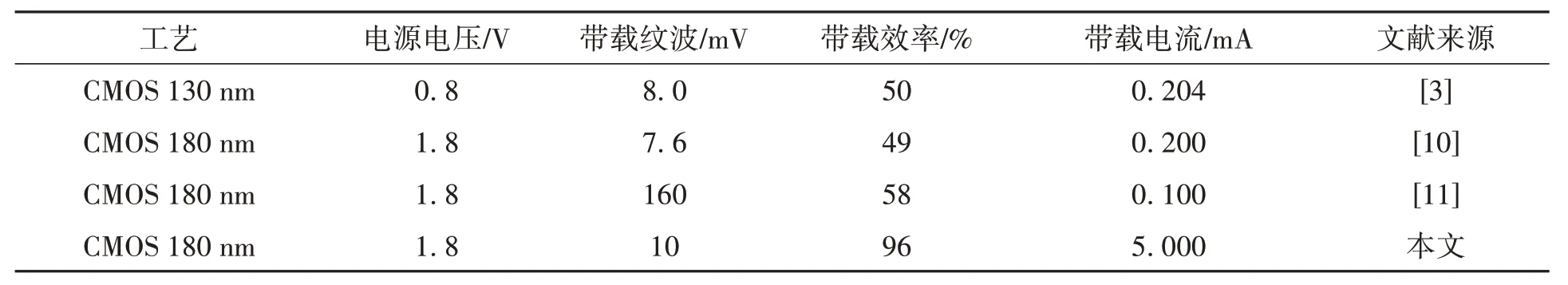

将仿真结果与近几年来相关文献设计结果进行比较,结果见表1。由表1 可见,在小带载电流情况下,文献[3]和文献[10]的设计虽然纹波小,但是带载效率很低。而本文设计的电荷泵在具有较大负载电流能力的同时,输出纹波与二者相当,且在较小带载电流时,可实现更小的纹波值。这表明本文电荷泵具有更好的稳定性。此外,得益于高电压选择电路与电荷泵升压模式的配合,转换效率也明显高于其他文献设计的结果。

表1 电荷泵电路性能参数比较Table 1 Comparison of performance parameters of charge pump circuits

4 结论

本文基于SMIC 0.18 μm 1P6M 工艺,设计了一款用于FLASH 存储器的自举升压电荷泵电路。相比于传统的电荷泵电路,本文设计的电荷泵采用开环无反馈结构,通过调整电容比值,满足了不同的输出升压需求。此外,电路采用高电压选择电路,能够实现电压自举,进一步提高了效率。仿真结果表明,在电源电压为1.8 V、带载为5 mA、内部电荷泵开关频率为50 kHz时,高电压选择电路正常工作,输出电压为3.3 V,纹波小于10 mV,效率达96%,可满足Flash存储器的升压需求。