基于SiGe BiCMOS 的全集成射频功率放大器设计

2024-03-25傅海鹏项德才

傅海鹏 ,项德才

(天津大学 微电子学院,天津 300072)

射频功率放大器位于无线发射机末端,是无线通讯系统最重要的组成部分之一.其主要功能是把基带处理后的信号在一定的线性度范围内放大至指定的功率,并传递到天线负载.无线收发系统的主要能量消耗是功率放大器造成的,其效率会对便携式设备的电池寿命造成影响.并且,以热形式耗散的能量会使整个系统温度升高,因此热稳定性也是功率放大器的重要指标.目前,相对成熟的用于实现功率放大器的工艺有GaAs 异质结双极晶体管(Heterojunction Bipolar Transistors,HBT)、射频绝缘体上硅(Radio Frequency Silicon on Insulator,RF SOI)和SiGe 双极互补氧化物半导体(Bipolar Complementary Metal Oxide Semiconductor,BiCMOS).GaAs HBT 具有高线性度、高电流密度和高击穿电压的优点,但是GaAs 衬底的导热率较低,因此需要进行可靠的热稳定设计以防止功放失效.此外GaAs HBT 工艺可供使用的器件相对较少,往往需要额外的CMOS 芯片来提供电源和控制,这导致GaAs 功放整体集成度较低.RF SOI工艺具有较高的集成度和衬底隔离度,适合制作低噪声电路,但SOI 衬底导热率极差,因此高功率功放利用RF SOI 工艺实现难度较大.SiGe BiCMOS 工艺集成了SiGe HBT 和标准CMOS 工艺,既具有HBT 的高电流密度和高击穿电压的特点,又可以片上集成CMOS 电源和控制电路,适合制作全集成功率放大器.

芯片的面积大小意味着成本的高低,如何利用有限的芯片面积实现更高的功率、增益和线性度是研究功率放大器的重要方向之一.胡锦等[1]采用 180 nm SiGe BiCMOS 设计了一款全集成功率放大器,输出功率高达27.73 dBm,但采用三级共发射极(Common Emitter,CE),面积较大.Ruan 等[2]采用两级CE 级联,面积仅为1.15×1.14 mm2,功率增益可达27.3 dB,但是其片上未集成CMOS 电源,电路性能受温度和供电纹波影响较大.Reynier 等[3]采用SOICMOS工艺,5 V供电下饱和功率为35.1 dBm,功率增益为29.5 dB,片上集成CMOS电源,最高工作温度达85 ℃,但其封装较复杂,成本较高.

针对上述问题,本文提出了一种基于0.35 µm SiGe BiCMOS 的功率放大器.设计采用cascode 驱动级和CE 功率级级联,减少面积的同时提高功率增益.此外,片上集成CMOS 电源以提供稳定的电流偏置.测试结果表明所提出的功放具有较高的增益和线性输出功率以及较好的热稳定性.

1 电路分析与实现

1.1 电路结构设计

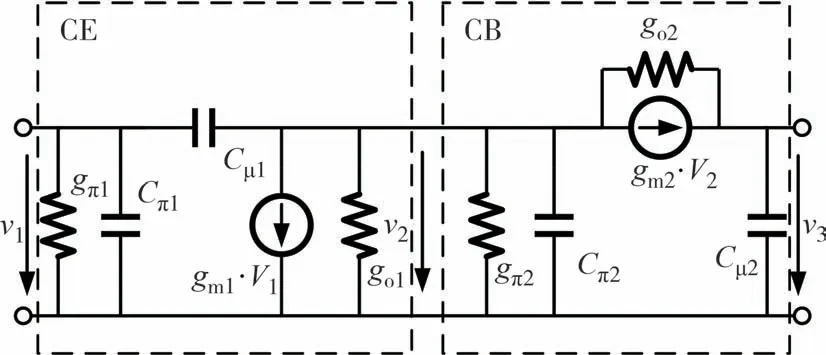

为达到较高的功率增益,功放一般采用多级结构,由驱动级和功率级构成.驱动级将输入的信号初步放大,使其具有一定的功率从而推动功率级.本设计的目标增益为30 dB,考虑设计余量为2 dB,仿真增益需要达到32 dB.本文采用的工艺下的CE 增益约为17 dB,考虑到全片上匹配的损耗较大,每一级匹配的损耗约为2 dB.若采用两级CE 结构,两级放大器的有源部分贡献约34 dB 的增益,输入、级间和输出各贡献2 dB 的插入损耗,则至多得到28 dB 的增益,无法满足设计指标.如采用CE,那么至少需要三级级联,即驱动级由两级CE 构成.由于每两级间需要进行级间匹配,三级级联则需要两个级间匹配,用于实现阻抗变换的片上电容和电感将占用大部分面积,这不利于芯片的小型化.图1为cascode结构小信号模型,为了更加直观对比CE 与cascode 结构电压增益,忽略输入电导gπ1与gπ2及结电容的影响,可得到

图1 cascode结构小信号模型Fig 1 Small signal model of the cascode structure

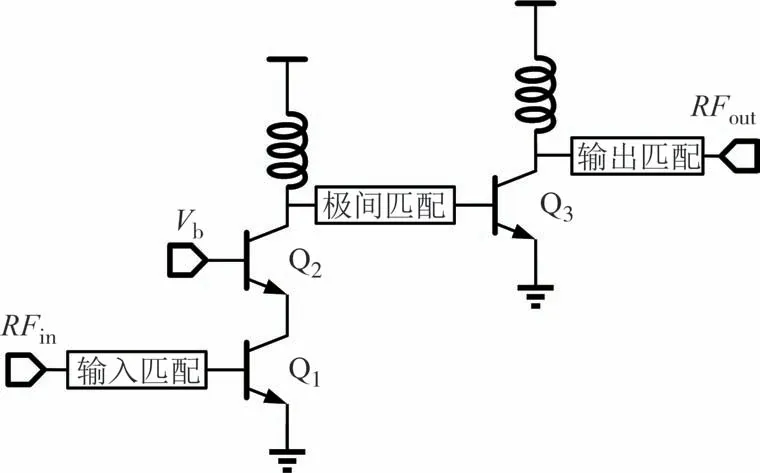

式中gm与go分别为晶体管的跨导与输出电导,对比两式可直观的看出cascode 结构的电压增益Acas为CE 结构电压增益ACE的gm2/go2倍.本文采用工艺下的cascode 结构的仿真增益约为21 dB,按照上文所述进行计算,含全片上匹配损耗的两级放大器总增益为32 dB,可以满足设计要求.因此本设计采用cascode 驱动级和CE 功率级级联.如图2 所示为电路的整体结构.

图2 电路的整体结构图Fig 2 The overall structure diagram of the circuit

1.2 CMOS电源

由于GaAs HBT 功放偏置电路的参考电流需要片外CMOS 芯片提供,这大大降低了放大器的集成度,提高了成本.为节省成本,可以选择采用简单的电压加电阻形成的简易电流源提供参考电流,但是晶体管和电阻均具有一定的温度系数,当温度变化时参考电流会发生变化,并且外界供电的纹波也会引入噪声,从而影响放大器的偏置状态[4-5].

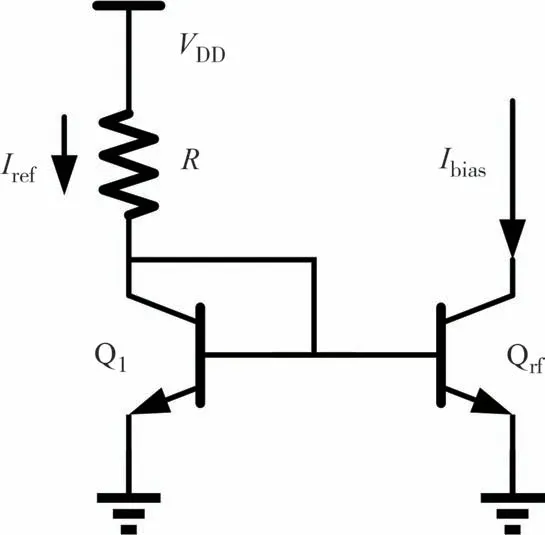

图3 为采用电阻形成的简易电流源,当供电电源的变化为ΔVDD时,偏置电流变化ΔIbias为

图3 简易电流源Fig 3 Schematic of the simple current source

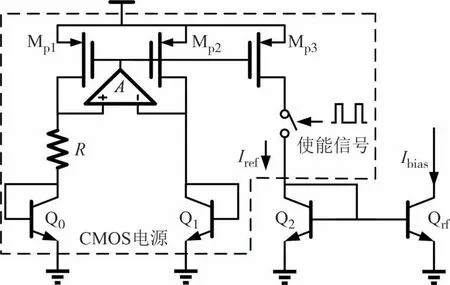

式中,EW与EL分别代表发射极宽度和长度,rf代指射频管,1 表示晶体管Q1.本设计采用SiGe BiCMOS 工艺,在片上集成了CMOS 电源以提供稳定的参考电流,图4 为CMOS 电源的原理图.MOS 管MP1、MP2,晶体管Q0、Q1,电阻R,运放A构成了基本的带隙基准电路,产生的电流经MP3倍数复制后为放大器的偏置电流镜Q2提供参考电流.此外,为满足低功耗工作的需求,该电源配备控制端,当外界使能信号为高电平时电源输出参考电流,放大器开始工作,将输入的一段包络放大;当使能信号为低电平时电源关闭电流,放大器关闭.该使能信号在测试阶段由测试使用的信号源提供,在实际应用阶段由基带芯片提供.图5 为放大器动态工作的原理图.

图4 CMOS电源原理图Fig 4 Schematic of the CMOS power supply

图5 放大器动态工作的原理图Fig 5 Schematic of amplifier dynamic operation

1.3 输出匹配设计

输出匹配的设计是功率放大器设计最重要的部分之一,其目的是实现功率放大器的最大功率传输.设计输出匹配,首先要通过负载牵引(Load Pull)确定集电极端的最佳负载Zopt,然后选择适当的拓扑将天线端的50 Ω 阻抗变化为Zopt.由于功率级功率较高,需要多个晶体管并联构成,因此输出阻抗很低,输出匹配的阻抗变换比很大,往往需要多阶结构实现.然而,片上电感不但损耗大也不便于后期调试,并且需要较大的面积,因此输出匹配往往采用片外实现.本设计为全集成放大器,采用全片上的匹配元件,具有一定的设计和调试难度.图6 为放大器的输出匹配原理图.

图6 输出匹配原理图Fig 6 Schematic of the output matching

图中L1与C1在基波频率表现为感性,在二次谐波频率谐振以减少二次谐波分量的发射.L2与C2在基波频率表现为容性,在三次谐波频率谐振以减少三次谐波分量的发射.在基波频率,匹配网络整体呈现带通特性,因此放大器具有较好的带外抑制特性.W1与W2为金丝键合线,并不参与匹配,W1超过 1 000 µm电路性能不对其敏感.

1.4 偏置电路设计

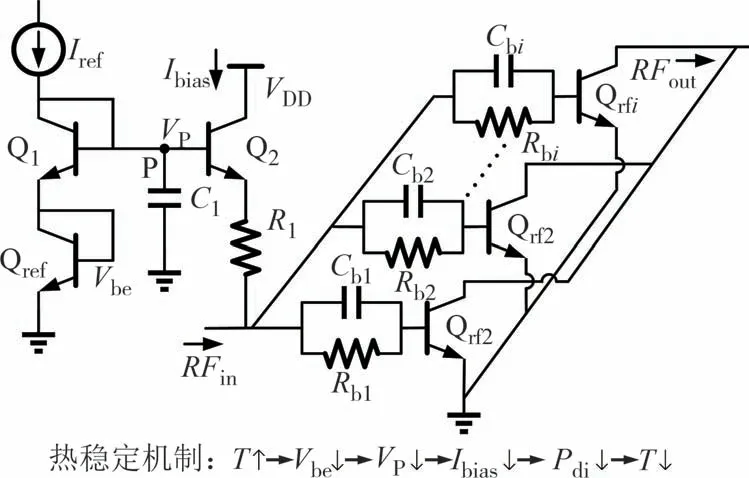

放大器若想正常工作,需要设计合理的偏置电路以提供稳定的偏置电流.但不同于小信号放大器,功率放大器处理的信号幅度变化较大,若使用一般的电流镜偏置,很难使其在较宽的输出功率范围内保持线性.Yang 等[6]提出了一种自适应的偏置电路,通过在电流镜结构的基础之上引入缓冲管来降低放大器的AM-AM(幅度)失真与AM-PM(相位)失真.本文采用该偏置拓扑,并在其基础上增加热稳定机制以提高放大器的热稳定性.图7为偏置电路的原理图.

图7 偏置电路原理图Fig 7 Schematic of the bias circuit

Q2为缓冲管,Q2与R1构成补偿结构,用于减少功率放大器的AM-AM 失真与AM-PM 失真,调节R1的大小可以控制补偿效果的强弱[7].Qref称为参考管,在实际版图设计当中需要将Qref放置在射频功率管阵列Qrf附近[8].当热耗散导致功率管Qrf温度升高时,参考管Qref温度随之升高,由于二极管结压Vbe具有负温度系数[9],Vbe下降导致P 点处的电位Vp降低,偏置电流Ibias下降,这会减小放大器的增益从而降低输出功率,热耗散的功率Pdi也随之降低,放大器的温度T下降,这样形成了一个负反馈机制,放大器温度处于一个闭环的系统,因此提高了功放的热稳定性.功率管阵列采用14 个3 指晶体管并联构成,为避免形成热点导致增益崩塌[10],设计采用了一种分布式的基极镇流电阻,如图7 中的Rbi所示.所谓分布式,即在每个3 指晶体管基极均串联镇流电阻,这样做可以使电流分布更加的均匀,热分布也更加均匀[11].为了在仿真阶段对所提出的热稳定偏置电路和分布式镇流电阻进行验证,本文采用了一种基于热阻矩阵的电路级别的热仿真控件进行电热协同仿真.基本原理为利用电仿真得到晶体管阵列中第i个晶体管热耗散消耗的功率Pdi,计算公式为

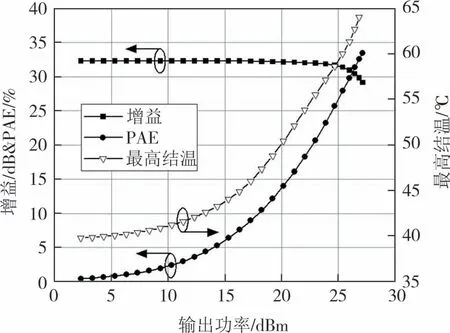

式中,Uce代表晶体管集电极与发射极间的电压降,Idi代表流经第i个晶体管未能传输到输出匹配而耗散的电流,Rthij(i≠j)代表晶体管阵列中第i个晶体管与第j个晶体管之间的热耦合电阻,单位为℃/W,可通过简单的实验获得[12-14].得到的温升ΔTi用于下一轮迭代计算,模拟实际工作中发热导致性能的变化.图8 为功放的大信号后仿结果.可以看出放大器P1dB可达25.4 dBm,此时的功率附加效率(Power Added Efficiency,PAE)为39%,最高结温小于65 ℃,未产生热点和增益崩塌,所提出的热稳定措施在仿真阶段得到了验证.

图8 大信号后仿结果Fig 8 Post-simulation results of large signal

2 整体电路与实现

电路的整体原理图如图9 所示,电路元件全片上集成,通过硅通孔(Through Silicon Via,TSV)实现接地,射频输入输出和集电极供电通过金线连接到外部.C4、C5及L4构成T 型输入匹配,整体呈现高通特性.放大器每一级的输入端均采用并联RC 结构提高电路稳定性.电路具有ESD(静电释放)防护功能,为不占用额外的面积,将其放置于打线端口下方.设计通过0.35 µm SiGe BiCMOS 工艺进行流片,整体芯片面积仅为1.25×0.76 mm2.芯片显微镜照片如图10 所示,信号从左侧进入,依次通过输入匹配、驱动级管芯、级间匹配、功率级管芯和输出匹配,最终从右侧输出.这种横向布局有效利用管芯的空间将各级匹配分离,从而避免匹配间的电磁信号干扰.CMOS 电源位于芯片边缘,远离射频主电路,且射频地与模拟地分离,这样做可以有效避免射频电路的噪声和泄露信号对模拟电路产生影响.

图9 电路的整体原理图Fig 9 The overall schematic of the circuit

图10 芯片显微镜照片Fig 10 Microscope photo of the chip

3 结果与分析

功率放大器芯片通过银浆贴在片外测试板上实现接地,其余端口通过金线键合到测试板.芯片采用3.3 V 供电,测试得到的驱动级静态电流为43 mA,功率级为74 mA.S参数测试采用安捷伦E5063A矢量网络分析仪(美国生产),测试结果与后仿结果的对比如图11所示.

图11 测试结果与后仿结果Fig 11 Test results and post-simulation results

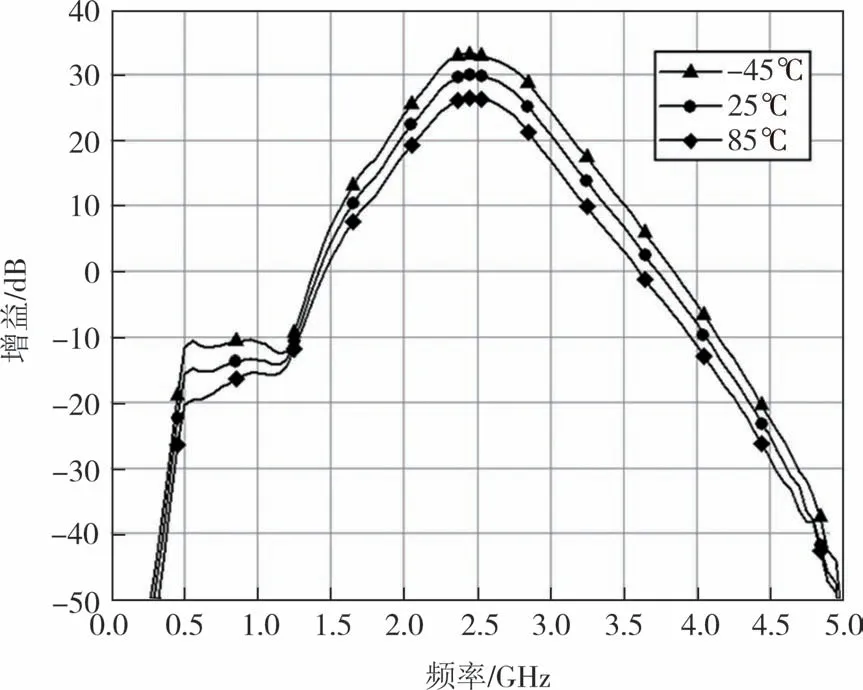

后仿结果显示放大器S21(正向传输增益)为32.5 dB,S11(输入反射系数)&S22(输出反射系数)<-10 dB.在25 ℃室温下测试得到的放大器增益约 30 dB,该增益通常需要三级级联才能实现,这说明所设计的cascode 驱动级能够提供较高的增益.测试结果与后仿结果相差约2.5 dB,出现此现象的原因是代工厂提供的晶体管建模并非完全准确,会和实际有一定的偏差,此外该芯片是通过测试板进行测试,测试板会引入非理想的寄生效应,导致放大器增益进一步下降.为验证功放在环境温度变化时的工作能力,利用温箱在-45~85 ℃对放大器进行测试,测试结果如图12所示.

图12 高低温下的测试结果Fig 12 Test results at high and low temperatures

测试结果显示-45 ℃时增益为32.9 dB,85 ℃时增益为26.5 dB,可以看出放大器热稳定性较好,未因结温过高而导致失效,说明设计采用的热稳定偏置电路和分布式镇流电阻起到了作用.

大信号测试采用NI pxie-5841 矢量信号收发器(美国生产),该仪器可以同时产生和分析矢量信号.在室温下,采用连续波信号对功放的增益压缩特性和效率进行测试,同时使用高精度红外线热分析仪观测放大器最高结温,结果如图13所示.

测试结果显示放大器1 dB 压缩点处P1dB为 24.3 dBm,PAE 可达33%.在饱和功率处的最高结温小于55 ℃.

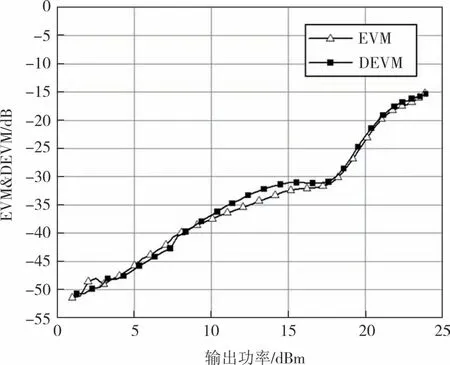

为测试放大器动态工作时的线性度,采用带宽为20 MHz 的64-QAM 正交频分复用(Orthogonal Frequency Division Multiplexing,OFDM)调制信号进行测试,控制信号的占空比为50%,周期为1 248 µs.测试结果如图14所示.

图14 DEVM与EVM测试结果Fig 14 DEVM and EVM test results

测试得到放大器在DEVM(动态误差矢量幅度)为-30 dB 时的输出功率为18.1 dBm.EVM(静态工作的矢量幅度误差)与动态工作的DEVM 的测试曲线几乎重合,这表明放大器具有较高的线性输出功率,并且动态工作并未导致其线性度有明显的退化.表1为本设计与其他全集成功率放大器的性能对比.

表1 提出的功率放大器性能比较Tab.1 Performance comparison of the proposed power amplifier

4 结论

本文采用SiGe BiCMOS 设计了一款全集成功率放大器,集成片上CMOS电源,采用cascode驱动级提高增益、减少芯片面积,运用了一种热稳定偏置电路和分布式镇流电阻以提高电路热稳定性.测试结果显示放大器增益可达30 dB,1 dB 压缩点处的输出功率为24.3 dBm,功率附加效率为33%,线性度满足无线传输要求.