基于ARM+FPGA 双核异构的SiP 设计

2024-03-04车岩

车 岩

(中国电子科技集团公司第四十七研究所,沈阳 110000)

1 引言

随着微电子技术高速发展,高集成度、小型化是未来电子产品的发展趋势。于是,新型的封装形式——系统级封装(System in Package,SiP)[1]得到了越来越多半导体厂商的青睐,得到了迅速发展。SiP 技术是集成电路向高性能、多功能、高密度化发展的有效技术途径,相较于后摩尔时代基于CMOS工艺的主流系统集成技术片上系统(System on Chip,SoC)而言,它朝着超越摩尔定律(more than Moore)的方向在发展。作为当前实现系统小型化的主流技术手段,SiP 是通过先进的封装技术,将不同工艺、不同架构、不同功能的裸芯集成到一个封装中,即异质异构集成,以此有效地解决SoC 所面临的研发成本高、设计周期长、验证和生产工艺复杂等问题,必将在未来技术发展中发挥极重要的角色。

2 双核异构SiP 设计原理

ARM+FPGA 双核异构SiP 的内部集成了1 个FPGA 裸芯、1 个基于ARM Cortex-M4[2]的MCU 裸芯、1 个flash 裸芯、1 个电平转换功能裸芯、4 个RS422 收发器裸芯,此外还包括若干阻容分立器件。其功能框图如图1 所示。

图1 ARM+FPGA 双核异构SiP 原理框图

所选裸芯片的主要技术指标如下:

1)MCU:选取集成了ARM Cortex-M4 内核的32位高性能MCU[3],主频168MHz;内部flash 容量1MB;SRAM 大小(192+4)kB;支持FSMC 接口;支持SWD&JTAG 调试接口;具有丰富的外设资源,包括GPIO、USART、ADC、DAC、RTC、USB、CAN(2.0B)、SPI、I2C、DMA、以太网MAC、SDIO、PWM 等。

2)FPGA:采用先进的55nm 低功耗工艺,逻辑规模为19600 查找表(LUTs),嵌入式存储器(ERAM)容量为1088kbit,内部DSP 数量为29 个,PLL 数量为4 个。

3)Flash:选用串行SPI 接口flash 存储器,属于非挥发存储器,可多次写入、读出,具备掉电保持存储数据信息的特性,存储容量为64Mbits。

4)电平转换器:支持数据高速传输,16 位数据通道分为两组,每组通道分别有独立的使能端以及方向控制端。信号通道两侧供电电源可独立设置。

5)RS422 收发器:选用一款3.0~5.5V 供电、全双工、低功耗产品,支持RS-485/ RS-422 协议,包括一个驱动器和一个接收器,两者均可独立传输信号。

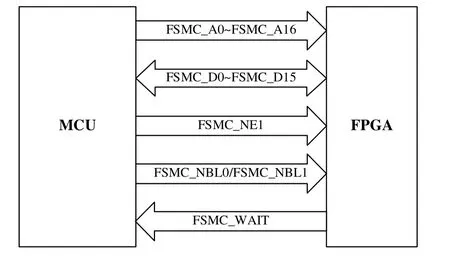

MCU 与FPGA 的连接是通过FSMC 的接口来实现的,具体连接关系如图2 所示。FSMC 接口信号只做内部互联,不做外部引出。

图2 MCU 与FPGA 连接示意图

MCU 与FPGA 的连接采用FSMC 接口的异步模式A 的时序,包括读时序和写时序,如图3 示。

图3 FSMC 接口异步模式A 时序

由于FPGA 是SRAM 型,需要外部flash 存放FPGA 的配置文件。系统上电后,从flash 中加载FPGA 的配置文件,用于配置FPGA。FPGA 与外部flash 的连接通过SPI 接口来实现,具体连接如图4所示。

图4 FPGA 与flash 连接示意图

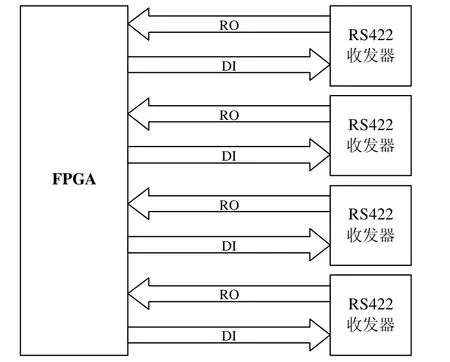

某型号RS422 收发器具有全双工、低功耗特点。FPGA 与4 个RS422 收发器连接是通过UART接口来实现,如图5 所示。

图5 FPGA 与RS422 收发器连接示意图

FPGA 与电平转换器的连接如图6 所示。通过共用总线SCK、MOSI、MISO 的信号,片选信号CS1~CS6 来实现6 路SPI 的接口功能。其中电平转换器的作用是实现3.3V 与5V 之间的电平转换。

3 基板设计及仿真

基板原理图设计软件选用Cadence 平台Orcad组件[4],主要设计思想如下:

MCU 按照144 引脚的封装引出;FPGA 裸芯3.3V电源、1.2V电源、BANK 电源、地、I/O 信号的PAD 均引出;3.3V 电源、1.2V 电源、地在基板上分别进行互联;每组BANK 电源至少引出1 组;I/O 信号除内部互联外,均引出到Ballmap 上;所有裸芯3.3 V 数字电源互联;数字地互联。

基板版图设计选用的软件为Cadence 平台SiP组件。主要设计规则可归如下:

外观尺寸17mm×17mm,封装形式为BGA400[5],pitch 为0.8mm;Finger 尺寸为70μm×150μm,最小pitch 为120 μm;裸芯到裸芯最小距离为500 μm;Finger 距离裸芯最小距离为300μm;键合丝选取直径20 μm 金丝,最大长度为3600 μm;Finger(边缘)到基板外框最小距离为150μm;走线(边缘)到基板外框最小距离为100 μm;基板版图最小线宽为35μm;镭射孔[6]的孔径、孔盘之比为80μm/180μm。

按照上述规则与设计,完成裸芯布局。考虑到铜布线的厚度及印制板厂工艺水平等因素,信号走线宽度选为35μm,间距为50μm。信号互联主要在TOP 层完成,第二层为地层,第三层为电源层,Bottom层为SiP 对外引出信号连接到BGA 球的布线。

在设计中还应该注意到,由于BT 基板厚度很薄,很容易出现翘曲的问题。可通过采取一定的技巧,有效缓解BT 基板翘曲的问题。

BT 基板上具有覆铜区域,通过控制BT 基板对称层的残铜比小于15%,可以有效避免基板翘曲问题。具体而言,BT 基板的顶层与底层为对称层;第二层与第三层为对称层。残铜比则是指对称层中两层铜重量百分含量的差值。

另外,通过在BT 基板上的覆铜区域设置排气孔,基板上设置绿油层,并在金手指区域开设大于等于50μm 的窗口来提高塑封料的结合度,也可以有效避免基板翘曲问题。

4 工艺与测试系统设计

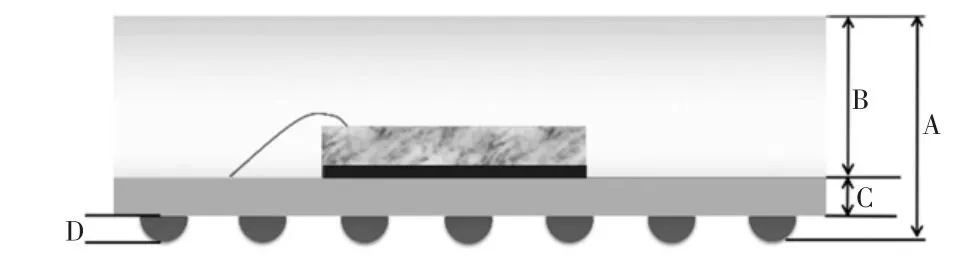

封装形式采用塑封BGA400,20μm 金丝引线键合[7],如图7 所示,尺寸参数的取值如表1 所示。

图7 引线键合图

基板采用4 层BT 基板,它是一种使用BT 树脂(Bismaleimide 和Triazine 两种成份)为材质的PCB,具体材质结构及各层厚度如表2 所示。

表2 BT 基板叠层构成

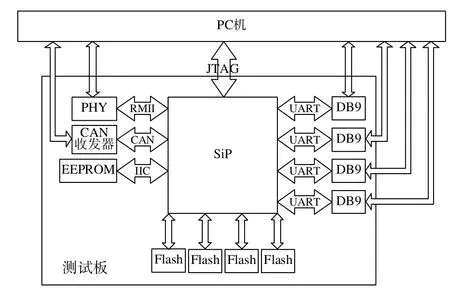

测试系统从结构上包括测试板和PC 机两个部分,结构示意图如图8 所示。测试板的功能是为被测SiP 模块提供电源、晶振、接口电路等[8]。PC 机用来调试、下载SiP,通过RS422 转USB/CAN 调试器等对通信接口进行测试。PC 机通过串口或网口与测试板通信,并显示、保存测试结果。

图8 测试系统结构框图

5 结束语

所探讨的基于ARM+FPGA 的双核异构SiP,立足于系统级封装技术,与传统的PCB 设计相比,在实现相同功能的条件下,占用的空间仅是传统模组的10%;与SoC 相比,研发时间仅是SoC 的10%,研发成本为SoC 的5%左右。此外该SiP 功能齐全、性能稳定,相对于传统的单板系统,具有可定制、体积小、功耗低、重量轻等优点,可为嵌入式系统的未来发展提供一种全新的解决途径。