130 nm 7T SOI SRAM总剂量与单粒子协和效应研究

2024-02-20肖舒颜王林飞陈启明高林春王春林张付强赵树勇刘建成

肖舒颜,郭 刚,*,王林飞,张 峥,陈启明,高林春,王春林,张付强,赵树勇,刘建成

(1.中国原子能科学研究院 核物理研究所,北京 102413;2.中国科学院 微电子研究所,北京 100029)

空间环境中充满着大量的高能带电粒子,其可直接影响电子器件的运行,进而造成运行异常、输出错误、功能中断、数据崩溃、电脑系统崩溃,甚至部件永久失效等严重后果[1]。相关的研究表明带电粒子辐射引起的单粒子效应(SEE)和总剂量效应(TID)是导致航天器运行故障的主要原因。因此,对星载电子器件开展TID和SEE机理研究是现代航天器设计中的主要工作之一[2]。先前的相关研究表明电子器件的TID和SEE之间存在着明显的协和效应。国内外从20世纪80年代开始就陆续开展了对电子器件TID与SEE之间协和效应的研究。随着电子器件工艺尺寸及抗辐射性能评估技术的发展,SRAM器件中TID与单粒子翻转(SEU)协和效应的研究已经从最早的微米器件逐渐拓展到了亚微米器件和纳米器件[3-14]。早期对特征尺寸为微米量级SRAM的研究表明,TID辐照会引发器件阈值电压的漂移,进而会对SEU敏感性有很大影响,最严重时器件的SEU截面在300 krad(Si)剂量辐照后增加了3个数量级[3-6]。对亚微米级SRAM协和效应的研究结果显示,亚微米级SRAM的协和效应小于微米级SRAM,TID辐照后的器件SEU截面最大可以增加1个数量级,且在其中发现了协和效应的数据依赖性,即“印记效应”[7-9]。随着研究器件特征尺寸的进一步减小,器件的TID影响机制发生了改变,从而导致了TID对SEE的影响也发生了改变。针对纳米器件的研究表明,TID辐照对小尺寸工艺器件SEU截面的影响已几乎不可察觉[10-11],TID辐照只能引起130 nm SRAM[12]和90 nm SRAM型FPGA BlockRAM[13]模块SEU截面的小幅度增加,这些器件的协和效应远不如微米级和亚微米级器件显著,TID对于小尺寸MOS管的影响主要是在STI结构中形成漏电流,由NMOS漏电和其寄生电阻共同作用使存储单元低电平上拉会引起“印记效应”,而PMOS漏电流增长充电使存储单元高电平下降时间延长会引起“反印记效应”[14]。

由于SRAM中TID和SEE协和效应受器件结构和制备工艺的影响较大,因此,目前业界还没有就相关机理达成共识。Zheng等[15]研究了特征尺寸为130 nm采用PD SOI工艺的6T结构SRAM中TID与SEU间的协和效应,结果显示,TID辐照后器件的SEU截面有所增加,且器件SEU截面与TID辐照期间写入的数据图形间没有明显的依赖关系,TID辐照造成的晶体管阈值漂移会使存储单元的静态噪声容限减小,最终使器件SEU截面增加。除此之外,有关SOI SRAM中的TID和SEE协和效应的研究报道相对较少,其相关物理机制也尚未完全明了。本文针对国产130 nm 7T SOI SRAM开展TID与SEE协和效应研究,通过实验规律结合理论分析阐明效应机理,为未来抗辐射加固工作提供参考。

1 器件、测试方法与实验装置

1.1 器件

本研究采用一款特殊设计的国产130 nm SOI SRAM器件,容量为64 Kbit,其存储单元为7T结构,工作时由电压为3.3 V 和1.5 V的两个电源供电,分别用于输入输出电路和存储单元阵列。如图1所示,存储单元由4个NMOS晶体管(N1、N2、N3、N4)、两个PMOS(P1、P2)晶体管和1个延迟晶体管(N5)组成,存储单元的特征尺寸为3.9 μm×3.4 μm。当存储单元读取和写入数据时,N5的电阻变得非常低,晶体管被打开。当数据写入后进入保持状态,N5关闭,其电阻将变得非常高,这样可以有效地抑制单粒子瞬态对存储单元的干扰,从而提高SOI SRAM的抗辐射性能。

图1 7T SRAM存储单元结构示意图

图2a为SOI SRAM存储单元中NMOS晶体管和PMOS晶体管的结构,它们是体下源场效应晶体管(BUSFET),消除了由埋氧层形成漏电通道的物理条件,因此,漏电通道主要形成区域为浅槽隔离氧化区(STI),这部分结构在捕获陷阱电荷后会在源极和漏极之间开启微弱的漏电通道。图2b为延迟晶体管N5的结构,它可以被认为是由1个电阻和1个晶体管并联的组合。

图2 存储单元中BUSFET结构和延迟晶体管N5结构示意图

1.2 测试方法

为验证该款器件的协和效应是否存在数据依赖性,特别针对其开发了测试系统,测试系统通用于TID实验和SEE实验,可在TID实验时对待测器件进行偏置并写入特定数据,以便于在辐照后的SEE实验中对协和效应的数据依赖性进行验证。测试系统结构如图3所示。

图3 测试系统结构

为防止控制电路受到辐射影响,系统主要分为主板和子板两部分,在子板中仅保留待测芯片和必要的通信接口,将主要的控制电路置于主板之上,主板和子板间通过30 m的长线连接,保证了在器件辐照过程中控制系统可以始终处于辐射场外区域。

1.3 实验装置

1) TID实验

TID实验在中国原子能科学研究院总剂量实验平台上开展。实验使用剂量率为25 rad(Si)/s,共采用8个器件,分为4组,每组2个器件,辐照前对每组器件的其中1个写入数据图形“55”并在辐照过程中保持存储状态,另1个仅施加偏置电压。4组器件分别辐照到0、300、500和750 krad(Si),辐照前后对所有器件均进行电参数测量。为防止TID和SEE实验之间的长时间等待和准备造成器件退火,对TID实验后的器件使用干冰保存,直到SEE实验前半小时取出放置到室温再进行下一步实验。

2) SEE实验

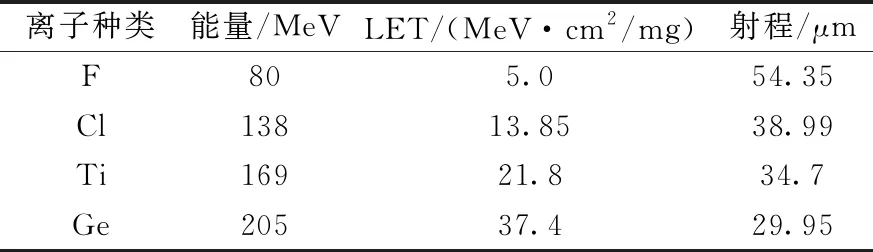

SOI SRAM的SEE实验在TID辐照后24 h内进行,并在中国原子能科学研究院HI-13串列加速器重离子SEE实验终端上开展。实验所用离子种类、能量、LET和在硅中射程列于表1,其中重离子射程和LET由SRIM程序计算得到。实验过程中对器件进行了LET由高到低的辐照,并在辐照过程中同步测量器件的SEU情况,每次辐照前预先写入数据图形“55”或“AA”,单次辐照的停止条件为累计100个翻转或达到1×107cm-2辐照注量,单次辐照完成后记录辐照注量和相应的翻转次数用于计算SEU截面和后续分析。

表1 离子种类、能量、LET和在硅中射程

2 实验结果

2.1 TID实验对器件电参数的影响

在TID实验中,3组器件被分别辐照到300、500和750 krad(Si)的累积剂量,1组器件未进行辐照。辐照后的器件电参数测量结果显示,器件的读写功能正常,未出现存储错误,测试过程中SOI SRAM器件的静态功耗电流(IDD)随剂量的累积不断增加,且在电参数测试中写入不同数据模式的情况下出现了明显的差异。图4为在电参数测试阶段分别写入全0和全1两种数据模式下IDD与累积剂量的关系。两种模式在0 krad的初始情况下IDD均为0.002 4 mA,经过750 krad剂量辐照后,全0模式下的IDD涨至1.26 mA,全1模式下的IDD涨至3.17 mA,全1模式下的电流涨幅明显大于全0模式。

图4 不同写入模式下IDD与累积剂量的关系

2.2 TID对SEU截面的影响

通过重离子SEE实验,得到TID辐照后的SEU截面情况。在TID辐照中和SEE实验中写入相同数据模式的器件,其SEU截面相对于写入不同数据模式器件的SEU截面并没有明显的上升,因此该款器件不存在明显的“印记效应”。SOI SRAM的SEU截面在TID辐照后出现了明显的变化,且随着累积剂量的不同而改变。

表2列出不同TID辐照后的翻转截面。由表2可知,当入射粒子LET为5.0 MeV·cm2/mg时,TID辐照后的SEU截面相对辐照前有所提高,最高提高了2.2倍(500 krad(Si)剂量辐照后);当入射粒子LET为13.85 MeV·cm2/mg时,TID辐照后的SEU截面相对辐照前有所降低,最低降为辐照前的19.5%(500 krad(Si)剂量辐照后);当入射粒子LET为21.8 MeV·cm2/mg时,TID辐照后的SEU截面相对辐照前也有所降低,最低降为辐照前的34%(300 krad(Si)剂量辐照后);当入射粒子LET为37.4 MeV·cm2/mg时,TID辐照后的SEU截面相对辐照前同样降低,最低降为辐照前的49.5%(750 krad(Si)剂量辐照后)。综上所述,该款器件的SEU截面在TID辐照后呈现下降的趋势,这与文献[16]报道的同种工艺6T SOI SRAM器件的研究结果完全相反。

表2 不同剂量辐照后的SEU截面

2.3 LET对SEU截面的影响

通过对不同TID辐照后的SEU截面进行Weibull拟合和外推,得到完整的SEU截面曲线(图5),图5中包含拟合得到的饱和截面。器件在0、300、500和750 krad(Si)剂量辐照后的饱和截面分别为2.15×10-10、2.09×10-10、1.79×10-10、1.73×10-10cm2/bit,饱和截面在750 krad(Si)剂量辐照后最多下降了19.5%。假定饱和截面的10%处为SEU翻转阈值所在点位,通过辅助线分析得到0、300、500、750 krad(Si)剂量辐照后的SEU阈值分别为5.13、5.18、5.17、5.17 MeV·cm2/mg,未出现明显的变化。这一现象与文献[8]的研究结果高度吻合,TID对SEU的影响主要是在饱和截面,而对翻转阈值影响较小。

图5 不同剂量辐照后的SRAM SEU截面拟合曲线

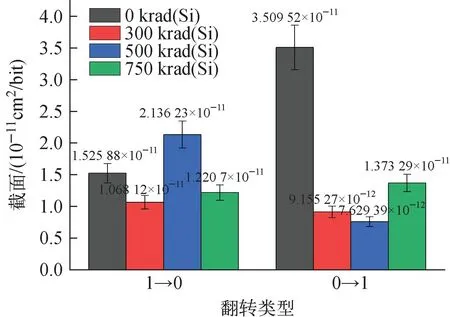

2.4 翻转类型对SEU截面的影响

重离子LET为13.85 MeV·cm2/mg时,写入数据为“AA”情况下不同剂量辐照后的SEU中“1→0”和“0→1”翻转的截面如图6所示。可看出,未进行TID辐照时,器件SEU中“0→1”翻转截面要远高于“1→0”翻转截面;在TID辐照后“1→0”翻转截面有升有降,总体在±30%左右波动,而“0→1”翻转截面则整体呈现下降趋势,最大下降了78.3%。因此,“0→1”翻转截面的降低是造成该款SRAM器件SEU截面降低的主要原因。

图6 “1→0”和“0→1”翻转的截面

3 讨论

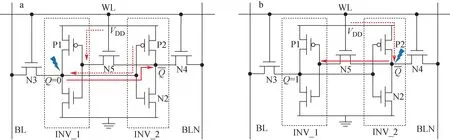

3.1 瞬态脉冲传播电路分析

由于电子在硅中的迁移率比空穴大得多,电子在电场的驱动下会迅速地被漏极收集,所以SOI SRAM的SEU截面是由处于关断状态的下拉NMOS晶体管决定的。图7为存储单元中“1→0”和“0→1”翻转时单个瞬态脉冲传播的等效电路。

图7 SOI SRAM“1→0”(a)和“0→1”(b)翻转时瞬态脉冲传播的等效电路

3.2 TID对N5延迟晶体管的影响

在以往的研究[16]中表明,载流子迁移率在TID照射下会发生改变。晶体管中的载流子迁移率可由经验式(1)[17]计算:

(1)

其中:αit和αot为模型参数,表征氧化层内固定电荷(ΔNot)和界面态电荷(ΔNit)对迁移率退化的贡献;μ0为辐照前的迁移率。

载流子迁移率的变化会改变N5的电阻率ρ,载流子迁移率和电阻率的关系可表示为:

(2)

其中:q为电荷;n0和p0为导带电子浓度和价带空穴浓度;μn和μp为电子和空穴的载流子迁移率。

由式(1)得到,随着TID的照射,载流子迁移率逐步下降,而式(2)中μn和μp的下降会导致电阻率的提升,延迟晶体管N5的等效关态电阻会增加,从而提升其延迟作用,最终导致SOI SRAM的SEU截面下降。

3.3 协和效应对抗辐射加固的启示

航天器所搭载的电子器件在空间中受到辐射环境的影响会产生TID和SEE效应,以往的研究中通常认为TID会使SEE进一步劣化。通过本文的研究发现,在特殊的器件结构下,如本文中利用延迟晶体管N5作为加固的方案,TID的形成可能会降低SEE对器件的影响。TID在空间中主要由质子或电子沉积能量所引发,并随着在轨时间的增加而不断累积,所以具有类似设计的SOI SRAM在辐射环境中的抗SEE能力会随着任务的进行不断变好,这为今后的宇航电子器件抗辐射加固提供了启示。

4 结论

本文通过实验得到130 nm 7T SOI SRAM SEU截面随TID的变化规律,采用Weibull拟合和外推得到器件的饱和截面和翻转阈值,给出该款SOI SRAM的协和效应机理机制,N5晶体管因为TID辐照造成了载流子迁移率下降,使其等效关态电阻增加,提升了其延迟作用,导致翻转截面大幅下降,这一现象证明了这种特殊结构SOI SRAM中TID对器件抗SEE性能的促进作用,对今后的电子器件抗辐射加固提供了启示。