基于Zynq 的医用内窥镜视频流采集与处理系统设计与研究∗

2024-01-29王云峰范正吉景金荣洪应平

王云峰,何 鑫,范正吉,景金荣,洪应平

(中北大学仪器科学与动态测试教育部重点实验室,山西 太原 030051)

在医疗领域,内窥镜是用来观察人的内部体腔的,通过它能直接观察内脏器官的组织形态,提高了诊断的准确性,成为医疗诊断的可靠工具。结合医用内窥镜施行的内外科诊疗技术的诸多优点,已成为医学界的共识。现代科技的进步推动着医用内窥镜的技术产品迅速发展[1]。随着科技的不断进步,CMOS 摄像头的尺寸也在不断缩小,内窥镜在医疗领域的用途也越来越广泛。同时对成像质量的要求也越来越高。受限于半导工艺,内窥镜CMOS 输出的图像信号往往会带有噪声、色差等,故需要设计相应的处理算法。由于医用内窥镜的特殊用途,算法处理必须保证实时性。

目前的内窥镜视频流采集处理方案有很多种,包括ARM、FPGA、DSP、专用SOC 等,其中,ARM 体积小,功耗低。但是设计相对不够灵活,且代码运行方式为串行工作,在运行复杂算法时占用资源高,效率不足;FPGA 方案的优点是灵活性强,且FPGA 的并行处理机制决定着其在算法很复杂的情况下依然能实现很低的延时。但是FPGA 设计难度大,用“数字电路”的思想去描述算法周期长,且不利于维护和修改;DSP 是一种独特的微处理器,有自己完整的指令系统。DSP 方案的优点是设计灵活,易于拓展,计算能力强,是数字信号处理的优先选择。缺点是成本高,设计难度大,占用面积和功耗也有待改进。专用SOC 方案如海思、大华等厂商设计的专门用于图像处理的芯片,优点是体积小、集成度高、功耗低,内部集成各种图像处理算法的IP 可以直接调用。缺点是不够灵活,复杂的图像处理算法只能调用厂商提供的固定的算法;比较好的解决方案就是用上述方案的组合,取长补短。考虑性能、体积、功耗等因素,Zynq 是个很好的选择。

Zynq 是Xilinx 公司推出的一款全可编程片上系统处理器,集成了PS(ARM 处理器) 和PL(FPGA),是一种单片ARM +FPGA 的架构。其中PS 处理器部分包含了完整的ARM 处理子系统,而PL 逻辑部分中的资源会随着芯片级别的不同而不同。这两个部分相互联系又可以独立使用[2]。

针对上述情况,本文设计了一种基于Zynq 的医用内窥镜视频流采集与处理系统,内窥镜摄像头的型号为OV6946。Zynq 包含了FPGA(PL)与ARM(PS)的优势,使设计的系统更加灵活,减少了开发的时间。本系统的目的是采集经OV426 对OV6946进行模数转换后的数字信号,然后通过Zynq 的PS和PL 端进行协同处理。最后用过HDMI 进行实时图像输出。并在视频流的帧间隔时间内,完成双边滤波、白平衡、暗部增强、CCM 等算法处理,以实现实时性要求。结果表明,在HDMI 显示器上实现了经算法实时处理的OV6946 的图像,保证低功耗和小体积的同时也完成了高性能、实时的视频流处理,并可在PS 端快速修改PL 端的许多算法参数,避免了PL 端设计和编译时长,具有高效性和灵活性。

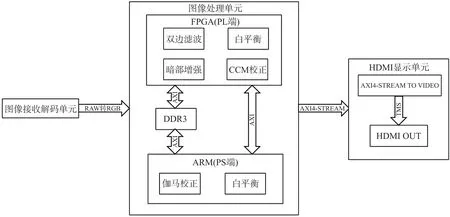

1 系统总体设计

为了实现视频流实时性的算法处理,本设计的算法大部分通过Vivado HLS 编写生成IP,运行在FPGA端,以实现并行处理,涉及到浮点运算的部分在ARM端处理,以节省FPGA 端资源并发挥ARM 在浮点运算上的优势。同时采集端也用ARM 结合FPGA 的方式,由ARM 端通过SCCB 总线对内窥镜的运行参数进行配置,由FPGA 端进行DVP 数字图像信号的采集。输出端采用FPGA 模拟HDMI 的方式进行输出,省去了HDMI 芯片,以减小系统的复杂性。

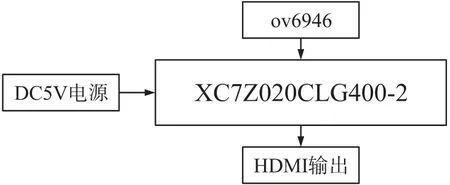

整体系统设计框图如图1 所示。分为图像解码模块、图像处理模块与图像显示模块三个模块。

图1 整体设计框

图像解码模块负责对OV426 输出的数字信号图像进行解码与像素格式转换。首先由PS 端通过SCCB 总线配置OV426 的工作模式,由PL 端接收OV426 的图像数字信号,进行RAW10 转RGB888 处理并缓存进DDR 中,由于OV6946 每个像素处的图像传感器在每个像素位置上仅感测一种颜色,并且缺少另外两种颜色。对于完整的彩色RGB 图像,我们在每个像素位置需要三种颜色[3]。故需做RAW10 转RGB888 处理,此处采用双线性插值法。

图像处理模块由PS 与PL 协同处理,具体做法为PL 端在接收数据缓存到DDR3 的同时,对像素进行行累加、列累加、像素统计等数据预备工作,并通过AXI4 总线传给PS 端,为后续算法使用做准备。白平衡使用灰度世界算法。灰度世界算法是以灰度世界假设为基础的,该假设认为对于一幅有着大量色彩变化的图像,R、G、B 三个分量的平均值趋于同一个灰度值[4]。上述在PL 准备的数据即可用于灰度世界算法,对于灰度世界算法,本系统在PL端进行所需的加减运算,在PS 端做所需的乘除运算来计算增益。补充了FPGA 对于浮点运算能力的不足,也省去了在PL 端用乘法器和除法器延时需进行时序对齐的麻烦,提高率开发效率。同时,伽马调节算法也是在PS 端实现,伽马校正是为了克服人眼视觉系统对于亮度变化的感觉是非线性的而引入的一种传输函数,在视频流、计算机图形学以及其他成像系统中应用广泛[5]。伽马校正是对输入图像灰度值进行的非线性操作,使输出图像灰度值与输入图像灰度值呈指数关系。此部分在PS 端用数组存储校正值,在PS 端从DDR 中搬运数据的同时,以查找表的方式直接进行伽马校正。经上述算法处理后再次缓存并由VDMA 读出并转换为AXI4-STREAM。去噪与暗部增强使用Vivado HLS 进行加速设计,硬件加速设计将软件代码转换为RTL 电路,输入输出接口均为AXI4-STREAM。其中不可综合的函数或者语句需用Vivado HLS 支持的函数替换[6]。

图像显示模块为HDMI 显示,HDMI 接口是目前应用最广泛的高清音视频接口之一,存在多种可供选择的传输方式[7]。HDMI 接口协议物理层使用TMDS 标准传输音视频数据。最小化传输差分信号(Transition Minimized Differential Signaling,TMDS)是美国Silicon Image 公司开发的一项高速数据传输技术,在DVI 和HDMI 视频接口中使用差分信号传输高速串行数据。本设计中直接在PL 端模拟HDMI协议,输出稳定且节省硬件资源与成本。

2 系统硬件设计

本设计选用Xilinx XC7Z020CLG400-2 入门级Zynq 作为主控芯片,设计了一套集图像解码、实时视频流算法处理和输出显示的硬件。利用OV426桥接芯片对OV6946 进行模数转换,然后由Zynq 进行采集、解码与处理,最后由HDMI 输出。

2.1 内窥镜图像解码硬件模块设计

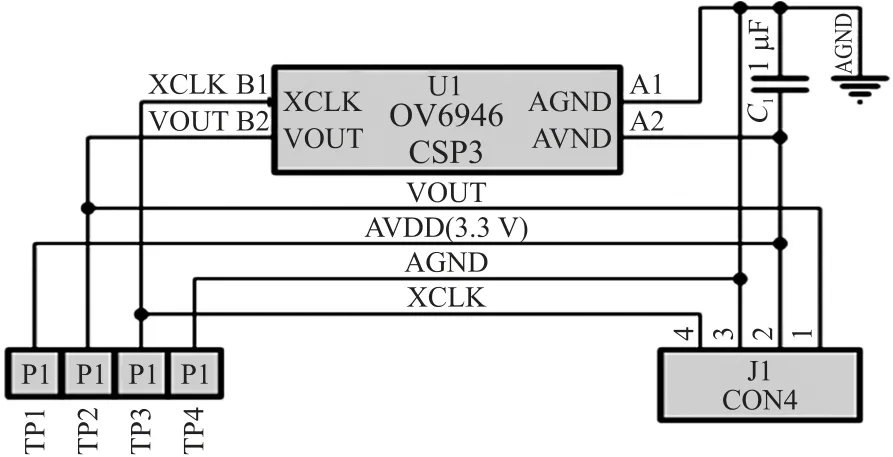

2.1.1 OV6946 摄像头

CMOS 是内窥镜摄像头的核心器件,微型COMS已经在医疗图像领域得到了广泛的应用,如胃镜、肠镜、肾盂镜等等。OV6946 彩色图像传感器是一种低电压、高性能、1/18 英寸的CMOS 图像传感器,分辨率为400×400 pixel,它通过串行外围设备接口(SPI)的控制提供RAW 格式的全帧模拟图像。OV6946 的图像阵列能够以30 帧/s(FPS)的速度运行,并简化了曝光控制。可通过SPI 接口进行编程。其硬件原理表示如图2 所示。

图2 OV6946 原理示意图

2.1.2 摄像头模数转换单元设计

为了实现对OV6946 的CMOS 输出模拟信号进行转换,本设计使用了OV426 桥接芯片。OV426 是一款专为OV6946、OV6948、OCHTA10 等摄像头设计的一款桥接芯片。可将这些摄像头输出的模拟信号通过内部集成的ADC 和协处理单元转换为DVP协议的数字信号。OV426 通过SCCB 总线进行寄存器配置,可以配置输出数据的格式、ISP 功能等。支持BLC、AEC/AGC 和MWB 等功能。其硬件原理表示如图3 所示。

图3 OV426 电路设计

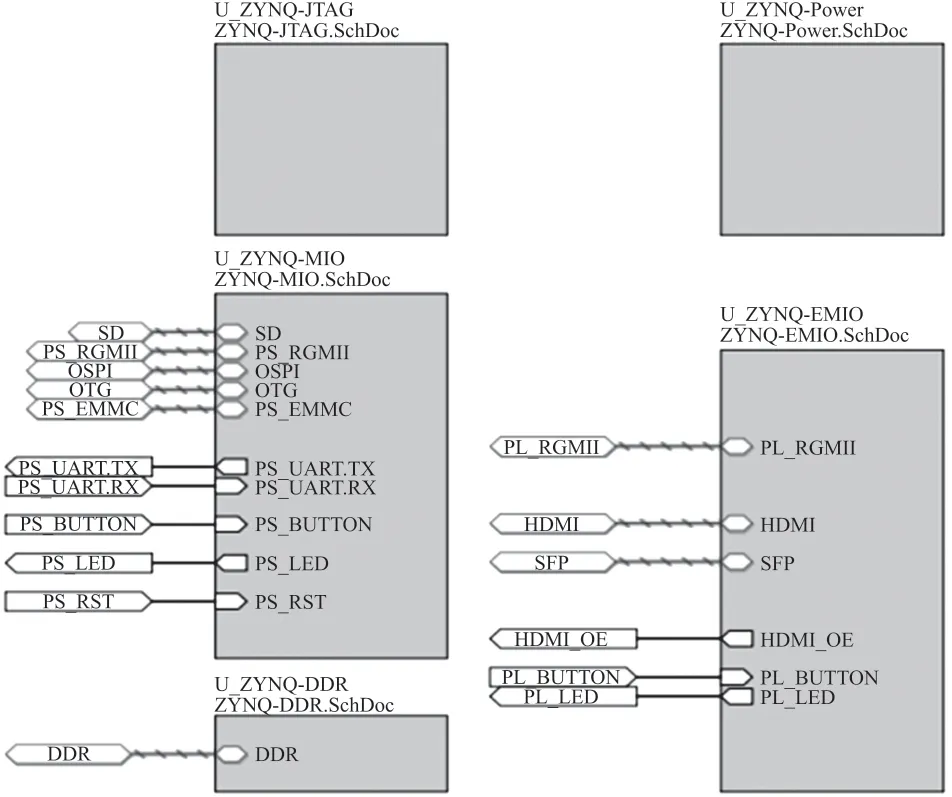

2.2 主控单元及电源硬件模块设计

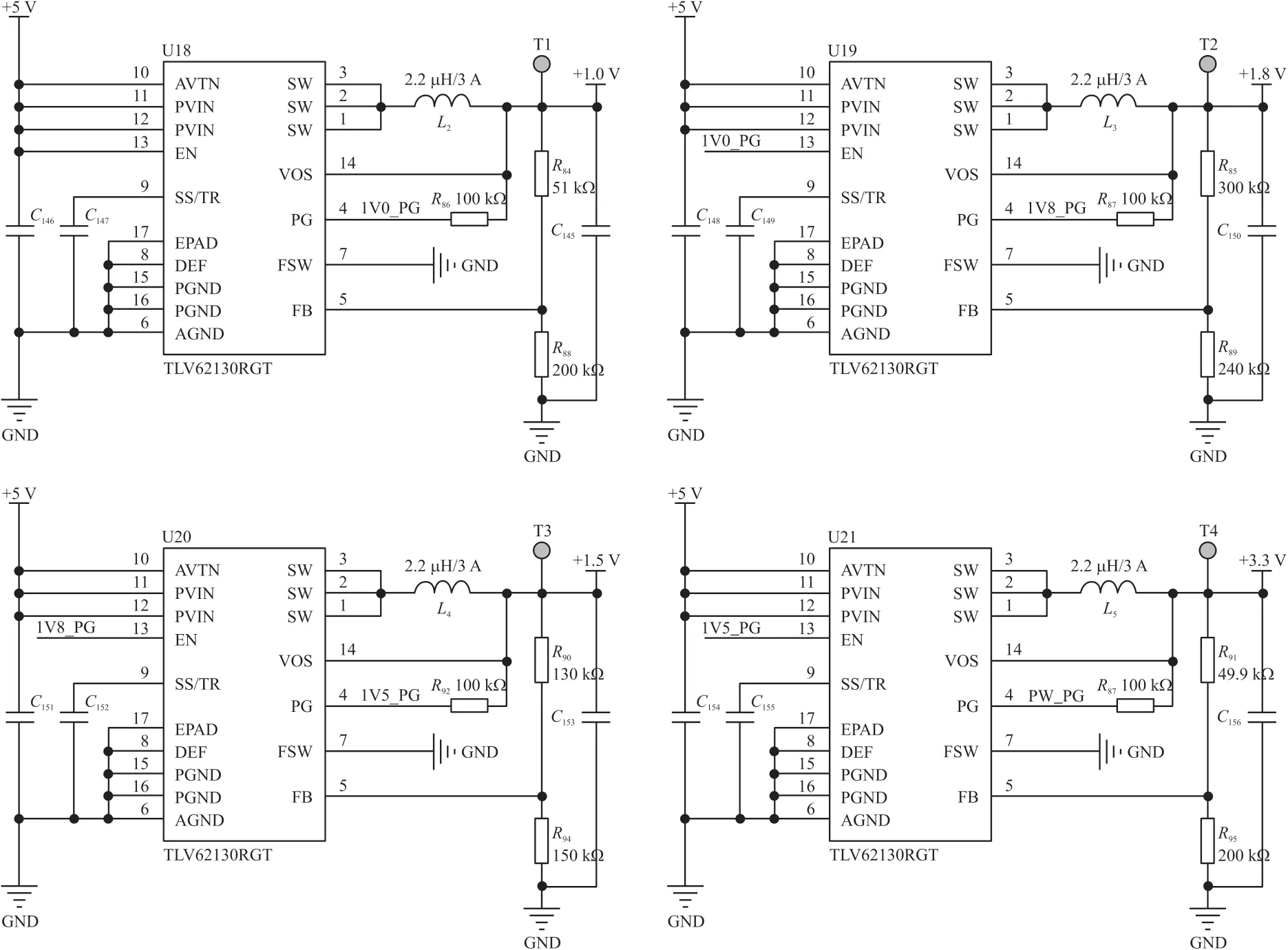

主控选用Xilinx XC7Z020CLG400-2 入门级Zynq 芯片ZYNQ-7020。PL 逻辑单元为85K,BRAM存储资源为4.9 Mbit。芯片的速度等级为“-2”。本设计中DDR3 采用美光MT41J128M16HA-187E,容量为2 Gbit。QSPI FLASH 选用W25Q256FVEI,主要用于程序的固化。电源部分统一采用TLV62130RGT,可通过反馈电阻设置其输出电压,输入电压范围为3 V~17 V,输出电压范围为0.9 V~5.5 V,输出电流最大为3 A,完全满足电源设计需求。主控单元顶层原理图及电源部分原理图表示如图4和图5 所示。

图4 主控单元顶层原理图

图5 电源部分电路设计

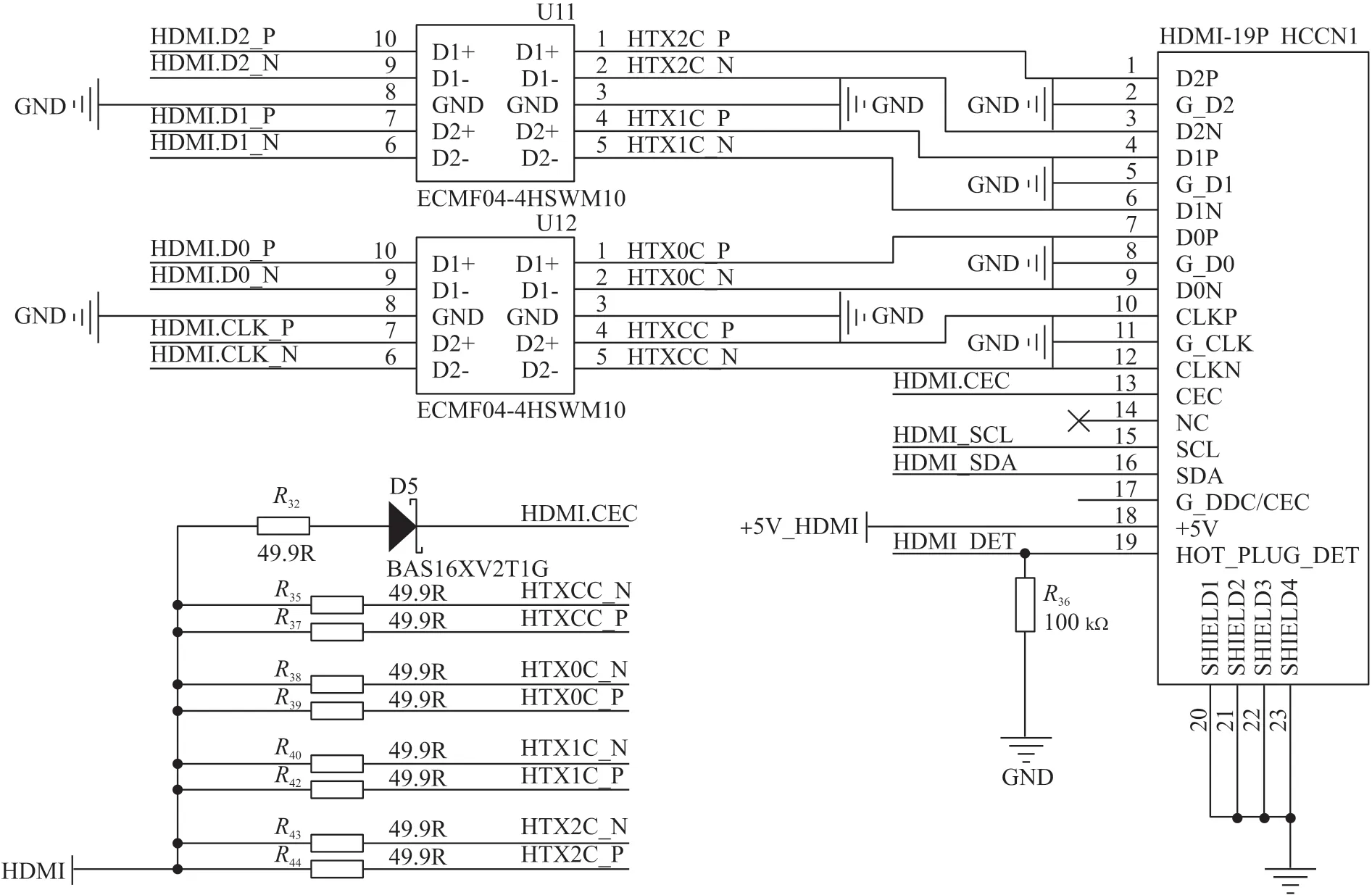

2.3 HDMI 显示硬件模块设计

高清晰度多媒体接口(High Definition Multimedia Interface,HDMI)是一种数字化音频/视频接口技术,通过FPGA 可以很快地实现驱动[8]。HDMI 1.0 版本于2002 年发布,最高数据传输速度为5 Gbype/s。而2017 年发布的HDMI 2.1 标准的理论带宽可达48 Gbype/s。HDMI 接口协议在物理层使用TMDS 标准传输音视频数据。TMDS 差分传输技术使用两个引脚来传输一路信号,利用这两个引脚间的电压差的正负极性和大小来决定传输数据的值(0 或1)。Xilinx 在Spartan-3A 系列之后的器件中,加入了对TMDS 接口标准的支持,用于在FPGA 内部实现DVI 和HDMI 接口。具体的模块电路设计如图6 所示。

图6 HDMI 接口硬件电路设计

3 系统软件设计

3.1 OV6946 视频采集软件设计

OV6946 在经OV426 转换后输出的为DVP 协议数字图像。DVP(Digital Video Port)摄像头数据并口传输协议,提供8 bit 或10 bit 并行传输数据线、HSYNC(Horizontal sync)行同步线、VSYNC(Vertical sync)帧同步线和PCLK(Pixel Clock)时钟同步线。OV426 提供10 bit的并口传输,PCLK 为8 MHz,其中HSYNC 高电平期间包含400 个PCLK,每个PCLK 取一次值,对应一行的400 个像素点。每两个VSYNC 的高电平间有400 个HSYNC,对应一帧图像的400 列。按上述方法编写Verilog 代码,并通过AXI4 总线直接存于DDR 中。AXI4 包含3种类型的接口:AXI4 接口、AXI4-Lite 接口以及AXI4-Stream 接口。AXI4 接口主要面向高性能地址映射通信的需要,功能完整,在单地址传输的情况下最大允许256 轮的数据突发长度[9]。

本设计中在PL 端设置好每一帧缓存的帧起始地址,经过FIFO 缓存打包后读出,通过AXI4 总线完成一帧的写入。基于此完成400 pixel×400 pixel 分辨率的数字图像解码。AXI4 总线仿真时序如图7 所示。

图7 AXI4 总线仿真时序

3.2 视频流处理软件设计

本设计的主要算法是通过Vivado HLS 开发完成。Vivado HLS 是最具创新性的可编程逻辑设计工具之一。使用Vivado HLS 生成IP 核可以大大缩短FPGA 的开发周期。只需要使用高级语言,如C、C++或System C 来描述逻辑,然后将逻辑转换为RTL 级别的实现。利用Vivado HLS 可以缩短1/3的RTL 仿真时间,使算法验证速度提高10 倍以上[10]。Vivado HLS 编写完的代码在综合通过后会生成一个IP 核,可通过代码配置其输入输出接口。

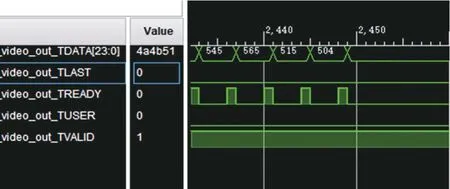

在本设计中,对于视频流的处理,输入输出接口均为AXI4-STREAM 接口。AXI4-STREAM 总线是单向的,从主节点到从节点,并根据握手信号传输数据。优点是它不需要地址,支持数据突发传输,数据量不受限制[11]。因此,AXI4-STREAM 适用于图像像素数据、音频采样数据、离散数字信号处理等数字信息的间接传输系统[12]。它的握手机制为只有当VALID 和READY 同时为高时,才能进行传输。当TREADY 信号一直处于高电平时,表示从设备已经做好了接收数据准备。TVALID 变为高电平的同时,TDATA 进行发送。数据发送完成后,TVALID 变为低电平。其仿真时序如图8、图9 所示。其中图8为一包数据传输开始。图9 为一包数据传输结束。

图8 传输开始

图9 传输结束

算法的总体设计流程如图10 所示。其中,白平衡为PS 端与PL 端协同完成,算法的累加步骤由PL 完成。在一帧图像采集完之后的一个时钟周期内即可完成数据的准备。乘除运算在PS 端完成。因为PS 端具有较强的浮点运算能力。伽马校正由PS 采用查找表的方式完成,其余算法均由PL 端完成,并由AXI4-Lite 总线在PS 端配置参数。

图10 系统算法流程图

图10 中最后一个步骤的作用为适配HDMI 与显示器的分辨率。由于摄像头的分辨率为400×400 pixel,标准显示器不支持该分辨率。故在其周围进行像素填充,使其输出640×480 pixel 分辨率的视频流,摄像头图像显示居中。经整合的上述所有算法在100 MHz 的时钟频率下延时约为3 ms。其Vivado HLS 综合结果如图15 所示。

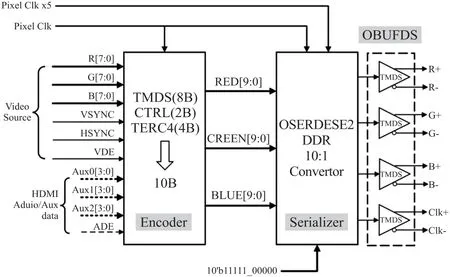

3.3 HDMI 显示软件设计

HDMI 的实现方法主要有两种,一种是使用硬件HDMI 芯片,另一种是使用IO 模拟。因为HDMI协议本身就是数字协议,所以本设计采用第二种方法,既节约硬件成本,又节省板面空间资源。

一个HDMI 连接包括三个TMDS 数据通道,一个TMDS 时钟通道。TMDS 时钟通道因分辨率不同而以特定速率运行。在每个TMDS 时钟通道周期中,三个TMDS 数据通道每个都发送10 bit 数据。这个10 位的字被编码,采用某种不同的编码技术。输入到信源端的输入流,包含视频像素,数据包,和控制数据。数据包包括音频数据和辅助以及相关的纠错码。

整个系统需要两个输入时钟,一个是视频的像素时钟,另外一个所需时钟的频率是像素时钟的五倍。并串转换过程的实现的是10 ∶1 的转换率,理论上转换器需要一个10 倍像素时钟频率的串行时钟。这里用了一个5 倍的时钟频率,因为OSERDESE2模块可以实现DDR 的功能,即它在五倍时钟频率的基础上又实现了双倍数据速率。其模块框图如图11 所示。

图11 RGB TO DVI 模块框图

其在本设计中的Block Design 如图12 所示,其中的pclk x5 由axi_dynclk_1 实现五倍频。

图12 HDMI 部分Block Design 图

4 系统实物及测试分析

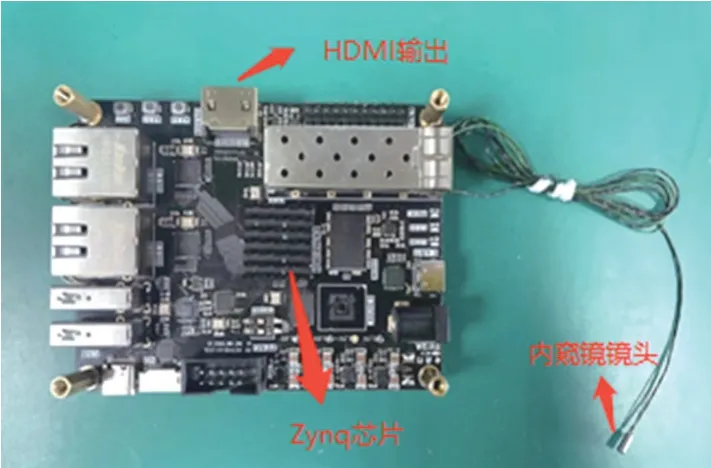

4.1 系统连接实物

系统试验时,为了减少阻抗不连续对摄像头模拟信号输出的影响,OV6946 通过阻抗为50 Ω 的屏蔽线焊接到OV426 引出的4PIN 通孔上。经板卡处理后由HDMI 输出。每根屏蔽线的屏蔽丝均做接地处理。其系统连接关系如图13 所示。硬件实物如图14 所示。

图13 系统连接关系图

图14 测试系统-测试装置实物图

系统上电后,直接通过HDMI 接口即可查看实时的摄像头采集回的图像。

4.2 测试结果

为了验证系统功能的实现,将板卡供电,通过HDMI 连接显示器。分别写入算法处理前后的代码来验证算法实现效果。固化到FPGA 端的算法总体综合出的结果如图15 所示。

图15 Vivado HLS 算法综合结果

由图15 可知,目标时钟周期为10 ns,综合后的设计所估计的时钟周期为6.381 ns,满足时序要求。最高延时为309 124 个时钟周期,即执行本设计的算法处理一帧图像的时间为3.091 24 ms。由于30 fps的内窥镜,图像帧间隔为33.3 ms,故完全满足实时处理OV6946 内窥镜的400×400 pixel 分辨率,30 帧/s图像的视频流。

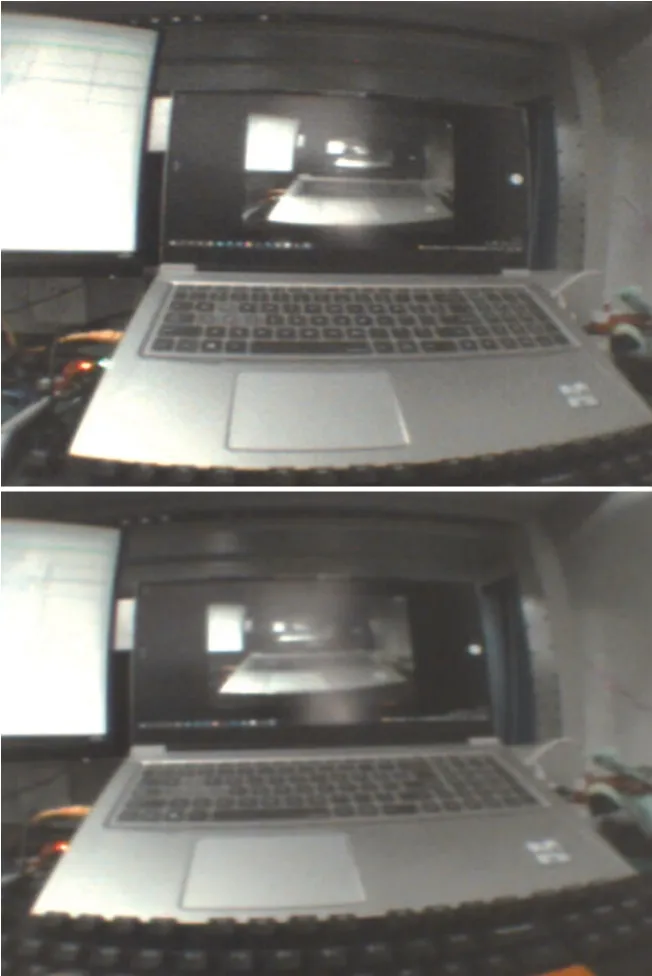

从显示器上可以看到OV6946 传回来的实时图像。重复多次试验可得,该系统可以高效无误地对OV6946 采集回的400×400 pixel@30FPS 的视频流进行实时处理,无肉眼可见延时。其性能达到了预定的指标。算法处理前后的效果图如图16~图19 所示。

图16 白平衡/CCM 前(左)后(右)对比图

图17 暗部增强前(左)后(右)对比图

图18 伽马值1.3(左)伽马值0.6(右)对比图

图19 双边滤波前(上)双边滤波后(下)对比图

5 结论

本文从医用内窥镜视频流采集处理需求出发,设计了基于Zynq 的医用内窥镜视频流采集与处理框架,对不同功能进行了模块化设计,同时利用了Zynq 芯片的协同处理优势。在完成技术指标的同时采用尽量少的元器件,减少了系统的复杂性,提高了系统的可靠性。本文所介绍的医用内窥镜采集处理框架工作稳定,在满足需求的前提下,对各个指标均进行了优化设计。同时,该系统已投入到实际使用中,具有较好的实用价值。