高分辨中子闪烁体探测器读出电子学研制

2023-12-27周诗慧黄河万志永2陈少佳朱志甫2唐彬黄畅王修库曾莉欣于莉杨浩刘慧银岳秀萍2赵豫斌孙志嘉

周诗慧 黄河 万志永2,,4 陈少佳 朱志甫2,,4 唐彬 黄畅 王修库 曾莉欣 于莉 杨浩 刘慧银 岳秀萍2,,4 赵豫斌 孙志嘉

1(郑州大学 郑州 450001)

2(中国科学院高能物理研究所 北京 100049)

3(核技术应用教育部工程研究中心 东华理工大学 南昌 330013)

4(散裂中子源科学中心 东莞 523803)

作为研究物质结构和动力学性质的理想探针,中子散射技术已在凝聚态物理、化学、生命科学、材料科学[1-2]等领域的研究中被广泛采用。先进的中子源是中子科学研究的基础[3]。利用中子源可以研究材料的微观结构,促进物体微观特征的科学研究[4]。中国散裂中子源(China Spallation Neutron Source,CSNS)是我国第一台散裂中子源,它为多个学科前沿领域的研究提供了一个功能强大的国际化科研平台[5-9]。能量分辨中子成像谱仪(Energy Resolved Neutron Imaging Spectrometer,ERNI)是中国散裂中子源目前在建的谱仪,其布局如图1所示。

图1 ERNI谱仪布局示意图Fig.1 Schematic diagram of ERNI layout

中子探测器是中子谱仪的关键核心设备,决定着谱仪的分辨能力和综合性能[10]。由于中子闪烁体探测器具有成本低、可大面积拼接等优点[11],ERNI谱仪的衍射探测器90°分区采用了高位置分辨的中子闪烁体探测器作为探测设备。该探测器整体结构如图2所示,它由6个扩展单元组成,每个扩展单元有效面积为1 354.752 mm2。单个扩展单元由两部分组成:闪烁屏、4×30矩阵式硅光电倍增管(Silicon Photomultiplier,SiPM)。SiPM具有良好的光子分辨能力,且光响应快、工作电压低、抗磁场干扰强、价格便宜,被广泛应用于核探测领域[12]。探测器的每个扩展单元由120个SiPM紧密排布,其中每行有30个SiPM,每列有4个SiPM,单个SiPM像素为3.36 mm×3.36 mm。探测器的工作原理是:热中子入射至闪烁屏,与闪烁屏中6LiF发生6LiF(n,α)T核反应,核反应产生α粒子和氚核,α粒子和氚核在闪烁体材料中沉积能量,通过原子的电离激发、退激释放出接近可见光的闪烁光,闪烁晶体与SiPM紧密耦合,SiPM把光信号转化为电脉冲信号。

图2 探测器结构示意图Fig.2 Structure diagram of the detectors

谱仪要求探测器水平方向(X方向)的位置分辨≤1 mm,在X方向上共有30个SiPM,总长度为100.8 mm,这就要求电子学的积分非线性≤1%;谱仪要求探测器的时间分辨≤1 μs,为了实现高的时间分辨,要求电子学时间分辨≤100 ns。读出电子学采用单通道读出方法可以获得SiPM的最佳时间性能,但是大量的SiPM就需要海量地读出电子学通道,从而导致电子学规模大、功耗高、系统复杂。为此,读出电子学采用了电容网络复合读出电路和重心法结合的方法来降低SiPM处理的复杂性,从而用较少的读出通道获得高分辨的位置定位结果[13-16]。

1 读出电子学硬件设计

该探测器的读出电子学由三部分组成,分别为电容网络复合读出电路、前置放大板和数字读出板。为了实现探测器高位置分辨的测量要求,读出电子学采用了电容网络复合读出方法处理SiPM输出信号,把每一行的30个SiPM通过电容网络连接,并在两端输出信号,这样有效地减少了电子学读出通道,降低了探测器后端电子学的功耗,缩小了电子学的规模;电容网络输出的信号经放大、滤波后送给高速模数转换器(Analog to Digital Converter,ADC)采集并数字化,然后可编程门阵列(Field Programmable Gate Array,FPGA)把能量信息和时间信息按照固定数据格式打包、缓存后发送给后端系统;最后根据重心法计算得到中子事例击中位置。总体系统框架如图3所示。

图3 读出电子学结构示意图Fig.3 Block diagram of the readout electronics

1.1 电容网络复合读出

采用通道复用的方法,可以大量减少后续电子学读出通道,从而降低系统功耗,提高系统集成度。在目前应用最广泛的通道复用方法中,电阻网络复合读出和电容网络复合读出是应用最多的两种方法。电阻网络复合读出方法由于低通滤波效应影响,在大通量高计数率下会造成时间性能下降。因此,本设计采用了电容网络复合读出法,它是一种利用电容进行电荷分配的多路复用方法,其构造简单,且比电阻多路复用网络的电阻少,具有优越的时间性能。设计中采用的电容网络如图4所示。其水平方向的位置分辨由重心法计算可得,垂直方向的位置分辨主要取决于物理位置。

图4 电容网络示意图Fig.4 Diagram of capacitive network

电容网络复合读出的工作原理是[17]:把1×30 SiPM线列的30个输出信号编码为两个位置信号,根据连接到每个阳极的加权电容器的数量,SiPM的每个阳极信号(A1~A30)被分成一个或两个信号。然后将每个分割信号传输到其中一个位置信号输出通道,阳极信号与加权值(即电容值)之间的关系如式(1)和式(2),通过式(3)和式(4)可得,探测到的电荷量和位置关系,其中Qa和Qb为编码电路两端电荷量的值,E为探测到的电荷量,X为将A1作为原点时在水平上得到的位置。

1.2 前置放大板

前置放大板的作用是把电容网络复合读出电路输出的微弱信号放大调理,再进行成形滤波,滤除高频噪声,并使波形更加平滑,以进一步提高信噪比[18],并易于ADC采集和处理。

每块前置放大板有16路电子学处理通道,其中两个通道一组,处理一组1×30的SiPM阵列经电容网络复合电路输出的信号,每块前置放大板可以同时处理两个4×30的SiPM阵列的输出信号。前置放大板对电容网络的输出信号处理方法如图5所示。每组电容网络复合读出电路输出的两路电压信号,首先进入一个低噪声、高带宽的前置放大器进行放大。前置放大器的增益带宽积为3.8 GHz、压摆率为1 350 V·μs-1,高的增益带宽积保证了前置放大器可以实现高增益放大,快的压摆率保证了原始信号的前沿时间信息可以有效地保存。前置放大器输出的信号然后进入二阶RC滤波成形电路,滤除信号中的高频噪声,从而提高测量精度。由于前置放大板和后端数据处理板是通过5 m长的线缆连接,经过滤波后的信号需要通过驱动电路来提高信号的驱动能力,避免信号远距离传输衰减。驱动电路把单端信号转换为差分信号,然后通过差分线缆送给后端数据处理板的高速ADC采集。相比单端信号,差分信号具有能有效抑制电磁干扰(Electromagnetic Interference,EMI)、抗干扰能力强等优点,更适合远距离传输、较高信噪比要求的场合。前置放大板的增益约为15 V·V-1,经过前置放大板处理后的信号幅度范围大约为后端高速ADC输入量程的90%,这样既保证了不会由于信号超量程损坏ADC,同时充分利用了ADC的全动态范围,从而使系统具有良好的信号分辨能力。前置放大板如图6所示。

图5 前置放大板信号处理方法示意图Fig.5 Schematic diagram of preamplifier board's signal processing method

图6 前置放大板照片Fig.6 Photograph of preamplifier board

1.3 数字读出板

数字读出板对前置放大板的输出信号进行采集并数字化,然后进行触发判选从而甄别出中子事例,排除SiPM热噪声、γ等干扰信号,最后把中子事例对应的幅度信息和时间信息打包,缓存处理后按照固定的数据格式通过千兆以太网发送给后端处理;数字读出板同时集成了高压、精密ADC、高压监测电路、温湿度监测电路等电路模块,FPGA根据后端系统的命令实现对这些模块的配置和控制,同时把相应的状态和监控信息发送给后端系统。每块数字读出板包括32个独立的高速ADC采集通道,可以同时连接两个前置放大板。FPGA是数据读出板的数据处理和控制核心,本设计采用了美国赛灵思(Xilinx)公司的kintex-7系列FPGA集成电路XC7K325T-2FFG900I。

高速ADC把前置放大板输出的模拟信号转换为数字信号,它的精度决定了整个系统的测量精度。传统的并行高速ADC需要多位数据线来传输数字化数据,不太适合集成度高的应用场合。随着电子技术的发展,近年来出现了新型的高速串行接口ADC,它在不降低ADC采样率的前提下,仅通过少量的高速信号线来实现数据的海量传输,这样节省了PCB的面积和大量的数据口线,从而提高系统的集成度。

本设计采用了TI公司的8通道、12位、最高采样率为65×106的低功耗高速串行ADC芯片ADS5282。它和FPGA通过串行低电压差分信号(Low Voltage Differential Signaling,LVDS)接口对数据进行传输,每个通道仅采用一组差分LVDS线传输数字化数据。FPGA把高速ADC的采集数据处理后通过光纤接口发送给后端系统分析和处理[19]。和网线传输方式相比,光纤数据传输方式具有传输距离远、抗干扰能力强等优点。同时为了保证数据命令的稳定可靠传输,使用商业化的SiTCP软核实现数据和命令的交互,它采用传输控制协议/因特网互联协议(Transmission Control Protocol/Internet Protocol,TCP/IP)完成数据传输,上位机采用三次握手的用户数据报协议(User Datagram Protocol,UDP)实现对读出电子学的命令配置[20]。

为了预防网络拥塞等突发情况,设计还采用了两片4 GB容量的第三代双倍数据率同步动态随机存取存储(Double Data Rate Three Synchronous Dynamic Random Access Memory,DDR3)作为数据缓存,提高读出电子学的处理和数据缓存能力,从而提高系统的稳定性。为了实现多模块数据同步,数字读出板使用T0信号作为触发来打包和传送缓存数据。T0是中国散裂中子源质子打靶的周期信号,它的周期为25 Hz[21]。为了保证T0信号的可靠传输,T0信号采用抗干扰能力较强的低压正发射极耦合逻辑(Low Voltage Positive Emitter Couped Logic,LVPECL)电平。

稳定可靠的工作电压是SiPM正常工作并发挥出优良性能的必要前提。为了提高整体系统的集成度,电子学集成了自研的高压模块。高压模块利用DC-DC模块产生高压来给SiPM供电,它以STM32L431CCT6作为核心控制器件,通过12位精密数模转换器改变DC-DC模块的输入电压来实现高压变化,进而达到设计要求。每个高压模块有两路独立高压,输出范围为+26.5 ~ +33V,输出的纹波噪声不超过10 mV,分别为前端的两个前置放大板对应的SiPM阵列供电,上位机可任意配置高压模块两路高压的输出。由于SiPM的增益和热噪声会随着温度的不同而改变,为此采用根据SiPM探头的温度实时调整高压的方法,补偿SiPM温漂的影响。数字读出板通过一根5 m长的线缆把一个IIC接口的温湿度传感器放置在前端SiPM阵列位置附近,FPGA定时采样前端探头的温度,并根据温漂补偿算法来定时调整高压输出。同时数字读出板上还集成了一路温湿度传感器,用来检测数据读出板本地的温度和湿度,并通过光纤网络定时发送给后端用于监测。为了预防高压异常,数字读出板设计了高压电压和电流监测电路,FPGA通过1个16位、8通道的精密ADC实时采集监测每一路高压的电压、电流,当发现异常时,及时报警并关断高压,避免损坏SiPM阵列。数字读出板如图7所示。

图7 数字读出板照片Fig.7 Photograph of digital readout board

1.4 FPGA逻辑设计

前置放大板把模拟信号滤波成形再被ADC采样和量化后送入FPGA,送入FPGA的数据需要进行串并转化和数字求和得到每个通道信号的能量信息。FPGA最后把包含能量信息和时间信息的数据包通过千兆光纤网络传输到后端。后端根据得到的时间信息和能量信息,进一步完成能量和时间数据的处理和修正,从而得到中子事例的击中位置和飞行时间。

FPGA固件逻辑设计对于完成单事件处理单元的功能和提高能量、时间测量精度具有非常重要的作用。单中子事例的处理流程如图8所示。两路高速ADC通道分别对应处理一组SiPM线列的两端输出。高速ADC采样和量化后的数据为12位串行的LVDS数据流,数据采样率为480×106s-1。为了降低数据处理的速率,得到每个采样点量化的码值,在FPGA逻辑设计中首先把ADC输出的串行数据转化为并行数据。为了排除噪声和γ等干扰信号的影响,必须设置合适的触发阈值。当两路数据有任何一路超过触发阈值时,固件产生一个公共触发信号给单事件处理单元进行能量信息计算,并记录下时间信息。公共触发信号采用这种逻辑或的产生处理方式,有利于提高系统的计数率。阈值可由上位机通过光纤以太网任意设置。当接收到公共触发信号后,FPGA逻辑启动数字求和逻辑来进行能量信息的计算。

图8 单中子事例处理流程Fig.8 Processing procedure of single neutron event

为了减少ADC采样和量化后波形的基线波动,在信号求和之前的几个采样时钟周期计算基线平均值,作为数字求和波形的基线。这种采用动态基线作为基线的处理方法,可以克服基线温漂对测量精度的影响。求和开始后,每一个串并转换后的数据与基线进行比较运算,扣除基线的影响。求和点数N可由上位机任意配置,N越大能量测量的精度越高,但同时会增加系统的死时间,因此选定的N值在确保求和时间覆盖信号宽度的前提下要尽可能小。求和完成后,单事件处理单元逻辑对数据进行数据组帧,帧数据包括中子事例击中时间信息、SiPM线列两端的能量信息,最后把帧数据写入单事件处理单元先进先出存储器(First in First out,FIFO)。

数字读出板总共有16个单事件处理单元FIFO。为了实现数据的并行处理,减小系统死时间,采用了多级流水线的方式实现数据的缓存。每4个单事件处理单元FIFO汇总到一个二级FIFO中,4个二级FIFO的数据通过令牌环的方式最终写入到4G的DDR3中。大容量的缓存提高了系统的吞吐率,有效的降低了系统的故障率。数据最终通过SiTCP软核发送给后端系统,在DDR3和SiTCP软核间还有一级FIFO用来实现数据缓存和隔离[20]。

2 性能参数测试

在读出电子学设计和调试完成后,为了验证电子学的性能,前期在实验室进行了时间分辨测试和积分非线性测试。完成实验室测试后,在中国散裂中子源20号中子束线上和探测器一起进行了带束测试,包括位置分辨和探测效率测试。

2.1 实验室测试

2.1.1 时间分辨测试

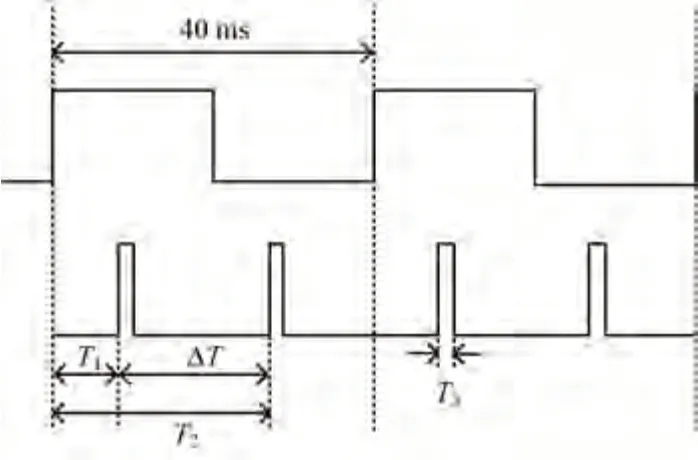

Tektronix公司的高精度信号发生器AFG3252C有两个分别独立的信号产生输出通道,测试信号时序关系如图9所示,一个通道产生周期40 ms、占空比50%的模拟T0信号输出给数字板,一个通道产生两个间隔相距ΔT,即5 ms的正向类指数脉冲信号,脉冲的幅值为100 mV,宽度为T3,即500 ns,并以模拟T0为周期把产生的类指数信号通过自研的1:16扇出板送给研制的电子学样机。读出电子学以T0为周期打包并发送事例击中时间给上位机,上位机通过分析20 000个击中的时间信息,通过式(5、6)[20]计算以及测试得到最小时间分辨如图10所示,测试表明最小时间分辨约为12 ns。

图9 测试信号波形Fig.9 Waveform of test signal

图10 时间分辨测试结果Fig.10 Result of time resolution test

2.1.2 积分非线性测试

手动输入峰峰值从0~100 mV、步进为10 mV的经平移变换后的正弦波信号,信号宽度为1 μs,周期为10 μs。首先通过式(7)计算出输入信号的面积,然后对数字化后输出的值进行积分求和,多次测量求平均值,最后将输入值通过理论计算所得到的面积与数字化后输出并积分求和后的值进行线性拟合,再通过式(8)得到积分非线性,依次可以求出32个通道的积分非线性。32个通道的积分非线性分布如图11所示,积分非线性最大不超过0.95%。

图11 32通的积分非线性Fig.11 Integration nonlinearity of 32 channels

式中:DIV为实验点在Y轴方向偏离拟合直线的最大绝对值;INPUTY满刻度输入对应的Y值;dy拟合直线在y轴上的截距。

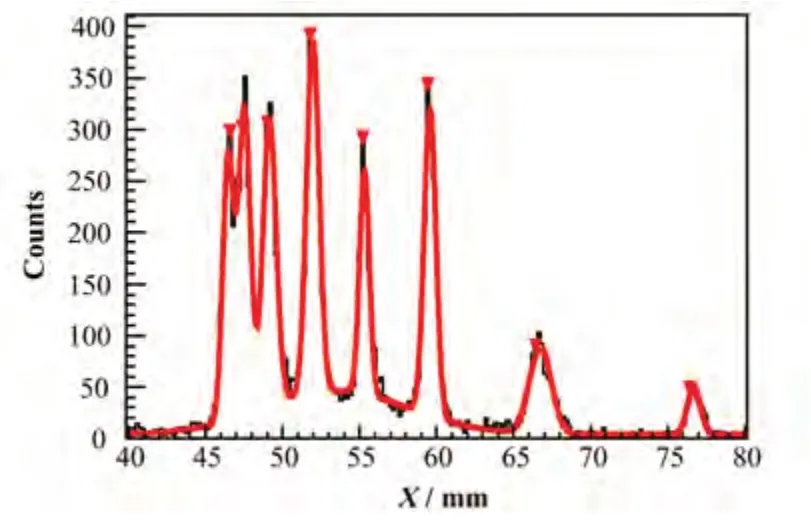

2.2 束线测试

为了验证研制的读出电子学是否满足高位置分辨中子闪烁体探测器的物理设计指标,探测器和电子学在中国散裂中子源20号中子束线开展了探测器位置分辨和探测效率实验,现场测试如图12所示。中国散裂中子源20号中子束线的中子能谱范围为1~5 Å,通过云母单色器把入射中子单色为单能或准单能中子(1.6 Å和2.8 Å)。为了测试探测器位置分辨能力,把由热中子阻挡材料加工的狭缝阵列(共8条缝,狭缝宽度均为0.5 mm,从左至右狭缝边缘间距分别为0.5 mm、1 mm、2 mm、3 mm、4 mm、6 mm、8 mm)放置在探测器样机入射窗前,狭缝阵列垂直于探测器水平方向。单色器单色的单能中子入射到狭缝阵列后绝大部分中子被吸收,只有狭缝位置的中子能够穿过狭缝被探测器探测。探测的中子信号经读出电子学处理后,数据通过千兆光纤网络上传给上位机,由重建算法解析后得到狭缝阵列的图像。通过分析狭缝阵列沿水平方向投影图即可确定探测器水平方向的位置分辨。测试得到的狭缝阵列沿水平方向投影图如图13所示,可以清晰看到,1 mm的狭缝满足设计指标。为了验证探测器的热中子探测效率,借助高气压标准3He管(已知探测效率),分别测试了探测器对1.6 Å和2.8 Å中子的探测效率。测试结果显示,采用研制的电子学系统,探测器对1.6 Å和2.8 Å中子的探测效率分别达到了65%和75%左右,均达到了设计指标。

图12 中子束线现场样机测试Fig.12 Photograph of experimental on-site prototype testing at neutron beam line of CSNS

图13 位置分辨测试结果Fig.13 Test result of position resolution

3 结语

本文介绍了用于能量分辨中子成像谱仪的高分辨中子闪烁体探测器读出电子学,它采用了一种电容网络复合读出电路和电荷重心法相结合实现探测器高位置分辨的技术方案,在其基础上,作者完成了读出电子学系统的研制和测试。实验室和束流测试结果表明,该读出电子学系统达到了工程设计指标。目前该电子学系统正在进行批产和测试,计划2023年底安装到能量分辨中子成像谱仪现场。它的研制成功,为能量分辨中子成像谱仪保质保量完工、顺利开展实验提供了可靠的技术保障。

作者贡献声明周诗慧、万志永负责整体系统的设计与测试,以及论文的撰写和修改工作;陈少佳负责整体项目的进展,以及论文的修改;黄河、朱志甫负责论文的审订;唐彬、黄畅、王修库参与实验具体测试及数据记录;曾莉欣、于莉、杨浩、刘慧银、岳秀萍分别从自己擅长的领域出发进行资料的搜集和整理;赵豫斌、孙志嘉负责研究的提出和指导。