基于逻辑门的新型多主访问RS485总线方案*

2023-12-13林云策朱浩然包志舟

林云策,朱浩然,包志舟

(1.温州大学电气与电子工程学院,浙江 温州 325035;2.温州大学乐清工业研究院,浙江 温州 325035;3.浙江人民电器有限公司,浙江 温州 325035)

0 引言

RS-485总线具有接口芯片丰富、硬件成本低、操作方便、低速传输时传输距离远等特点[1-2],被广泛应用于电镀电源、实验室电源管理、电力终端设备管理等领域[3-4]。传统的RS-485 总线应用多为基于Modbus 协议的一主多从(一个主节点,多个从节点)通信方式,采用主节点轮询从节点的方式进行通信[5-7],优点是通信方式简单。但一主多从通信模式只适合规模不大或对通信实时性要求不高的场景。随着从机节点数的增加,主节点轮询从节点的时间会变长[8-9]。因此。为了提高通信实时性,拓宽RS-485总线的应用,多主访问RS485通信方式被提出[10]。多主访问RS485 通信方式是利用主节点可以主动发起通信的特点,取消了轮询机制,采用通信节点主动变为主节点进行主从通信的方式,大大提高了通信的实时性。但是因为只有一条总线,当多个主节点发起通信时,在总线上会发生通信拥堵,如何解决总线上的通信拥堵是实现多主访问RS485总线技术的关键[11]。

文献[12]提出将RS-485 总线接收器的输出端反相后接到CPU 的外部中断管脚,用触发中断的方式判断总线上是否有数据传输,同时结合定时器中断判断总线是否空闲。但需要软件定时器的配合,且对并发节点的处理只是简单采取随机延时后重发,总线利用率不高。文献[13]提出利用硬件电路实现,具体的电路由两个对称RS485 总线接收器构成,需要进行合适的阻抗匹配,两个接收器的输出相与后得到总线状态信号。该方案电路复杂,容易引入故障点,且带载能力较弱,不能超过16个节点。文献[14]提出利用74HC123 单稳态触发器形成总线状态标志,判定当前总线是否为忙。该方案单稳态时间设计比较依赖固定的通信波特率,缺乏对并发主节点的有效的处理方式,导致总线利用效率仍然不高。文献[15]提出利用定时器进行总线侦听,再对总线进行改造,使之具备逻辑“与”功能,配合具有优先级的数据帧解决多节点并发问题。该方案相对优秀,总线利用率较高但需要用到定时器资源。文献[16]提出一种令牌环机制,主节点按一定顺序进行通信,需要紧急通信的主节点在一定抢发时间内争抢总线,并发的主节点,按不同优先级重复发送数据,竞争总线。该方案适合规模小、数据量小的场合。

以上各方案都可以基本实现多主访问的功能,但是都有各自的局限性,针对不同的场合都有各自的用处。针对现有的方案,本文提出了一种不占用软件资源、带载能力强、总线利用高的新型的可支持多主访问的RS-485总线技术方案。

1 整体设计方案

1.1 多主访问RS485存在的技术问题

多主多从模式设有多个主节点,随机发起通信的多个主节点容易在总线上出现通信拥挤。为了避免这种情况,主节点的主动通信需要合理规划,有效化解冲突。为此,节点需要满足两点要求。第一,主节点只有在检测到总线空闲的时候,才有权限向总线发送数据,进行有效通信。第二,侦听总线空闲虽然避免了主节点在总线忙时发送数据。但无法避免同时检测总线空闲的主节点一起抢占总线,造成通信混乱。因此需要对多个并发的主节点进行仲裁,选中唯一可通信节点。

针对第一点,需要设计出侦听总线空闲机制,通知主节点具备发送条件。针对第二点,需要设计出并发冲突节点竞争机制。

对侦听总线空闲机制的设计,是抓主总线空闲的特征,即总线空闲时,总线信号不变;总线繁忙时,总线信号是变化的。因此可以根据这一特点,利用不同的技术手段和资源,根据需求设计总线空闲侦听机制。

多个并发主节点在总线发生冲突时,会造成总线电平的不可预测混乱,导致节点接收的数据与发送端不一致。是否对发生冲突的总线规律化处理,冲突节点以何种方式再次发送是并发冲突节点竞争机制设计的关键问题。本文将侦听总线空闲机制和并发冲突节点竞争机制合称为冲突检测机制。

1.2 多主访问RS485总线设计方案

工程技术方案的设计除了解决功能性要求外,还需要考虑软硬件资源配置的问题。本文针对侦听总线空闲机制和并发冲突节点竞争机制的关键问题,在只添加少量硬件资源,不占用软件定时器资源的条件下,提出了可靠性高的冲突检测硬件电路,再配合特定的发送数据格式,实现可支持多主访问的RS-485总线通信方式。

2 多主访问RS485硬件电路设计

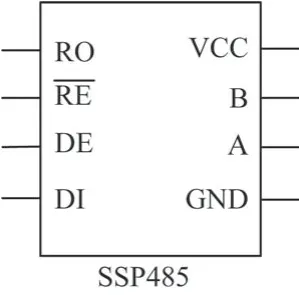

2.1 RS-485接口介绍

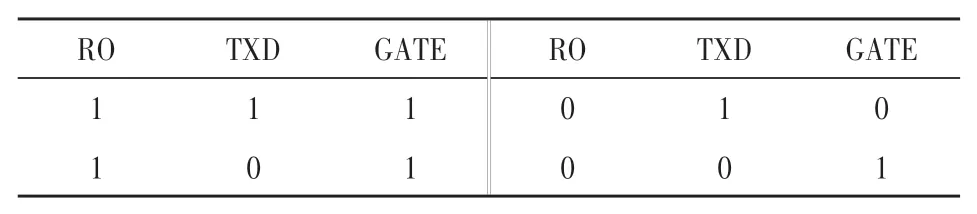

常用485接口芯片的接口如图1所示。该芯片可以将实现USRT 串口电平格式和RS485 总线的电平格式相互转化。该芯片一共有8 个引脚其分别为接收数据输出脚RO、接收控制脚RE、发送控制脚DE、发送数据输入脚DI、接受数据输出脚和一对总线接口引脚A、B 所构成[17]。RS485 采用差分传输即通过AB 间的电压差确定。发送控制脚DE 为低电平时,A、B 口为高阻态;发送控制脚DE 高电平时,使能发送控制脚,令A、B 解除高阻态。对于接受数据控制脚也同理,不过控制逻辑相反。RS-485引脚详细的功能真值表1所示。

表1 输出真值表

图1 RS-485接口

2.2 冲突检测电路

本文是利用485 芯片的AB 口高阻态特点,并配合少量的逻辑门电路,实现冲突检测硬件电路,其结构图如图2所示。对485接口芯片的数据接收控制脚位一直使能。

图2 冲突检测电路结构

冲突检测硬件电路的左边接MUC,RS-485 为控制信号,TXD 为串口输出,GATE 为冲突检测信号。该冲突检测的电路的原理是在当总线发生冲突时,GATE 会出现低电平;当总线空闲时,GATE会出现高电平。

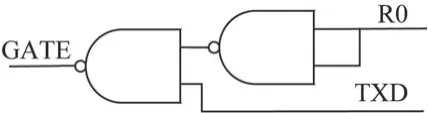

输入环节是由1个与非门构成,如图3所示。与非门的两个输入分别是RS485 控制信号和串口输出TXD,与非门的输出连接485 芯片的数据发送控制脚。串口输出TXD 和485 接口芯片的数据发送脚DI 直连。输入环节功能真值表如表2 所示。由表可知,输入环节的特点是当DIS_RS485 信号为逻辑“0”时实现485 通信;当DIS_RS485 信号为逻辑“1”时可以令串口输出的逻辑“1”,不是通过485 芯片的逻辑电平“1”的输出,而是通过A、B 总线上的电阻来实现逻辑“1”的输出。而当有节点出现逻辑“0”时总线电平被拉低,变成逻辑“0”。这种输出方式可以保证总线上多个节点通信,不会破坏总线电平标准,有很强的带载能力,且可以据此对节点进行优先级设置。

表2 输入环节功能真值表

图3 输入环节电路

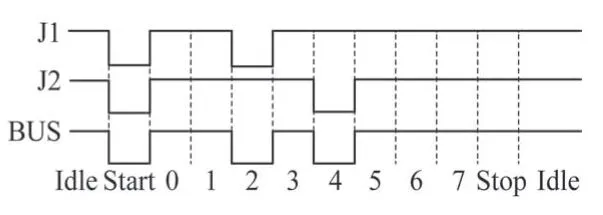

当总线上有两个节点J1、J2 分别输出USRT 串口格式字节0xFC 和0xEF 时,总线上收到的是0xEC。如图4所示。

图4 多节点总线冲突情况

输出环节是由1 个非门和1 个与非门组成,输出环节的电路如图5所示。

图5 输出环节电路

输出环节的输入是串口输出TXD 和485 接收数据输出脚RO。输出环节的作用是利用总线数据和节点自身的输出判定总线是否忙,功能真值如表3 所示。由表可以看出输出环节的功能是类同或门。因为输入环节的存在中,在本电路中第二种情况不会发生。当本节点收发逻辑电平不一致,即GATE为逻辑0时,说明当前总线不空闲(仅识别GATE为1,不能说明总线空闲)。利用GATE电平的变化的规律,MUC 通过一定的软件手段,可以判定总线是否为忙。

表3 输出环节功能真值表

冲突检测电路对传统的485 总线和控制机制进行了改造。将传统485 通信的逻辑“1”的电平输出,改为高阻态偏置电压输出,实现了总线冲突时高电平保持,出现低电平拉低的规律化特征,并实现节点输出数据和总线数据的硬件比较。

2.3 工作机制

MUC 对冲突检测电路的GATE 口进行检测,只检测到逻辑电平“1”时,授予节点通信权限;一旦检测到逻辑电平“0”,该节点需要重新申请通信权限。

MUC 的一个外部中断口接GATE 口,采用下降沿触发或低电平触发中断,通过中断对节点进行授权。

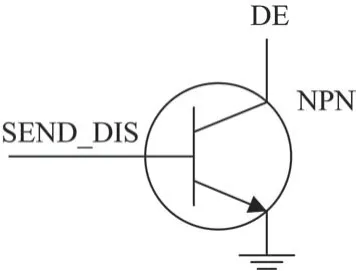

为了更好地侦听总线是否空闲,且不影响总线通信,在发送数据引脚上额外增加上1 个发送控制电路如图6 所示。利用1 个NPN 三极管,控制485 芯片的数据输出控制脚,在侦听总线时,SEND_DIS输出高电平,拉低发送数据控制脚DE的电平,防止查询总线帧对总线的影响。查询总线帧是节点串口以总线485通信最低波特率的一半的查询字节0xFF。因为串口发送字节时,存在一个低电平的起始位,所以查询总线帧可以优先检测出,总线上是否有通信发生。若在发送查询数据帧期间,GATE口出现低电平则说明系统忙,否则总线空闲。当总线上在两个字节波特率时间内没有字节发送时,说明不存在有效通信,所以可以认定总线空闲。

图6 发送控制电路

获得发送权限的主节点按485 通信波特率发送优先级数据帧,GATE 脚出现低电平的主机退出竞争,继续进行侦听总线,申请发送权限。同时发起通信的主节点按优先级获得发送权限。

优先级和二进码的换算关系如式(1)所示。

式中:n为优先级数;j为参与计算的bit-1 位数;i为先发送比特位数(i=0,1,2,…,j),数字越小越早发送;ai为对应比特位上的取值。

一个字节的高位5 位取相同位数,只计算低3 位比特位,按右边为低位先发设计的优先级数据帧的形式如表4所示。

表4 计算3个比特位的地址码

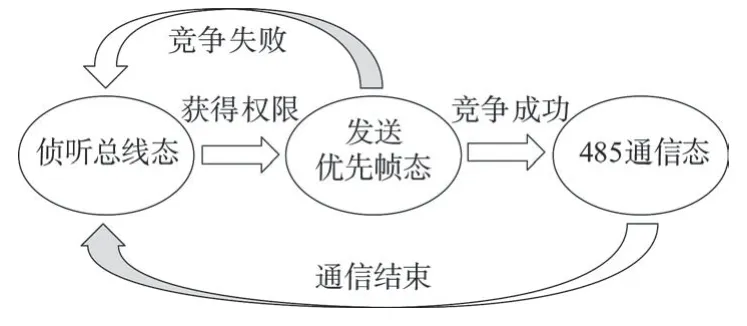

每个节点的状态都是在侦听总线态,发送优先帧态,485态之间相互转换。状态转化如图7所示。

图7 节点状态转化

本机制不需要用到定时器资源,硬件实现冲突检测。

3 多主访问485软件设计

3.1 主控芯片要求

本本设计方案对主控芯片的要求偏向IO 口资源,而不占用定时器资源。这对一些对定时器资源有要求的节点事务,且主控定时器资源少的主控有明显的优势。例如像51 单片机这种低成本、定时器资源少的主控,一旦存在定时查询事务,定时器资源紧张的情况下,采用本方案就可以明显缓解紧张资源。这为工程上提供了一种新的方案选择。

3.2 通信状态转化程序设计

对总线侦听程序的设计重点是在总线空闲判断和状态转换。总线空闲判断要和各个状态转换相匹配。状态转换主要是冲突检测电路进行功能配置和必要的数据帧配合。

节点的起始状态为侦听总线态,默认具有通信权限。当节点有通信需求时,才会发送查询总线帧。一般先配置冲突检测电路功能令SEND_DIS=1,DIS_RS485=1,再开启外部中断,然后配置串口发送查询总线帧。外部中断的优先级必须高于串口中断的优先级。在外部中断函数中,对节点进行授权剥夺。在发送完查询总线帧后且通信权限未被剥夺,节点进入发送优先帧态。

进入发送优先帧态的节点,也是先配置冲突检测电路功能,令SEND_DIS=0,DIS_RS485=1。然后发送优先级帧,发送完成后,再查询节点通信权限。如果仍然具有发送权限,则进入485 通信态,否则退回总线帧听态,并恢复其通信权限,进行新一轮的总线查询。

进入485 通信态的节点,配置相应的冲突检测电路功能即令SEND_DIS=0,DIS_RS485=0。进行485 通信,通信结束后可以关闭通信或者总线侦听态,等待下一次通信需求的发起。程序设计的流程如图8所示。

图8 程序设计流程

4 实验验证和结果分析

本文通过MATLAB Simulink 平台对方案进行逻辑验证了。实验平台对485总线AB 总线进行了合理简化,一个节点的电位模拟总线信号,具体接法见图9。用1个受控的开关模拟高阻态,开关的控制脚模拟485 芯片数据发送控制脚DE,开关断开为高阻态,开关闭合总线电平由受控电压源决定,即正常485通信。冲突检测电路的3个与非门用了自带的模型。节点的主控master 的控制逻辑用MATLAB FUNCTION 函数进行模拟。Change 引脚为波特率切换信号。两个方波的频率模拟波特率,输入master 模块的baud 脚。Trig 脚模拟数据发送请求,高电平为请求数据发送,低电平无请求。Byte 脚输入优先级地址帧。Byte_485 模拟后续通信数据。其他脚和上文描述的意义相同。

图9 多主访问485总线方案

通过上述平台以两个主节点为例模拟本方案多节点错时通信、多节点并发通信工况。

侦听总线空闲通的模拟情况如图10所示。由图10可知当节点J1 正在通信的时候,节点J2 发送了总线查询帧,当其遇到了J1通信过程中的低电平时,J2的GATE2脚迅速被拉低,并且重新发送总线查询帧,并重复上述过程。一直到节点J1 完成通信后,节点J2 检测总线空闲,才进入正常的通信。

图10 多节点错时通信

由图11 可知节点J1 和节点J2 同时发起通信要求,同时监听到总线空闲,并发进入发送优先帧态。由于节点J2的优先级比J1高,节点J1首先发送的电平为高电平遇到节点J2 发送的低电平后,GATE1 电平被迅速拉低,节点J1 退出竞争,进入总线侦听态,而节点J2 竞争成功,继续通信。直到节点J2通信结束后,节点J1检测到总线空闲,并获得总线通信权,开始正常通信。

图11 多节点并发通信

从仿真结果可以看出当存在节点发起通信请求两个通信字节时间后,必定有节点进行有效通信,体现了本方案总线高利用率和稳定性。

5 结束语

本文对多主访问的RS-485总线技术进行了研究,针对总线空闲侦听机制和多节点并发竞争机制两个问题,提出了基于逻辑门的冲突检测电路和相应的软件算法,并在MATLAB Simulink 搭建了方案模型,并进行不同工况的仿真。仿真结果证明了本方案的可行性。此外,本方案还具备以下优点。

(1)在不采用定时器资源下,具备有高效的总线空闲侦听机制,支持大规模节点的优点,为定时器资源少的主控芯片,提供了新的多主访问RS485总线技术方案。

(2)在节点发送数据过程中就自动完成了总线竞争而不被打断,无需强化冲突,浪费总线资源,大大提高了总线利用率。

本文为扩展RS-485多主访问总线技术的应用做出了一定的贡献。