随钻声波测井井下算法测试系统数据交换接口设计

2023-12-06郝小龙高国寅

王 伟,郝小龙,周 静,杨 诚,高国寅

(1.西安石油大学 电子工程学院,陕西 西安 710065; 2.西安石油大学 油气钻井技术国家工程实验室井下测控研究室,陕西 西安 710065)

引言

随着油气勘探与开发的不断深入,钻井工程越来越依赖随钻测井的远探测地质导向功能。基于随钻测量、地质导向和旋转导向的“测定导”一体化技术成为优化井筒轨迹、提高油气采收率的重要手段[1-2]。

目前,随钻电磁波电阻率和方位伽马测井在地质导向中应用较多[3-5]。随钻声波测井每个测量点的数据量远大于这两种技术所对应的数据量,无法实时上传全部数据,现有仪器多采用“井下存储数据、起钻后再读取和处理”的方式或者只实时上传滑行波时差信息[6-7]。这导致随钻声波测井数据处理的实时性很差,无法满足钻井的地质导向需求,也阻碍了随钻声波“远探”和“前探”技术的快速发展[8-9]。对数据进行井下处理后只实时上传处理结果,是一种有效的解决方案。

声波测井的数据处理算法主要有预处理[10]、滑行波的时差计算[7,11]、反射波的提取和成像[12-14]、方位接收信号的相控增强[15]等算法。这些算法大多数是在PC机的纯软件中进行测后处理,未考虑测井仪器的硬件条件和执行算法所需要的时间与内存,不能作为井下实时处理算法。因此,必须开发井下硬件支持、运行时间短、占用内存小、兼容数据采集的井下处理算法来满足随钻声波测井地质导向的实时性需求。构建井下算法测试系统并使用已有的测井数据对算法进行验证是开发各种随钻声波测井井下处理算法的重要途径。

数据交换接口是井下算法测试系统的重要组成部分,需要完成测试系统上位机中原始测井数据与前端机SRAM中处理数据的格式转换与双向快速传输两个功能,其中传输速率在20 MB/s以上。本文设计了一种用于井下算法测试系统的数据交换接口,满足了上述需求。硬件上,前端机以FPGA为控制核心,它与上位机通过USB微控制器连接。软件上,USB微控制器固件、FPGA和上位机控制软件三者配合,实现了数据交换接口的通信协议。

1 硬件设计

图1所示为随钻声波测井井下处理算法测试系统的硬件整体框架。该系统由上位机和前端机组成,二者通过USB总线连接。数据交换接口实现上位机与前端机SRAM中数据的格式转换与双向传输。上位机实现测井数据格式转换、USB传输控制和数据二次处理等功能。前端机主要由FPGA、SRAM和USB微控制器三部分组成。FPGA作为井下处理算法的执行中心,一方面能够并行处理多道信号,大大减少算法的执行时间,另一方面与实际测井仪器的采集控制器一致,保证了井下数据处理和采集功能的硬件兼容。高速SRAM挂接在FPGA上,缓存算法运行过程中的大量数据。USB微控制器是数据交换接口的核心硬件,它以从设备的方式与FPGA交换数据,通过USB总线与上位机通信。

USB微控制器选用CY7C68013A,它集成了一个增强型8051微处理器和一个USB 2.0收发器[16]。该芯片以Slave FIFO接口模式挂接在FPGA上,FPGA产生该接口所需的访问时序[17]。IFCLK为接口时钟信号,SLCS为片选信号,SLRD和SLWR分别为读写使能信号,SLOE为读写允许控制信号,FIFOADDR[1:0]为FIFO缓冲区选择信号,FD[15:0]为16位数据总线。FLAGB和FLAGC分别为所选端点FIFO的空标志和满标志,PKTEND为FPGA数据包发送完毕标志。

基于该数据交换接口,按照以下流程测试井下处理算法:(1)上位机将原始测井数据转换为前端机能够识别的数据文件,通过USB微控制器传递,下发至FPGA并存储在SRAM中;(2)FPGA运行井下处理算法,对SRAM中的测井数据进行处理;(3)上位机读取处理后的数据并进行二次处理,评价井下处理算法。

2 软件设计

本工作设计了USB微控制器固件、FPGA和上位机控制软件三部分,它们共同实现了上位机和前端机之间的数据交换协议。

2.1 USB微控制器固件设计

USB微控制器的固件实现了上位机和FPGA之间双向数据的中转功能。它与上位机以低位先发送的方式串行通信,与FPGA以16位数据总线的方式并行通信。图2为微控制器的工作流程,主要包含以下步骤:

(1)系统初始化。配置CPU时钟为48 MHz,USB总线为480 Mbps的高速模式。设置外部FIFO接口工作在从模式,并为该接口分配引脚。

(2)配置Slave FIFO端点。设置EP2端点为自动输出模式,缓存上位机和FPGA之间的下行数据。EP6为自动输入模式,缓存上行数据。这两个端点以16位数据总线和批量传输的方式工作,均配置为四缓冲方式,每个缓冲区512字节。

(3)中断配置。使能INT2和INT4中的USB设备挂起请求、接收到设备包令牌、端点FIFO空满状态等中断。

(4)USB微控制器枚举,与上位机建立连接。在该过程中,上位机获取微控制器的设备描述符等信息,为设备分配配置值,确认USB接口和断点的属性。

(5)等待并分析上位机的事务命令,执行相应的操作。若收到OUT事务,则将下行数据写入EP2端点并通过FIFO非空状态通知FPGA读取数据。若收到IN事务,则将EP6中的上行数据放到USB总线上。这一步骤(图2中虚线以下的过程)是自动执行的,不需要CPU的参与。与此同时,微控制器及时处理各种中断请求,保证设备的正常运行。

2.2 FPGA控制软件设计

本工作在FPGA中设计了USB微控制器和SRAM的访问模块,并在此基础上实现了二者的数据交换。图3为FPGA内部控制的原理框图。PLL模块将24 MHz的输入时钟倍频成48 MHz和96 MHz的时钟信号,分别提供给Slave FIFO接口控制模块和FIFO-SRAM转换模块。Slave FIFO接口控制模块实现两个功能:一是构建USB微控制器内从FIFO的访问时序,对其进行读写操作;二是根据上位机下发的数据包类型,执行下传数据到SRAM、上传数据至从FIFO以及数据处理等操作。FIFO-SRAM转换模块一方面对SRAM进行读写访问,另一方面与Slave FIFO接口控制模块交互,实现数据在FPGA内部的下传和上传。主FIFO模块在数据下传过程中缓存数据,协调读从FIFO操作和写SRAM操作之间的速度差异。该FIFO由IP核生成,深度为4 096,数据宽度为16位。在数据上传过程中,FIFO-SRAM转换模块将SRAM中的数据读出并写入Slave FIFO接口控制模块。

图3 FPGA控制原理示意图

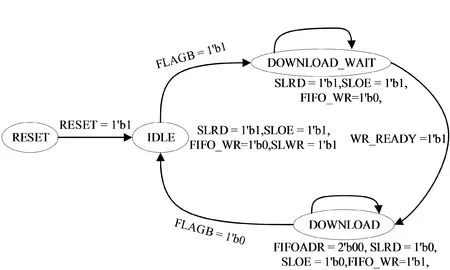

在Slave FIFO接口控制模块中,数据上传和下传两个功能的设计方法类似,都是基于状态机思想。图4为该模块下传功能的状态机图,展示了该模块从USB微控制器的从FIFO中读取数据并写入主FIFO的过程。当FPGA上电并完成初始化后(RESET=1′b1),系统从复位状态(RESET)进入空闲状态(IDLE),此时从FIFO的读写控制信号SLOE、SLRD和SLWR均为不操作时的高电平,主FIFO的写控制信号FIFO_WR为不操作时的低电平。当从FIFO中有数据需要读取时(FLAGB=1′b1),系统进入下传等待状态(DOWNLOAD_WAIT)并判断主FIFO是否允许写入数据。当主FIFO允许写入时(WR_READY=1′b1),系统进入下传状态(DOWNLOAD)。在该状态,FIFOADR被配置为选择EP2缓冲区,SLOE和SLRD变为低电平用于连续读取EP2中的数据,FIFO_WR变为高电平用于写数据到主FIFO。当从FIFO的数据读完后(FLAGB = 1′b0),系统返回到IDLE状态。

图4 Slave FIFO接口控制模块数据下传的状态机图

图5所示为Slave FIFO接口控制模块数据下传功能的仿真结果,其中左侧虚线以上为该模块的输入信号,虚线以下为输出信号。FDATA为USB微控制器输出到Slave FIFO接口控制模块的16位并行数据,FIFO_DATA是Slave FIFO接口控制模块输出到主FIFO的数据。时间段1到时间段4分别代表复位、空闲、下传等待和下传这4种状态。仿真结果与预期相符合,表明该设计是正确的。

图5 Slave FIFO接口控制模块数据下传的仿真结果

2.3 上位机控制软件设计

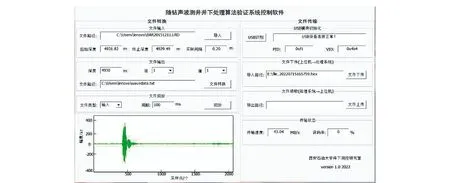

上位机是井下算法测试系统数据交换的控制中心,图6所示为该系统的上位机控制软件。该软件基于MFC框架开发,实现了文件转换和文件传输两个功能。

图6 井下算法测试系统的上位机控制软件

文件转换是将不同记录格式的测井数据转换为前端机能够识别和处理的文件[18]。该功能通过文件输入、输出和回放3个模块实现。文件输入模块导入原始测井数据并解析出数据对应的测井起止深度与采样间隔。文件输出模块转换出所需深度、接收站和通道的测井数据。文件回放模块可以快速查看上述2个模块中数据文件的质量,回放速度可以设置。

文件传输是在正确识别USB设备的基础上进行文件的下传与上传操作。该功能的开发利用了Cypress提供的CyAPI驱动程序库。USB设备的识别主要判断设备的初始化是否正常,并在软件中显示设备的PID号和VID号。文件下传是将上位机的测井数据传送到前端机的SRAM中,而文件上传与之相反。文件传输以512字节的数据包为基本单位,每包中的前511个字节为纯数据,最后1个为校验和字节。在数据传输过程中,上位机和FPGA均计算每包数据的校验和,统计校验和不一致的数据包个数用于计算误码率。文件传输完毕后,该软件显示平均传输速度和误码率。若有传输错误发生,则重新传输该文件。

3 测试与分析

本设计对基于USB微控制器的传输过程和数据交换接口的整体性能进行了测试。

3.1 USB传输过程的测试

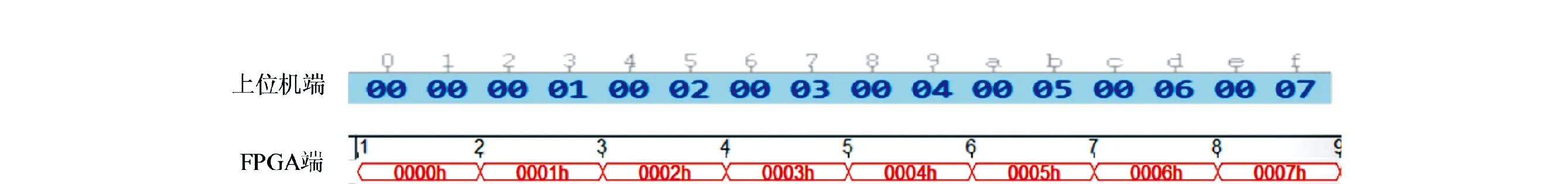

在上位机和FPGA之间互相收发已知数据,可以测试系统中USB传输过程的准确性和接口速度。图7所示为下传测试时上位机端发送和FPGA端接收到的数据。图的上部为上位机端发送数据包中的前16个字节数据,也即0x0000-0x0007这8个字数据,其中字数据的高字节在前,低字节在后。图的下部为FPGA中Slave FIFO接口控制模块接收数据包中的前8个字数据。可以看出,FPGA端接收到的数据与上位机端发送的数据一致,说明二者可以进行基于USB微控制器的通信。

图7 基于USB的下传测试数据

上位机连续发送512字节(含校验字节,每个字节占8位)的数据包时,利用示波器可以测试基于USB微控制器的数据包传输时序。图8所示为示波器测试结果,通道1到通道3分别是Slave FIFO接口控制模块的IFCLK、SLRD以及FLAGB信号,其中IFCLK是48 MHz的时钟信号。SLRD为低电平而FLAGB为高电平的时间段表示FPGA读取USB微控制器中从FIFO数据的过程,SLRD为高电平而FLAGB为低电平的时间段表示上位机往从FIFO中写数据的过程。从图可以看出,传输一个512字节的数据包耗时约为9.75 μs,计算可得本系统中USB接口的数据传输速度约为420.10 Mb/s。

图8 基于USB的数据包传输时序

3.2 数据交换接口的整体性能测试

本设计通过传输已知大小的数据文件来估算该数据交换接口的上传和下传速度,验证上位机软件中传输速度自动测试功能的可靠性。上位机下传1 GB的数据时,秒表记录的耗时为24.69 s,估算的下传速度为41.47 MB/s。前端机上传1 GB的数据通过连续64次读取SRAM中的全部数据并上传来实现。该过程的耗时为30.44 s,上传速度的估算值为33.64 MB/s。测试中,上位机软件测量的下传和上传速度分别为43.04 MB/s和34.78 MB/s。这与估算值接近,说明该数据交换接口的传输速度满足设计要求且上位机软件的传输速度测试功能正常。在此基础上,使用实际声波测井数据对该接口进行了整体测试。结果表明,该数据交换接口的上位机控制软件能够实现测井数据的格式转换,上位机和前端机SRAM之间能够进行双向快速传输,且传输速度和所需时间均与预期相符合。

4 结 论

本文在开发FPGA、USB微控制器和上位机软硬件的基础上,初步构建了一种随钻声波测井井下算法测试系统,设计了前端机SRAM与上位机之间的数据交换接口,实现了测井数据的格式转换、上位机和前端机的双向快速传输等功能,满足了井下处理算法测试系统的接口需求。

该数据交换接口能够完善随钻声波测井井下算法测试系统,提高开发井下实时处理算法的效率,有助于推动随钻声波测井地质导向技术的发展。