基于CPS 的微系统模块DDR3 信号PISI 分析

2023-12-04袁金焕王艳玲孙丽娟殷丽丽

袁金焕,王艳玲,孙丽娟,杨 巧,殷丽丽

(西安微电子技术研究所,陕西 西安 710065)

0 引言

现有DDR3 信号仿真方法,对简单2D 结构的PCB 板来说,板材及结构单一,已形成很多成熟的规范及仿真指导方法。QJ3103A-2011 印制电路板设计要求中对过孔及电流密度均有明确合格判定标准,在Mentor 公司Hyperlynx 和Ansys 公司的Siwave 软件中也有成熟的仿真流程。然而,微系统模块中采用新型材料以及复杂3D 堆叠结构的TSV 板、微模组、管壳。在一个封装内通过基板互连成为一个完整的复杂功能芯片[1],IC 裸芯片管脚数目、基板上集成的裸芯片和无源元件越来越多,基板层数、布线密度、传递的信号频率均迅速提升[2]。信号通路经过TSV 转接板的走线、TSV 孔、焊球、管壳基板的走线、过孔、焊球,到另一个硅转接板;模块应用时还需要对外引出到达PCB 板的走线、过孔和芯片;信号完整性仿真是一个发送芯片-信号通道-接收芯片的系统概念,微系统内分部件和PCB 板要协同进行PISI 仿真和优化;并需要分析3D 堆叠结构中提取S 参数方可达到仿真精度的方法以及电源直流和交流分析的合格判定标准等。目前微系统模块对PISI 均无成熟的分析方法及判定标准。

本文提出基于CPS 的微系统模块DDR3 信号电源完整性和信号完整性分析方法,能够进行3D 堆叠结构TSV 硅基板、管壳、微模组分部件的仿真建模、叠层设置、Solder Ball 参数设置;分部件电源PI 的DC 分析,并指出TSV 板和管壳合并集成分析的优点及判定依据;分部件结合PCB 板基于CPS 的AC 低阻抗PDN 的PI 分析;微系统中从发送芯片-信号通道-接收芯片全链路DDR3信号SI 分析。本案依据一款NOP 微系统和测试PCB 板进行详细分析说明。

1 NOP 微系统DDR3 的完整链路的PISI 仿真流程

微系统NOP 模块中,TSV 硅转接基板正面采用微凸点和裸芯片连接,背面采用相对较大尺寸凸点与封装管壳互连,正背面RDL 实现凸点的再分布,通过中间的TSV 结构实现正背面的导通,最终实现芯片与封装管壳的互连。DDR3 的完整链路包括:控制器690TSV 组件、管壳、DDR3 颗粒TSV5 层微模组件。其中DDR3 颗粒TSV5 层微模组件由5 只DDR3 芯片及1 只IPD 芯片构成,5 只DDR3 芯片采用RDL 二次布线后进行3D 同构堆叠,1 只IPD 芯片采用RDL 二次布线后与DDR3 芯片进行异构堆叠。IPD 芯片集成了DDR3 信号走线为Fly_by拓扑结构需在信号终点端接匹配的电阻和电容,降低信号反射,保证信号完整性。TSV 基板组件和管壳版图示意图见图1。

前仿真可以在Designer 中搭建电路,使用库中现有的传输线和阻容模型,分析:(1)控制器和DDR3 型号规格选择、驱动端的驱动能力和接收端的ODT 配置、匹配阻容值;(2)根据材料确定叠层信息、传输线阻抗、平面层回流路径;(3)拓扑结构,综合得出质量较好的信号波形后方可进入版图布局布线阶段。版图设计完成后进入PISI 后仿真阶段,PI 分析包括直流压降仿真(DC IR‐Drop)和电源阻抗仿真,SI 分析对DDR3 信号幅值和时序进行仿真。直流压降仿真优先于电源阻抗仿真和SI后仿真,如果依据直流压降仿真结果需对PCB 进行优化,版图更改后直流压降仿真通过后再进行电源阻抗仿真和SI 后仿真。对分部件进行PISI 分析,再进行CPS 协同的整条完整链路PISI 分析,有不通过的项目需要指导版图设计并再次仿真,直至PISI 分析过程中项目全部通过。微系统PI、SI 仿真流程如图2 所示。PI、SI 仿真时优先选用可实现3D 封装级分析的Ansys 公司的EM Suite 套件,包括SIwave、HFSS 3Dlayout、Designer[3]和Icepak[4]。

2 NOP 微系统仿真前叠层及焊球设置

根据叠层材料、焊球材料、工艺加工等设置叠层,包括层厚、材料电特性参数等。

2.1 控制器690TSV 基板叠层、焊球参数设置

根据图3 中TSV 基板结构示意图,设置控制器TSV基板的叠层仿真模型参数。

图3 TSV 基板叠层结构示意图

FMx是正面第x金属层(x=1、2、3);FPx是正面第x介质层(x=1、2);Oxide 是TSV 孔壁及正面硅衬底表面无机介质层SiO2(厚度3±0.5 μm);Oxide&PI 是背面硅衬底表面介质层(SiO2厚度0.5~1 μm、PI 厚度1~4 μm);BMx是背面第x金属层(x=1、2);BPx是背面第x介质层(x=1);Solder Ball 是凸点。依据厂商提供FPGA 裸芯片7VX690T 焊球直径、高度、材料,设置控制器TSV 基板的Solder Ball 凸点参数:TOP 层对应裸芯片690T 小球直径100 μm,高度70 μm;材料Sn90Sn10,电导率2.17×107S/m;TSV 的BOTTOM 层对应BGA 大球直径250 μm,高度180 μm;材料Sn63Pb37,电导率8.7×106S/m。TSV顶层和下层均需要粘接,材料是胶U8410-73c,顶层高度设置为裸芯片7VX690T 焊球高度,BOTTOM 层设置为BGA 大球高度。控制器TSV 基板叠层就可成功设置。需要注意的是,根据仿真测试误差[5-6],可进行材料参数拟合[7],在此把基板介质PI 的介电常数从3.5 调整为2.32。

2.2 DDR3 颗粒TSV 5 层微模组件叠层、焊球参数设置

DDR3 颗粒TSV 5 层微模组件是由5 层TSV 组合而成的,故叠层设置顺序根据实际应用情况TSV 是倒置并且组合进行设置,每层TSV 之间由胶U8410-73c 粘接,顶层和下层需要粘接胶,高度设置为实际粘接的焊球高度。Solder Ball 凸点根据裸芯片焊球直径、高度、材料设置;顶层IPD 芯片对应小球直径90 μm,高度70 μm;DDR3 裸芯片分别嵌入到5 层TSV 中,对应小球直径40 μm,高度10 μm;微模组最下层BGA 大球直径350 μm,高度260 μm;材料均为Sn63Pb37,电导率8.7×106S/m。

2.3 管壳设置参数

管壳考虑选用新一代高速率低温共烧陶瓷管壳(HITCE)陶瓷封装,能更好地满足高速通路要求。由于控制器690TSV 基板和DDR3 颗粒TSV 5 层微模组件的叠层中均已经设置了BOTTOM 层BGA 焊球、焊接到管壳后填充的材料胶的参数,故管壳叠层设置时就无需重复设置焊球及相关填充胶的参数,只需要设置中间介质层和金属层的参数。

3 电源PI 仿真

PI 仿真包含DC IRDrop 和AC 阻抗仿真两个方面。DC IRDrop 对电源从供电芯片VRM 到用电芯片的整个PDN 的直流电压损耗和电流密度、过孔电流进行分析,指导版图设计优化。阻抗仿真对整个PDN 的去耦网络进行优化,实现低阻抗PDN 设计。

3.1 DC IRdrop 压降仿真

由于微系统模块在三维方向堆叠的密度很大,过孔直径很小,故在硅基板和管壳阶段进行电源DC IRDrop分析不能只分析大电流而忽略小电流电源网络的仿真。

控制器TSV 基板、DDR3 颗粒TSV 5 层微模组件、管壳,分别需要进行DC IRDrop 仿真。如果仿真结果中有不通过的项目,定位原因进行版图更改,直至每一个组件都需要通过。然后,在仿真软件中,对控制器TSV 基板和管壳的工程文件进行合并,将DDR3 颗粒TSV 5 层微模组件和管壳的工程文件进行合并,对这两个工程进行直流DC IRDrop 压降仿真。

TSV 板和管壳按照分部件分别进行仿真的话,分部件处凸点、焊球的电压源作为pin-group 进行操作,电流源是平均分配到每一个管脚进行操作的;若TSV 板和管壳进行Attach 合并操作后,则作为一个整体模型,能够分析到凸点、焊球等中间路径瓶颈处的过流能力、压降、电流密度等关键参数,这样仿真模拟的电流路径通过情况和实际工作情况更贴近。如果芯片厂商提供有CPM,则优先使用CPM 映射的引脚配置电流。

直流电压损耗的标准:微系统内部PDN 直流压降建议不超过电源电压3%波动要求。电流密度标准:相同截面积的金属布线承载电流的大小,随着温度升高呈非线性增大,因此,散热越好,允许的温升越高,允许的电流密度就越大,这是电热综合的结果。根据电流密度结果、热仿真、样机测试运行结果以及近些年加工调试成功的多款微系统模块,总结出硅基板和管壳材质情况下,仿真电流密度经验最大值为800 A/mm2。总结出Si‐wave 软件中常用过孔的限定电流值,见表1。后期,根据工艺参数的实测数据积累对此值再进行修正。

表1 直流压降仿真过孔电流判定值

直流压降仿真超标时,可通过以下方式优化PCB 设计直至全部通过:增加PDN 电流通路瓶颈处的走线和电源平面宽度;增加承载电流过大过孔的孔径;在该过孔附近增加地孔;调整过孔分布位置,将承载电流较小的过孔调整到电流主路径位置,分担电流;增加电源地平面的铜厚等。

3.2 交流AC 仿真

电源阻抗仿真检验PDN 上有瞬态电流变化时,产生的电压变化是否超过芯片允许的电压变化量,即PDN 是否可以给芯片提供没有噪声的干净的电源[8]。若存在瞬态电压变化量过大,对PDN 的去耦网络进行优化仿真,指导PDN 设计。

判断进行交流AC 阻抗仿真的原则:此处TSV 基板无电容,进行谐振分析即可,限于体积限制可根据参数设置埋入电容消除谐振[9-10];管壳中安装了部分少量储能电容,故对管壳阶段可进行交流AC 阻抗仿真;进行AC 阻抗仿真分析的电源网络,根据实际并接的电容情况进行具体分析,通常微系统封装级及PCB 板级放置电容使得PDN 的阻抗在中频阶段低于目标阻抗,一旦超过这个由封装电感制约的最高频率,由芯片看过去的PDN 阻抗将由片上电容和封装内电容决定;微系统由于空间限制主要靠PCB 板进行去耦电容的配置,PCB 板去耦电容可采用例如Three per decade 方法,即按照10 倍数选择多种电容,同时阻抗曲线也能很好控制并联谐振峰[11],并且考虑封装寄生效应应距离微系统模块供电引脚就近放置;放置电容时还需要考虑用电芯片电流较大,稳压模块无法实时响应负载对于电流需求的快速变化,故在芯片焊盘四角处放置大容量储能电容从而防止电压出现跌落。

AC 阻抗仿真分析常用的是采用目标阻抗法[8]。然而目标阻抗随频率升高而增大,准确的目标阻抗曲线需要获取负载芯片在各频点的最大瞬态电流变化量,即电流需求的频谱,在具备CPM 时,可以直接进行PDN 时域CPS 协同仿真,检验是否存在电源噪声超标。将芯片、微系统封装和PCB 板进行CPS 协同进行PDN 设计,即分别提取PCB 板电源供电芯片端到微系统模块焊盘、TSV 板和管壳Attach Package 后的电源网络的模型S 参数,然后在仿真软件Designer 中搭建时域电路图,构建PDN 全链路,在模块端接入芯片CPM 模型,如图4 所示。采用去耦电容优化和时域仿真结合的方式,在不同数量和取值的电容下分析,获得电源纹波在限定范围以内的去耦网络设计。

图4 DDR3 的1V5 电源网络CPS 协同仿真全链路电路图

芯片端1V5 电源网络的时域波形如图5 所示,其中黑色虚线为采用CPM 模型精确优化微系统模块管壳的高频去耦电容,并协同优化PCB 中频去耦电容后的电压波形;黑色实线为未添加去耦电容网络时的电压波形。可见,芯片端电源纹波降低了33 mV,见图5 所示。

图5 CPS 协同分析的电源时域波形

4 SI 仿真

DDR3 总线的地址总线、时钟、数据总线和选通信号之间存在严格的时序要求,各信号又有详细的信号质量参数要求。DDR3 的数据DQ 信号、DM 信号和DQS 都是点对点的互连方式,可以通过驱动端调整驱动能力,接收端调整ODT 设置来进行阻抗匹配,从而实现波形的完整性;而地址信号、控制信号、时钟信号需要调整驱动端的驱动能力及Fly-by 拓扑结构远端处的匹配阻容值。选择布线结构和驱动器、DDR 器件时,可在前仿真阶段进行仿真,如果信号波形通过即可进行版图设计。采用星型结构遵照的原则是如果走线较短,信号上升沿较缓慢,信号反射较小,该星型拓扑结构因便于走线而优先采用;如果该星型拓扑结构反射较大且在仿真情况下也未找到合适的匹配电阻,此时需改成菊花链或Flyby 拓扑结构及其匹配方式消除反射[12]。

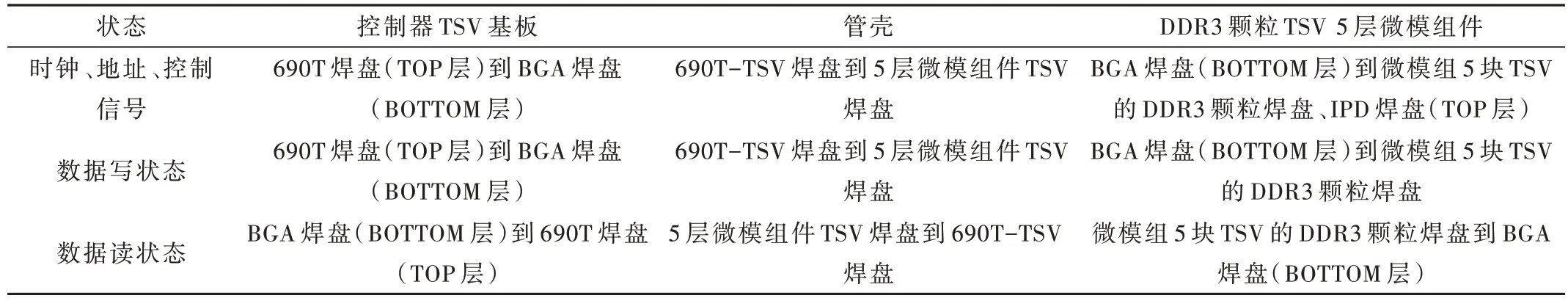

首先,将TSV 基板和管壳的版图设计导入到仿真软件中,进行板叠层、电容、电阻参数设置。其次,进行信号路径S 参数提取,因为版图涉及TSV 双孔设计,并且存在5 层TSV 堆叠结构组成的微模组,考虑到软件算法中对3D 版图结构计算准确性,此处优先选用专门用于封装的全波电磁场仿真HFSS 3DLayout[13-14]软件。由于HFSS 计算时间较长,故在提取S 参数时,信号分组进行,通常按照实际工作时序相互参考的信号作为一组进行提取,见表2。

表2 提取S 参数分类列表

此处比对了采用效率较高的SIwave 软件提取S 参数,信号时域波形相对于HFSS 有微小区别,分析原因是由于本案中焊球位于两端,而中间路径是TSV 过孔,结构工艺突变小,如图6 所示。

图6 TSV 微模组中一根地址信号Fly-by 型拓扑模型示例(左侧3D 互连图,右侧俯视平面图)

需要注意的是如果工艺采用图7 所示的SSD 控制组件结构、图8 所示的焊球互联或侧边互连的POP 结构,结构突变在走线中间位置且相对整段路径较长,如果采用SIwave 软件大概率会导致S 参数误差很大而不能运行出时域结果,此时只能使用HFSS 3DLayout 提取。根据2.5D 和3D 时域仿真与实测结果对比可知,3D 模型在仿真精度方面具有绝对的优势,基于仿真速度,2.5D 模型的仿真具有一定的参考价值[15]。

图7 SSD 控制组件示意图

图8 一种侧边互连的PoP 示意图

接着,采用AnsysEM Desktop 的circuit 软件Designer模块进行时域电路分析,根据信号读写状态时方向不同,导入提取路径的S 参数,搭建电路时按照信号从左到右的方向,对S 参数级联时的方向调整如表3 所示。

表3 S 参数级联时方向列表

仿真重点分析芯片不同驱动端口特性和拓扑端接匹配方式。通常来说,作为数据接收端,其ODT 方式包含ODT40、ODT60、ODT120 和ODToff,分别表示端接40 Ω、60 Ω、120 Ω 和无端接。作为发送端,其电特性包含iobuf34、iobuf40 和iobuf48 驱动状态。在目前的布线线宽、间距和硅基叠层尺寸及材料参数下,信号波形质量较好的设计为:驱动端芯片选用iobuf34;地址线和控制线拓扑最远端采用上拉到0.75 V 端接,匹配电阻取值范围40 Ω~80 Ω;时钟差分线拓扑最远端正负线分别串接60 Ω 电阻1 端,两个电阻的2 端短接后串接一个100 pF电容,再上拉到1.5 V。数据信号速率为1 600 Mb/s,写状态搭建电路如图9 所示,信号波形如图10 所示。

图9 数据写状态下搭建DQ0~DQ15 与相应DM、DQS 信号完整电路图

图10 写状态DQ0~DQ71 数据信号的接收端时域波形

查看DDR3 信号仿真结果,包括电平、边沿、时序、眼图等,并采用内嵌DDR3 脚本计算时序,依据标准判断时域和时序是否满足DDR3 信号判别JESD79-3F[16]标准中Electrical Characteristics and AC Timing 章节的要求,若不满足标准则指导版图优化后重新进行仿真,直至通过。

5 结论

本文提出对微系统中TSV 硅基板、管壳、堆叠TSV等分部件进行PISI 分析方法以及CPS 协同的设计方法。该方法能够在PI 仿真方面运用CPM 进行电源时域波形纹波分析,相对比传统的频域阻抗分析可以表达更加形象;在SI 分析方面能够进行全链路级联时域仿真。从NOP 微系统和PCB 板CPS 协同的分析结果来看,该方法效果显著。