测试回路杂散电感消除技术研究

2023-11-15袁丽娟荆茂盛胡奇威王洪洲

袁丽娟,荆茂盛,胡奇威,左 宁,王洪洲

( 中国电子科技集团公司第四十五研究所, 北京 100176)

近年来,随着物联网、车联网、太阳能电池板等新兴产业的兴起,半导体功率器件向提高开关速度、降低工作损耗、提高工作温度和增强可靠性等方向发展与创新,在很大程度上满足了社会各行业多样化的应用需求。高压半导体功率器件在划切、分选前的晶圆级电性能参数测试是保证封装产品良率的重要环节。全自动高压探针测试系统用于半导体功率器件晶圆级静态、动态参数测试不可或缺的前道检测设备。为了保证功率器件芯片在进入后道封装环节后最终产品的良率,探针测试系统需要提供可靠的测试平台以确保精准的电性能参数测试。相对复杂的结构导致运动平台以及测试回路的设计需要针对测试工艺进行多个方面的考虑。

1 典型的半导体功率器件

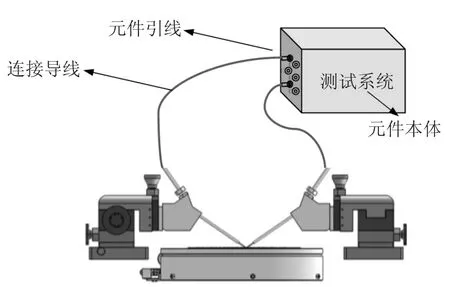

典型的半导体功率器件主要有MOSFET (金属氧化物半导体场效应晶体管)和IGBT(绝缘栅双极型晶体管)2 种。MOSFET 电性能测试示意如图1 所示。

图1 MOSFET 电性能探针测试示意图

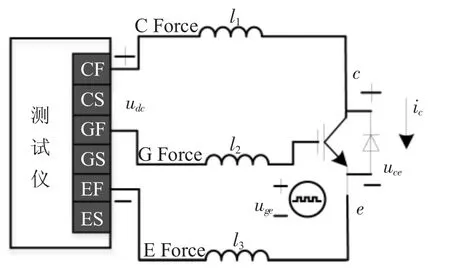

IGBT 集MOSFET 电压控制特性和BJT(双极结型晶体管)低导通电阻特性于一体,具有驱动简单、驱动功率小、输入阻抗大、导通电阻小、开关损耗低、工作频率高等特点,继承了MOSFET 较宽的安全工作区(Safe Operation Area,SOA)特性,是电力电子器件家族中最重要的成员之一,IGBT器件等效电路图如图2 所示。

图2 IGBT 器件等效电路图

IGBT 众多的优良性能,使其广泛应用于新能源汽车、轨道交通、光伏等行业。但是绝缘栅双极型晶体管(IGBT)的关断时间短,探针测试系统测试回路中的杂散电感在被测器件开通和关断的过程中将感应出较高的电压尖峰,大功率逆变器中IGBT 两端会出现较大的电压过冲,高电压应力可能超过半导体器件的承受能力,最终导致半导体器件的破坏,同时还会导致高频噪声以及辐射污染等问题。为此需采取一定的措施降低测试回路中的杂散电感,从而保护半导体器件免受损坏。

2 测试回路杂散电感分析

全自动高压探针测试系统主要由测试所需仪表、特殊性能的线缆、探针/ 探针卡、运动工作台、物料传输机构等构成,如图3 所示。

图3 全自动探针测试系统

以IGBT 测试器件为例说明测试回路中杂散电感的分布。图4 为对IGBT 器件进行电性能参数测试的示意图。

图4 电性能参数测试回路

IGBT 器件进行参数测试的等效电路图如图5 所示,图5 中DUT(device under test)为被测的IGBT 器件。其中C Force 为集电极激励线,C Sense 为集电极感应线;G Force 为栅极激励线,G Sense 为栅极感应线;E Force 为发射极激励线,E Sense 为发射极的感应线。在电性能参数测试中,C Force 和E Force 为整个回路提供了测试环境,电压可达几千伏,G Force 为双脉冲形式的栅极驱动电压。当G Force 上有正电压且大于开启电压时,整个回路导通,即相当于开关闭合。否则IGBT不导通,即相当于开关断开。

图5 参数测试的等效电路图

根据杂散电感的定义可知,连接导线、元件引线、元件本体等都会有杂散电感的存在,且对于整个测试回路来说,感应线阻抗极大、电流极小近似为0,故测试回路在考虑杂散电感对其的影响下可等效为图6。

图6 测试回路中杂散电感的主要分布

电感具有通直流阻交流的特性,故探针测试回路中存在一瞬态:

由式(1)可知,存在瞬态集射极两端的电压等于测试仪给定电压与回路中杂散电感产生的电压之和。集电极与发射极两端的电压会超过测试仪给定的电压,且由于开通和关断时间极小,杂散电感值较大时,集射极两端电压值较大,超过IGBT器件两端的耐受能力,对器件造成损坏。

3 叠层母排降低杂散电感的原理

开关器件与其它电气件的连接方式大致上可分为4 类。同轴电缆这种连接方式其互感较低且使用方便,但是其存在费用高、载流量低的缺点。铜板或铜条的平行排列连接方式可以在一定程度上抑制电压尖峰,但是互感仍然较大。电缆绞线使用方便而且便宜,但是自感和互感都较大,且载流量一般较小。叠层母排技术则兼备了经济性和实用性。测试回路连接分类如图7 所示。

图7 测试回路连接方式

叠层母排的主要结构是将排叠两层铜母排或多次铜母排,用绝缘材料将各层铜母排进行电气隔离,再通过一些工艺将导电层与绝缘层制作成整体。叠层母排截面呈现扁平状,使导电层面积在相同的电流截面下增大,也大幅增加了散热面,改善系统散热性能,提升了载流量;与此同时叠层母排降低了导电层之间的间隔距离,但由于叠层使输入输出线之间的分布电容加大,分布电容加大使输入输出线两端之间的耦合减小,起到去耦的效果,可以降低空间中的电磁干扰。由于流经叠层母排两侧的电流方向相反,且大部分相互叠加,一定程度上抵消了对外的磁场,有效地减小了线路上的寄生电感。根据麦克斯韦的电磁场理论,通电导线在周围空间产生磁场,电流越大磁场强度越强。在高速开关状态下,换流时会产生高频的大电流,而且根据集肤效应,高频电流主要分布在导体的表面。根据高频电流的镜像理论,层叠式电流路径能够抵消更多的磁场,回路中的寄生电感更小。叠层母排的结构如图8 所示。

图8 叠层母排结构

假设两层叠层母排基本参数:l 为母排长度,w 为宽度,h 为导电平板厚度,d 为两层导电平板中心间距。

导体的电感由外电感和内电感组成:

(1)内电感Li是由导体内部的磁链引起,其大小随频率的增加而减小;

(2)外电感Lo是由正、负母排的电流方向和拓扑结构决定,与频率无关。

在高频状态下,由于存在集肤效应,内电感Li很小可以忽略,电感主要表现为外电感Lo;而在低频状态下,Li是电感的重要成分,电感表现为Li与Lo之和。内电感Li的计算公式如式(2)所示:

外电感的计算公式如式(3)所示:

其中,μ0为真空磁导率;μr为相对磁导率;Δk和Δe为修正因子,由母排几何参数决定。如果d≪2h 并且d≪h+w,上式可以简化为:

如果h≪w,上式可进一步简化为:

综上所述,设计低电感的叠层母排时,有以下五条规律:

(1)层间距离d 与叠层母排寄生电感大小成正比;

(2)铜排厚度h 与叠层母排寄生电感成正比;

(3)非叠层区域越大,叠层母排寄生电感越大;

(4)端子越大,叠层母排寄生电感越大;

(5)上下叠层母排电流流向必须相反,即形成双向镜像回路,且换流回路包围的面积应尽量小。

叠层母排层间距离过小时,将会导致正负母排之间的绝缘性能降低;铜排设计比较薄端子截面积过小,会导致电流密度过大,温度过高。所以针对性的设计叠层母排需要综合考虑各方面的指标。

4 叠层母排在探针测试系统的应用

4.1 叠层母排在探针测试回路中应用分析

对于探针设备来说,叠层母排技术应用于同时测多个器件的探针卡与其它电气件的连接上。图9 为高压微腔室灭弧探针卡。

图9 高压探针卡

在图9 中可以看到,探针卡上存在多个尾部线缆,在探针测试项目系统中,探针卡主要用于同时测量多组开关器件的电性能参数,对于每个器件来说,都有3 个极,同时测量多个器件电性能参数时涉及多个回路,叠层母排技术的设计可将回路中的磁场抵消,从而降低杂散电感,满足系统的可靠性与安全性。叠层母排结构平面图如图10。

图10 叠层母排平面图

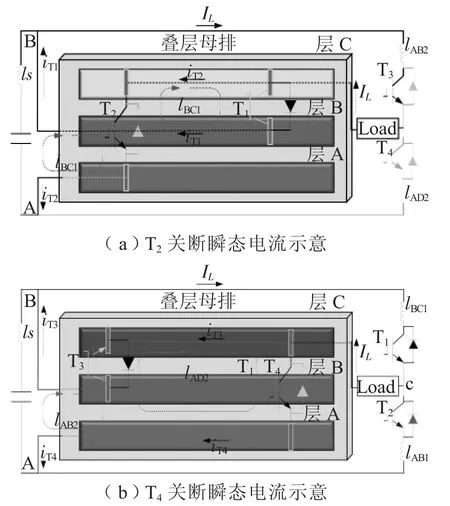

以探针卡同时测试晶圆上4 个IGBT 为例,叠层母排上为每个IGBT 留出3 个引脚,便于与IGBT 器件的连接。其叠层母排结构如图11 所示。

图11 叠层母排结构

叠层母排电流流向示意如图12,可知相近两排母线中电流方向相反,从一定程度上抵消了磁场,从而大大降低了线路中的杂散电感。其中图12(a)为IGBT T2关断瞬态电流示意,图12(b)为IGBT T4关断瞬态电流示意。

图12 高压电性能测试时叠层母排电流流向示意

4.2 叠层母排在探针测试系统中的应用

叠层母排在探针系统中的应用步骤主要为:仿真设计、仿真分析、优化迭代设计、实际测试。实际应用时探针卡固定在被测晶圆上方,探针卡上的线缆通过设计的叠层母排连接测试仪表。首先在Ansys 有限元仿真软件进行电磁场模型的有限元仿真。用Ansys 软件中的Q3D Extractor 能高效地对基于电气CAD 数据或三维Solidworks 模型数据的电子结构进行三维和二维电磁场仿真,通过设置电流的输入和输出位置及交流电流的频率、对导入结构指定材料属性,可对模型进行电磁性能分析。Ansys 可以提取寄生参数,并且计算任意载流结构的寄生参数。在Ansys 中对叠层母排进行建模如图13。

图13 叠层母排Q3D 模型

在Ansys Q3D 中设置叠层母排的材料,将母排和导电条材料设置为铜,将中间绝缘层的材料设置为环氧树脂(FR4 epoxy),设置仿真中注入交流电流的输入面(source)和输出面(sink),通过上述的参数选取和设置,软件即可提取出叠层母排的寄生参数。图13 所示母排结构仿真计算的寄生电感为14.235 μH。

根据叠层母排的优化原理对叠层母排的外形和结构进一步优化。图13 中正负母排的连接端子部分没有重叠,导致端子部分寄生电感较大。将寄生电感端子部分也设计为叠层结构,如图14 所示,其中图14(a)中的端子部分非重合面积较大,寄生电感值为9.348 nH;将端子部分的非重合部分减小,如图14(b)所示,寄生电感提取值为6.27 nH,寄生电感进一步减小。

图14 叠层母排模型

经过3 次仿真迭代优化设计的叠层母排结构杂散电感计算值如表1 所示。

表1 优化叠层母排结构前后杂散电感仿真值对比

将14(b)中的叠层母排结构应用在探针测试系统中,仿真后的C、E 极电压变化曲线如图15所示。

图15 C、E 极两端电压变化曲线

图15 中的纵坐标为C、E 极两端的电压,由图15 可知,在探针卡后加入叠层母排,集射极两端的电压较为平稳,电压尖峰较小。说明叠层母排的加入使得杂散电感值变小,进而保护了被测器件。

5 结束语

本文分析了探针测试系统测试回路中杂散电感对被测器件的影响,如果杂散电感值过大,会在电性能参数测试过程中增大被测器件两端的尖峰电压,一旦超过被测器件电压的承受能力,存在被测器件损坏的隐患。通过研究叠层母排结构降低杂散电感的原理,进一步分析了叠层母排技术在探针测试系统中的应用,并对叠层母排结构进行仿真分析,得到不同结构叠层母排的杂散电感值,最终在探针测试系统中对叠层母排结构降低杂感特性进行验证。

叠层母排技术的发展,使其广泛应用于军事设备系统、电动设备的功率转换模块、电力开关系统等领域。不可否认的是,叠层母排确实在一定程度上降低杂散电感,但是其并不能完全消除杂散电感。杂散电感的消除还需要依靠吸收电容与电感的相互作用,以此来达到杂散电感消除的目的。电容补偿可能会放大谐波,影响电容器以及线路中其它用电负载的正常运行,对于探针测试类设备来说,测试回路采用叠层母排结构配合吸收电容来降低和校准杂散电感带来的电气干扰会是一个新的研究方向。