2.4 GHz 频段射频前端高线性度SiGe 低噪声放大器设计

2023-11-14傅海鹏史昕宇

傅海鹏 ,史昕宇

(天津大学 微电子学院,天津 300072)

低噪声放大器要求在自身不引入较大噪声的同时,将接收到的微弱信号进行线性放大.作为接收机中的第一个放大器,LNA 的性能在很大程度上影响整个系统的噪声、线性度、灵敏度等指标.近年来,通信技术的发展和进步让视频会议、网络教学等各种应用场景得以实现,改变了人们的生活方式[1-3].为了适应不断扩大的接入设备数量,满足不断增长的数据吞吐量及速率需求,无线通信协议标准也在不断发展.其中,无线通信协议中诸如调制阶数的提升及系统灵敏度要求的提高对射频前端接收部分的线性度提出了更高的需求.这为LNA 的设计带来了新的挑战,LNA 需要具有更高的线性度、更低噪声、更高增益,以及更低的面积成本等[4].

为实现高线性度需求,文献[5]采用多栅晶体管(Multiple Gated Transistor,MGTR)结构,分别将主、从CMOS 晶体管偏置在饱和区和亚阈值区,实现对整体跨导二次导数的抵消,从而提升线性度.然而,该方案仅适用于CMOS 工艺.文献[6]采用堆叠晶体管的方法设计了一种堆叠三级的cascode 低噪声放大器.堆叠使得放大器可以使用更高的电源电压,从而获得更大的信号摆幅范围.功耗的提升也使得线性度得以提升.但这显著牺牲了功耗,不符合低功耗应用的发展趋势.文献[7]通过改进偏置电路提升线性度,但是其在大信号时,经电阻泄漏的射频电流会直接流入偏置电路中,偏置电路与放大器间镇流电阻的压降变化仍会带来低噪声放大器输入1 dB压缩点的前移,恶化放大器线性度.

从工艺考虑,虽然CMOS 工艺具有成本较低、易于集成等优势,但是噪声和线性度较差[8].而GaAs等Ⅲ/Ⅴ族工艺与之相反,性能优秀,但价格高昂且不易集成[9].与上述主流工艺对比,SiGe BiCMOS 工艺不仅具有CMOS 工艺易于集成的特点,还具有可与GaAs等Ⅲ/Ⅴ族工艺相比拟的性能和价格优势,是一种适合射频LNA 设计的具有高性价比的折中选择[10].

针对上述挑战并考虑工艺特点,本文采用SiGe BiCMOS 工艺,设计并实现了一款工作在2.4 GHz 频段的射频前端LNA.通过并联电容反馈技术在输入端同时实现增益和噪声匹配,并结合SiGe工艺特点,采用改进的动态偏置电路,克服镇流电阻压降影响,对泄漏的射频电流也加以利用,在不提升静态功耗的同时,实现线性度提升.为适应不同强度信号下的工作情况,该LNA 可在LNA 模式和旁路(Bypass)模式间切换.

1 电路设计

本文提出的全集成LNA 整体框图如图1 所示.整体电路由LNA、偏置电路、单刀双掷(Single Pole Double Throw,SPDT)收发开关及Bypass 支路构成.芯片整体通过单刀双掷开关选通发射、接收支路.LNA 接收部分在输入信号较小时,通过逻辑控制开关使电路工作在LNA模式,实现低噪声放大功能.在输入信号较大时,电路工作在Bypass模式,对信号进行旁路衰减,供后级电路处理.

图1 全集成LNA框图Fig.1 Block diagram of fully integrated LNA

1.1 开关设计

本文使用的单刀双掷开关如图2 所示.开关电路结构采用串并联结构,导通时开启串联支路,关闭并联支路,实现导通低插入损耗;关断时关闭串联支路,导通并联支路,实现关断高隔离度.由于发射、接收支路具有不同的功率容量需求,整体电路设计为非对称结构.当LNA_EN 为高电平,PA_EN 为低电平时,射频开关选通接收支路,M1管关断隔离发射支路,天线ANT 端口接收信号经过M2、M3管从RX 端输出至LNA主体放大;当LNA_EN为低电平,PA_EN为高电平时,M2、M3关断隔离接收支路,PA 发出的大功率信号由TX端口经过M1管从ANT端输出.

图2 单刀双掷开关原理图Fig.2 Schematic of single pole double throw switch

1.2 LNA及Bypass设计

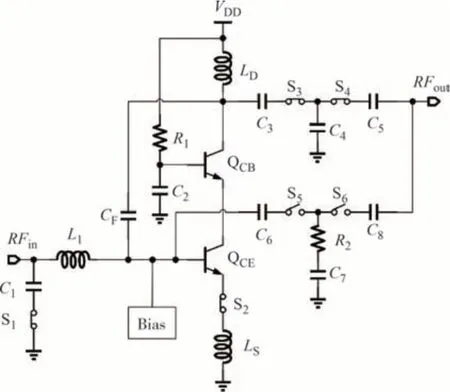

低噪声放大器在稳定的条件下,主要性能指标包含噪声系数、增益及线性度,良好的设计需要在三者之间权衡折中,一般噪声系数和增益的优先级较高[11-12].本文所设计的LNA 放大器部分如图3 所示,放大器主体由三极管QCE和QCB构成器件数较少的共射共基结构,减少晶体管噪声贡献并提高放大器增益.采用高Q值的金丝键合线电感LS组成发射极电感反馈结构保持放大器良好的稳定性,并参与输入阻抗实部匹配.

图3 低噪声放大器原理图Fig.3 Schematic of the proposed dual-mode low noise amplifier

考虑三极管在电流密度一定的条件下,其最小噪声系数将独立于晶体管大小.并且,共射共基极放大器的线性度与集电极工作电流IC正相关.因此,在功耗范围内采用大尺寸、低电流密度的三极管实现噪声与线性度的折中设计.尽管这将导致输入阻抗的实部低于50 Ω,使输入匹配复杂化,但采用额外的并联电容反馈CF和L1、C1构成的L 型匹配网络仍可以实现输入端噪声与增益的同时匹配.

具体如图4 所示,ZS为50 Ω 射频端口阻抗经过射频开关接收支路后在RX 端口体现的阻抗值.将L1、C1构成的L型匹配网络输入阻抗设计为射频开关输出阻抗ZS的共轭以实现最佳输入匹配,输出阻抗设计为共射共基放大器的最优信号源阻抗实现噪声匹配.并联反馈电容CF将由负载电感LD与电容C3、C4、C5构成的T型匹配网络共同组成的输出负载阻抗ZL引入输入端匹配,因此可以通过调整CF、ZL来使看向晶体管的输入阻抗ZT等于最佳噪源阻抗的共轭来实现增益匹配.由于引入的ZL不在输入端,不会对先前噪声匹配产生明显影响,至此,也就实现了晶体管输入阻抗不为50 Ω 时的输入端噪声与增益的同时匹配.且反馈电容CF的引入使得反馈增强,稳定性提高,可以减小对LS尺寸的需求,进一步优化噪声.

图4 输入匹配原理图Fig.4 Schematic of the input matching network

结合图3、图4,可以推导出具体的输入阻抗为:

其中,C1、L1分别为L 型输入匹配的电容、电感,ZL为负载电感LD与电容C3、C4、C5构成的T 型匹配网络共同组成的输出负载阻抗,CF为并联反馈电容,rBB为三极管小信号模型中的基极电阻,LS为发射极反馈电感,gm为三极管跨导,CBE为三极管基极与发射极间寄生电容.

当接收机接近信号源时,会接收到较大功率的信号,此时需要Bypass功能对大功率信号进行旁路,避免信号超出接收电路动态范围,保护低噪声放大器不被损坏.当工作在Bypass 模式时,开关S1、S2、S3、S4断开,切断LNA 通路.开关S5、S6打开,借由S5、S6开关的导通电阻与电阻R2和电容C7所在的支路一同构成T 型衰减结构,并可以通过电容C6、C8分别调节Bypass 模式下的输入、输出匹配特性,通过电容C7调整带内衰减平坦度,实现Bypass 模式的信号衰减功能.

1.3 线性度提升偏置电路设计

偏置电路为晶体管提供合适的静态工作点.传统的有源偏置电路常采用电流镜结构,如图5所示.

图5 传统电流镜有源偏置电路原理图Fig.5 Schematic of traditional active bias circuit using current mirror

晶体管集电极电流IC与基极-发射极之间电压VBE的关系可写为:

式中:VT为热电压;IS为饱和电流.

上式得出,当图5 中晶体管Q2与Q3具有相同VBE时,电流镜左右两边必然流过相同的电流.这就是电流镜的工作原理.假设LNA共射管QCE叠加射频信号后,式(5)可改写为如式(6)所示,其中VRF为输入射频信号幅度.经过泰勒展开后可得式(7).

由上式可以得出,射频信号的输入会给集电极电流IC引入额外的直流分量,且随着输入射频信号增大,IC的直流部分将迅速升高.这意味着,随着输入射频信号增大,升高的IC将使得基极电流几乎同步升高,在镇流电阻上产生更大的压降,迫使共射管QCE直流偏置电压降低,晶体管跨导下降,进而带来放大器增益的下降,使得放大器的1 dB 压缩点提前到来,影响LNA线性度表现.

因此,为提高LNA 的线性度,本文采用如图6 所示的动态偏置电路对LNA 进行偏置.IBias采用基准模块产生的恒定电流.将原本的镇流电阻R拆分为电阻R2、R3,则QCE基极电流增大在R3上产生的额外压降仅会使得Q2各极电位同步抬升,避免了上述传统结构中镇流电阻对LNA 线性度的影响.当LNA 工作在小信号情况时,该偏置电路为放大器晶体管提供稳定偏置.而当输入射频信号增大,使得LNA共射管QCE基极电压出现下降时,Q1基极电压将随之降低.同时,泄露的射频电流经C1流入R1,抬升Q1发射极电压,使得Q1集电极电流减小.此时,IBias中将有更多电流成为Q2的基极电流,并经过Q2的电流放大作用,产生更多电流流入QCE基极.最终,额外电流的注入将提高QCE偏置电压,延缓QCE跨导下降导致的放大器增益下降,实现动态偏置效果,提高LNA线性度.

图6 动态偏置电路原理图Fig.6 Schematic of dynamic bias circuit

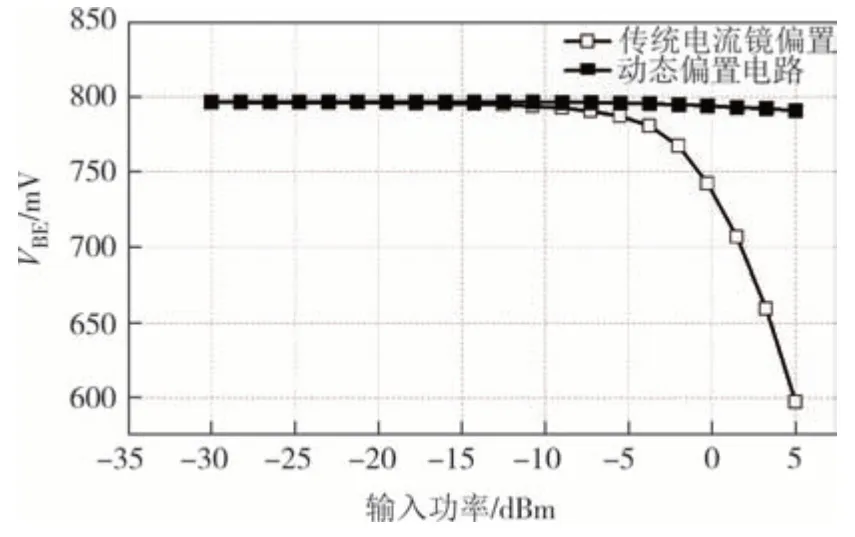

仿真得到在使用上述两种偏置电路时,QCE晶体管基极-发射极电压VBE随输入功率变化的关系如图7 所示.从图7 可对比得出,使用传统电流镜偏置的晶体管VBE在输入功率高于-10 dBm 后出现快速下降,并在输入功率达到+5 dBm 时,已下降约200 mV.而同等条件下,采用动态偏置电路结构进行偏置的晶体管VBE仅下降10 mV.以上结果表明,动态偏置电路可以更好地稳定放大器的静态工作点,减弱输入功率升高时,晶体管跨导变化导致的增益下降,改善电路的线性度.

图7 电路使用传统电流镜偏置与动态偏置的VBE随输入功率变化Fig.7 VBE versus input power for circuit using conventional current mirror bias and dynamic bias

2 仿真及测试结果对比分析

本节介绍芯片的仿真与测试结果.芯片的显微镜照片如图8所示.芯片面积为1.23 mm×0.91 mm.测试时,芯片的所有pad均由金丝键合线连接至片外测试板.测试板照片如图9 所示.测试板使用4350板材.

图8 芯片显微镜照片Fig.8 Microscope photo of the chip

图9 测试板照片Fig.9 Photo of the test board

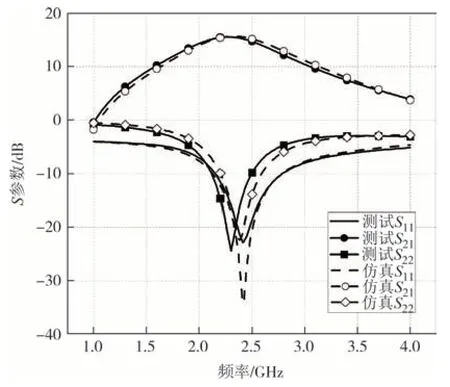

S参数的仿真与测试结果对比如图10 所示.仿真结果表明,在2.4~2.5 GHz 内,LNA 的S21为15.1~15.5 dB,S11<-20 dB,S22<-13.8 dB.测试结果表明,在相应频带内,S21为14.6~15.2 dB,S11<-18 dB,S22<-9.8 dB.S参数的测试结果与仿真结果一致性较高.

图10 S参数仿真与测试结果Fig.10 Simulation and test results of S-parameters

噪声系数的仿真与测试结果对比如图11 所示.在2.4~2.5 GHz 内,仿真噪声系数<1.85 dB,实测噪声系数在1.9~2.06 dB 内.噪声系数的仿真与实测结果相差接近0.2 dB,主要为测试板射频走线及接头损耗所致,可以认为仿真与测试结果一致.

图11 噪声系数仿真与测试结果Fig.11 Simulation and test results of noise figure

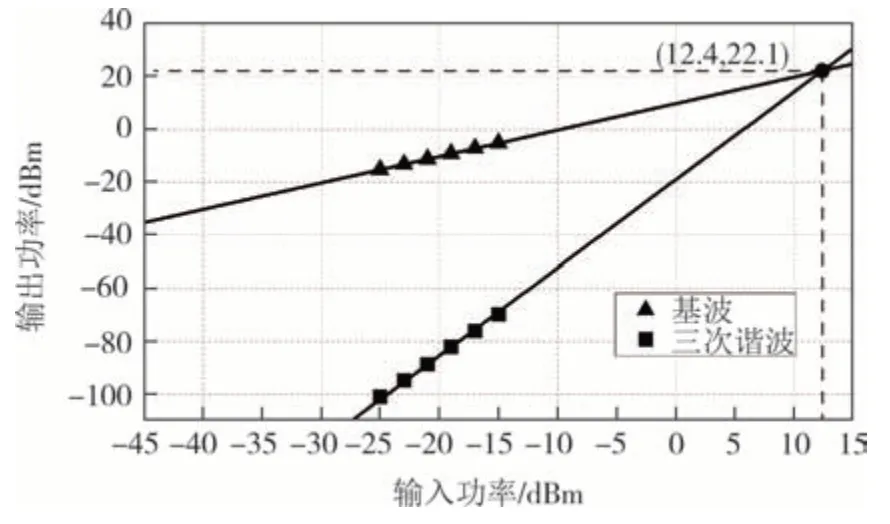

图12及图13展示了LNA线性度测试结果.测试结果表明,该LNA 在中心频点2.45 GHz 处输入1 dB压缩点接近-2.7 dBm,其输入三阶交调点超过+12 dBm.LNA实现了较优的线性度表现.

图13 输入三阶交调点测试结果Fig.13 Test results of input-referred third-order intercept point

表1 展示了本设计与近年其他低噪声放大器的性能比较结果.从对比结果可以看出,本文所设计的低噪声放大器各项性能指标较为均衡,增益较高,噪声系数相对较小,且本设计的输入三阶交调点指标较为突出,该低噪声放大器具有较为优秀的线性度水平.

表1 低噪声放大器性能总结Tab.1 Summary of the low noise amplifier performance

3 结论

本文提出了一款基于SiGe工艺的高线性度低噪声放大器.设计采用电容反馈结构和L 型输入匹配实现放大器增益与噪声的同时匹配优化,并采用改进的动态偏置电路提升LNA 的线性度表现.实测结果表明,在2.4~2.5 GHz 的工作频带内,电路增益为14.6~15.2 dB,噪声系数在2.1 dB 以内,输入输出匹配良好,且整体仿真结果与加工实测结果表现出较好的一致性.线性度测试结果表明该LNA 在中心频点2.45 GHz 处输入1 dB 压缩点接近-2.7 dBm,电路输入三阶交调点达到了+12 dBm,所设计的低噪声放大器具有较高的线性度.