基于UVM的报文验收滤波模块验证方法

2023-10-22史雷萌左石凯黄新栋叶圣哲

史雷萌,左石凯,黄新栋,吕 鑫,周 犇,叶圣哲

(厦门理工学院光电与通信工程学院,福建 厦门 361024)

早期的集成电路(integrated circuit,IC)芯片开发工作复杂度较低,采用Verilog语言编写测试激励的方式能够满足大部分验证需求。随着IC 芯片电路规模的增大,为了确保待验证模块功能的正确性,需要使用更多激励进行测试,导致构建Verilog 验证平台耗时增加。同时,覆盖率要求确保待测模块所有可能情况都被测试,但使用Verilog 验证平台收集会花费大量的时间和精力,故验证覆盖率的收集较为困难[1]。为了解决上述问题,学者们提出不同的解决方法:杨金鑫[2]使用Verilog语言验证系统级芯片内的控制器模块时,利用脚本文件语句定向约束参考模型的方式验证被测设备,该方法虽然能够增加验证激励,但并未对覆盖率指标进行收集,导致验证项的遗漏。王凯等[3]通过Systemverilog 语言验证图像采集芯片的功能,并划分验证环境结构,同时遵循面向对象的思想搭建验证平台,虽然验证平台的搭建速度增快,但平台结构繁琐且重用性不高,无法提高验证的效率。为此,本文提出一种基于通用验证方法学(universal verification methodology,UVM)的报文验收滤波模块验证方法,使用Python 脚本语言自动化搭建UVM 验证平台以加快平台搭建的速度,并采用可约束的随机化测试技术,利用随机时间种子产生不同的测试激励,提高测试的覆盖率。

1 报文验收滤波模块工作原理

报文验收滤波(acceptance filter,AF)模块是控制器局域网(controller area network,CAN)总线上处理报文数据的模块,由CAN 规范ISO11898-1[4]可知,当接收报文的识别位和预设定位值相同时,模块即接收此帧信息[5]。AF模块根据CAN规范分为基础(basic)模式和扩展(peli)模式[6],且在peli 模式中,根据滤波器的个数分为单滤波模式(single mode)和双滤波模式(dual mode)。

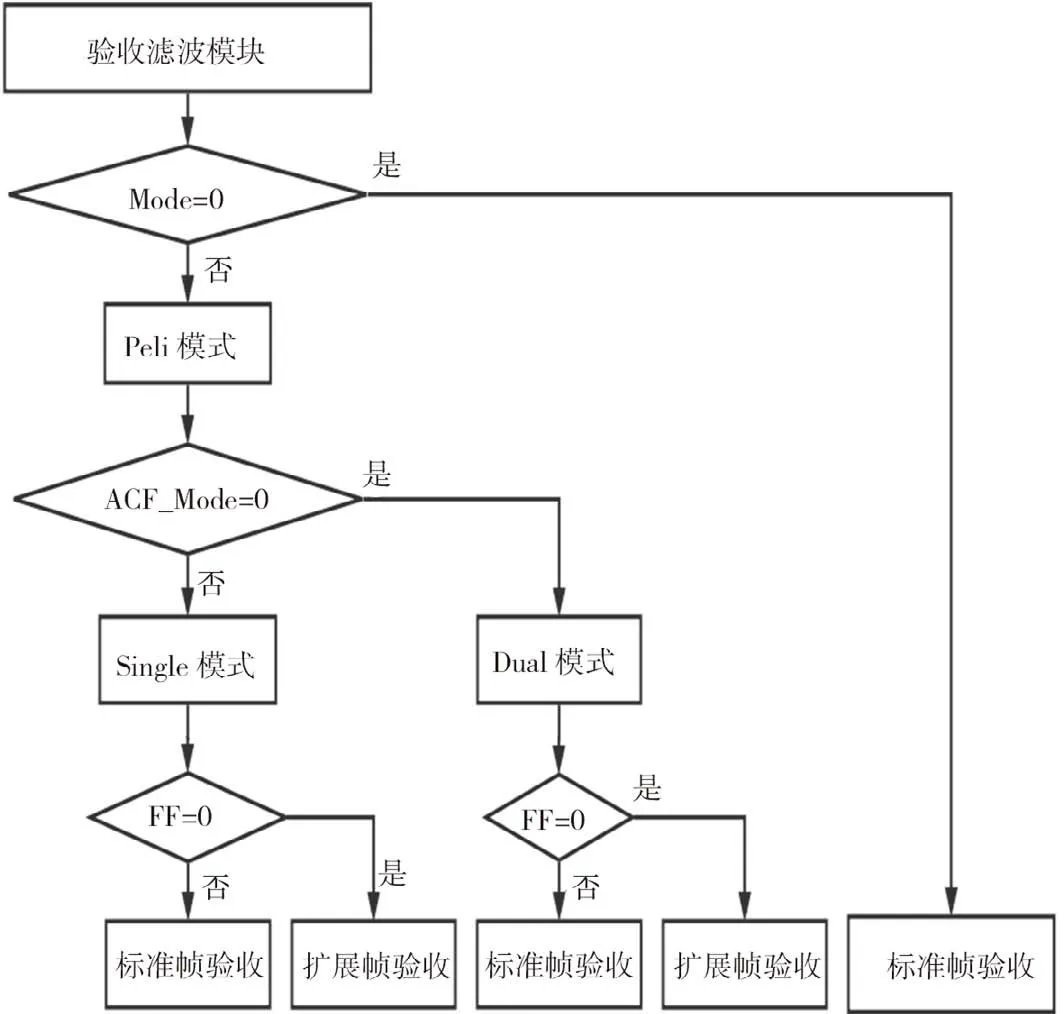

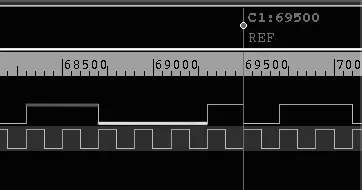

本文需验证的报文验收滤波模块由4个验收代码寄存器(acceptance code register,ACR)与4 个验收掩码寄存器(acceptance mask register,AMR)组成,且支持基础和扩展2 种工作模式。模块接收到总线上的报文后,通过Mode信号进入对应工作模式,ACF_Mode 信号选择不同滤波模式滤波验收报文。报文滤波验收模块运行流程图如图1所示。运行过程中,首先,平台通过Mode 信号高低电平判断模块进入何种模式,若Mode 信号为0,进入basic模式验收标准帧报文;若Mode信号为1,则进入Peli 模式。其次,判断ACF_Mode 信号的高低电平状态。若ACF_Mode 信号为0,进入dual 模式;若ACF_Mode 信号为1,进入single 模式。最后,判断报文的种类。对标准帧和扩展帧报文采取不同的模式进行滤波验收,并输出ACF_Pass_o 信号的高低电平状态作为滤波验收模块的结果。模块验收滤波结果波形示意图如图2 所示。图2 中:红色线段为高电平,表示通过验收;黄色线段为低电平,表示不通过验收。

图1 报文滤波验收模块运行流程图Fig.1 Workflow of message filtering acceptance module

图2 模块验收滤波结果波形示意图Fig.2 Waveform of module acceptance filtering results

2 UVM验证方法设计

2.1 UVM验证平台构建

UVM 验证方法学引入类作为基础单元,集成标准化模块语句规范仿真流程。利用脚本语言帮助验证人员快速构建验证平台,缩短待测设备(DUT)移植时间[7-9]。

本文利用Python 脚本语言的mako 库模板语句,自动化搭建UVM 验证平台[10-12]。将UVM 验证平台需要高重用度的部分提取出来,使用${agent_name}关键字动态替换。当脚本运行时,关键字通过render函数进行替换。脚本运行完毕后,在目录文件夹下生成验证平台代码。

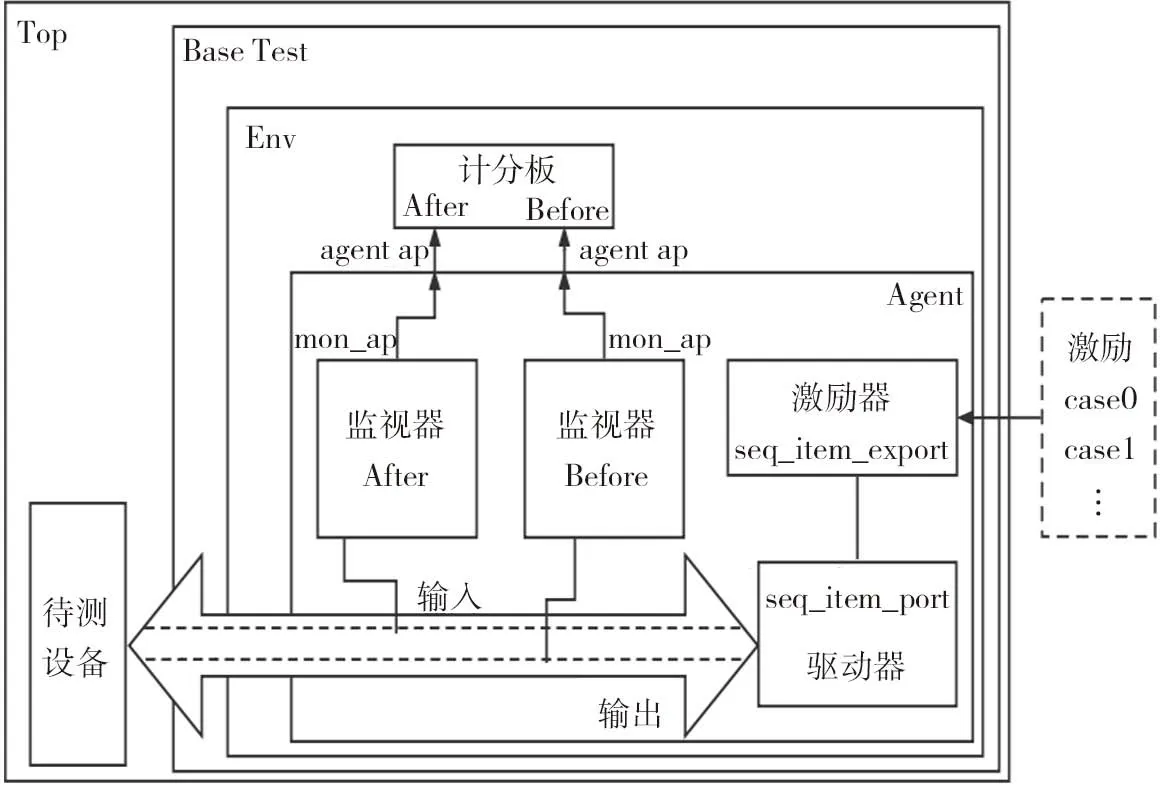

UVM 验证平台的结构示意图如图3 所示。顶层(Top)组件包括需要验证的DUT 和基础测试(BaseTest)组件。基础测试组件内包括环境(Env)组件、代理(Agent)组件和计分板组件。代理组件是验证的主要模块,其中包含封装监视器(monitor)、激励器(sequencer)和驱动器(driver)组件。为了加强组件之间的耦合性,通过接口(interface)组件连接DUT 和驱动器组件,并使用phase 机制管理任务执行顺序和时间,确保测试环境的正确运行。

图3 UVM验证平台结构示意图Fig.3 UVM validation platform

验证DUT 的激励由事务组件产生,在激励器和驱动器之间通过seq_item_export 和seq_item_port 端口交换数据。当激励产生事务之后由激励器同意传递给驱动器进行驱动。

本文创建监视器After 和监视器Before 组件收集驱动器得到的激励数据,提高代理组件的利用率,增强验证平台代码耦合的能力。监视器After 组件收集驱动器的输入数据,将收集的输入数据施加到参考模型组件中,得到参考模型运算的结果。其结果使用事务级建模通信机制经过mon_ap 端口传递给计分板。监视器Before组件则收集驱动器的输出数据,通过mon_ap端口直接传递给计分板。

计分板对比上文2个端口传递的数据,由于监视器Before需通过DUT产生数据结果,在计分板接收数据时会落后一个时钟周期,因此代码中存在2 个循环来收集监视器After 和监视器Before 的数据。通过UVM的域自动化(field_automation)机制,计分板对数据进行比较,数据相同则是成功,不相同则是失败。

2.2 验证激励规划

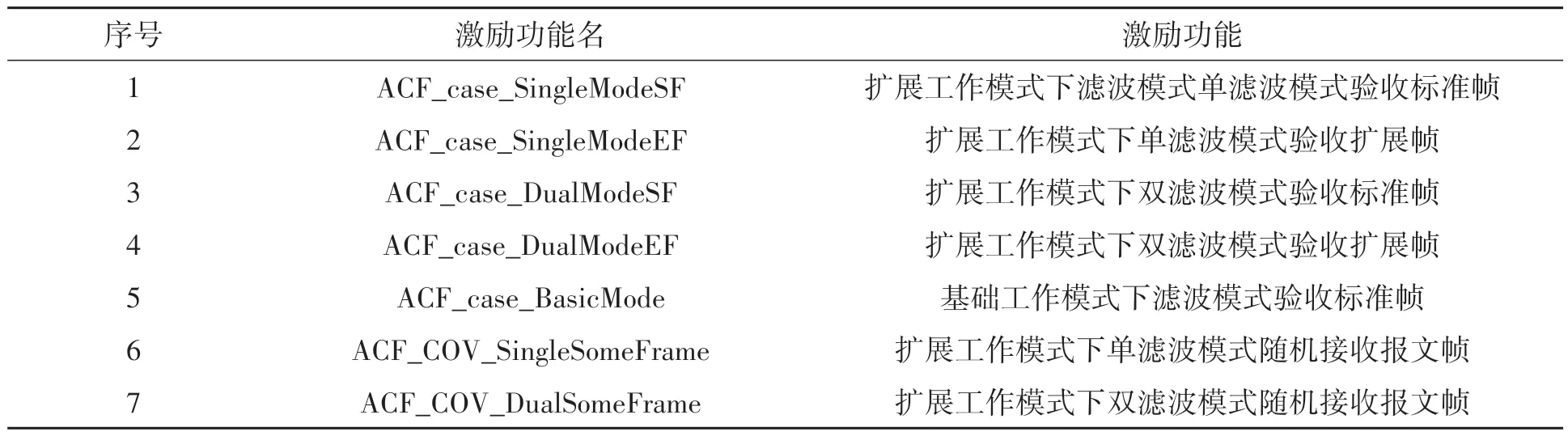

模块功能的正确与否是决定验证工作成功的关键,因此需要了解模块工作原理,依照工作原理规划验证激励。本文遵循第1节所述原理,针对滤波验收模块工作模式、滤波模式及帧种类的差异编写验证激励条目,如表1所示。

表1 验证激励条目Table 1 Incentives to validate

使用VCS 编译工具仿真验证激励时,通过default_sequence 宏定义启动不同验证激励文件。即在编译命令的关键字UVM_TESTNAME 后输入表1 中对应的激励功能名。验证激励运行后,由starting_phase 提起进程(raise_objection)。根据事务组件注入随机事件种子,产生随机数据。多次迭代后,再由starting_phase 结束进程(drop_objection)。通过随机事件种子约束数据,运行不同激励,逐渐提高验证的完备性。

2.3 覆盖率收集策略

收集验证激励的覆盖率是检测待测模块功能是否完备的手段。本文根据2.2规划的验证激励,通过更新随机事件种子的值并运行仿真,收集验证激励的覆盖率。反复迭代此操作,直到达到验证目标为止。

覆盖率类型包括代码覆盖率和功能覆盖率。代码覆盖率统计待测模块的代码执行情况,包括行覆盖率、分支覆盖率和表达式覆盖率。功能覆盖率统计待测模块的功能测试情况,通过功能覆盖组中存在的功能覆盖点数量来计算功能覆盖率。功能覆盖点包含事务组件的数据属性,包括帧类型、帧标识符等信号。仿真时,在同一时刻采样信号并收集覆盖率。

本文在VCS 仿真软件的编译命令中执行-cm 语句进行覆盖率收集,编译仿真结束后,使用dvefull64 -covdir *.vdb &命令通过DVE 图形工具查看覆盖率,并生成html 网页记录。此外,待测模块中的MaskData0、MaskData1这2信号持续为低电平,无须收集覆盖率,故编写屏蔽文件取消收集。在每个激励运行结束后,覆盖率统计信息会存入指定的文件夹内,当所有激励验证完毕后,通过merge命令合并覆盖率结果。

2.4 平台搭建速度指标

利用字节统计命令wc -c *.sv 能够收集验证平台的代码数据量,统计基于Verilog 语言的验证平台和UVM验证平台的代码量数据,并进行验证平台搭建速度分析。

3 仿真结果及分析

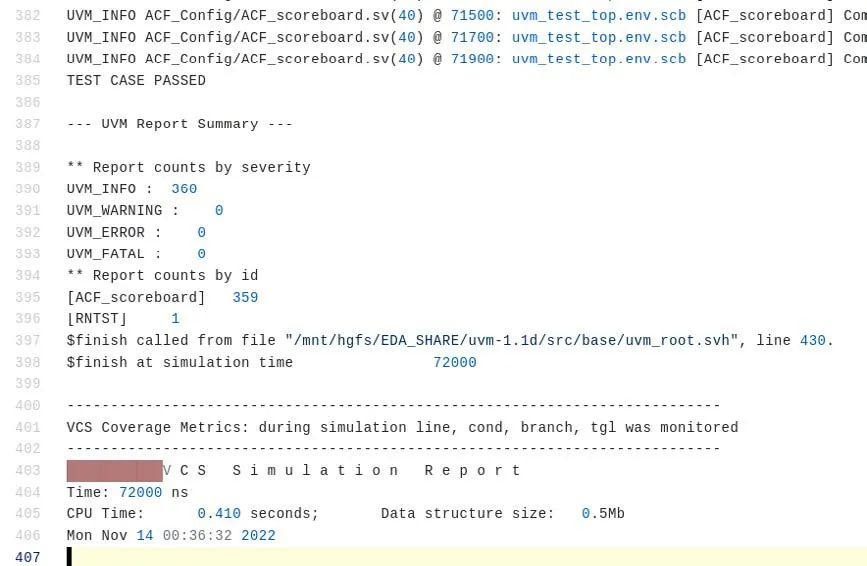

使用不同值的随机事件种子进行多次重复仿真,直到覆盖率数值趋于稳定。图4 为仿真输出的log文件示意图。

图4 仿真输出log文件示意图Fig.4 Simulation output log file

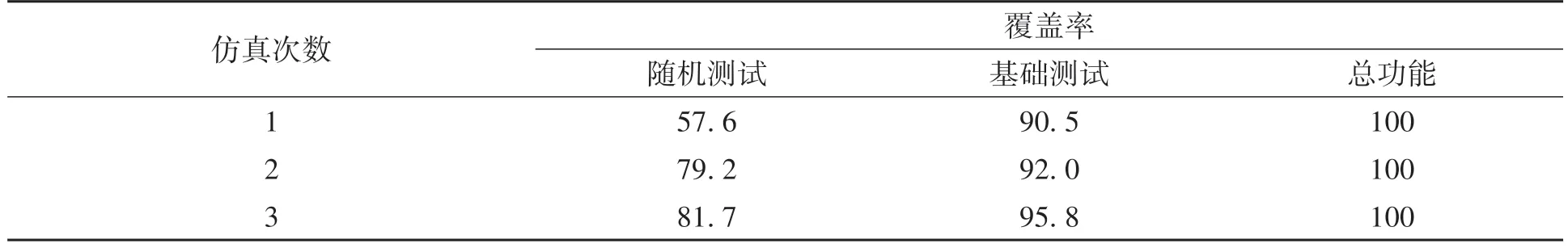

编译时更改随机事件种子值并多次仿真、收集代码覆盖率和功能覆盖率结果。表2为多次功能覆盖率收集的结果,由表2可见,功能覆盖率达到100%,覆盖率收集结果均符合预期。

表2 功能覆盖率收集结果Table 2 Functional coverage data collected 单位:%

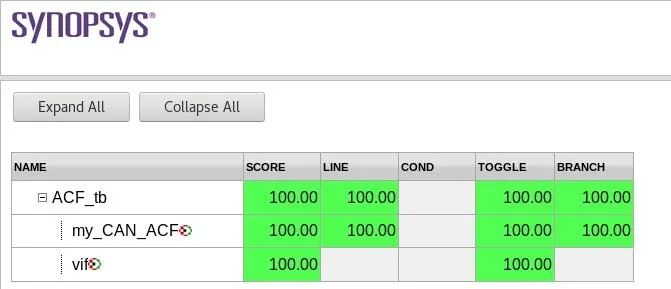

仿真过程中,其中一次仿真的代码覆盖率为97.22%,行覆盖率97.26%,分支覆盖率98.3%,表达式覆盖率94.2%。多次仿真后,逐渐提升至100%。如图5 所示,代码覆盖率收集了待测模块的覆盖率程度,表明对滤波验收模块已完成验证。同时,使用字节统计命令分别对Verilog验证平台和UVM 验证平台进行代码数据量统计发现,基于Verilog 语言的验证平台代码数据量为806 114 B,而使用UVM验证方法搭建的验证平台代码数据量为46 514 B,后者减少94%的代码数据量,能够缩短验证平台构建时间。

图5 代码覆盖率统计报告示意图Fig.5 Statistics of the code coverage

4 结论

针对Verilog 验证平台搭建速度慢、验证覆盖率收集困难的问题,本文提出一种基于UVM 的报文验收滤波模块验证方法。该方法采用Python 脚本语言自动生成UVM 验证平台,在验证平台中使用接口组件整合模块信号端口,并采用可约束的随机化测试技术,利用随机时间种子产生不同的测试激励。同时对验证模块输出数据进行监控,收集测试的覆盖率。仿真结果表明,相比Verilog 搭建的验证平台,本文提出的验证平台能够减少94%的代码数据量,缩短验证平台构建时间,且收集模块的覆盖率为100%。