嵌入式电容器与储能用聚合物/陶瓷介电复合材料的研究进展

2023-10-09简刚,封亮

简 刚,封 亮

(1.中国科学院深圳先进技术研究院 深圳先进电子材料国际创新研究院,深圳 518055)(2.江苏科技大学 材料科学与工程学院,镇江 212100)

随着全球变暖和化石燃料逐渐枯竭等一系列问题的出现,可再生资源的开发已成为全球优先考虑的问题.目前大多数新能源,如风能、太阳能等都由于其间歇性的特性,严重依赖于储能单元[1-3].并且随着电子信息技术的快速发展,电子产品的小型化、轻量化已成为微电子行业不可逆转的趋势.然而,目前的电子产品中,分散式有源器件占据了电路板上90%的区域,其中主要是电容器,这严重阻碍了微电子行业微型化的发展.因而,嵌入式微电容技术的开发与应用吸引了国内外科学家的注意.嵌入式电容器占用面积小,它的使用将大大提高印刷电路板的封装密度,使电子设备微型化成为可能.但是,嵌入式微电容技术对电介质材料有很高的要求,即材料需同时满足介电性能、可靠性及加工性的要求.

传统的电介质材料包括陶瓷和聚合物,但二者各有其优劣势.陶瓷是发现和使用最早的介电材料,常见的陶瓷电介质有氧化钛(TiO2)、钛酸钡(BT)、钛酸锶(SrTiO3)和锆钛酸铅(PZT)等等,其介电常数很高[4],热稳定性良好[5];但缺点是击穿场强小[6-7],密度高脆性大和需要高温烧结成型,无法满足现代电子产品的工艺要求.聚合物常见的包括聚二甲基硅氧烷(PDMS)聚丙烯(PP)、聚乙烯(PE)和聚偏氟乙烯(PVDF)等,具有较高的击穿强度、易于加工,价格低廉以及机械性能好等优点,是作为嵌入式器件材料的最佳选择;但聚合物介电常数较低,导致其介电性能和储能密度不高.

在单一材料无法满足应用需求时,研究者们开始将二者复合,研发了1+1>2复合效应的聚合物/陶瓷介电复合材料,即将具有高介电常数的陶瓷填料加入到聚合物基体中,这种复合材料相对来说比较容易制备.同时由于聚合物和介电陶瓷本身就是介电材料,所以复合材料在具有能量传递速度快、服务时间长、良好的灵活性、高介电常数的同时还具有相对较低的介电损耗,从而实现了高储能密度可以应用于较为广泛的领域,在近些年来备受关注[8-12].根据Lichtenecker 对数方程,复合材料中随着填料体积分数的增大,填料相和基体相之间的界面面积增大,进而使界面极化增大,复合材料的介电常数随之增大.在陶瓷介电填料填充的聚合物基复合材料中,要获得更高的介电常数,需要高的填充分数,一般认为介电陶瓷填料的体积分数高于60%时才能显著提高复合材料的介电常数,并且要求填料在聚合物基体中要有良好的分散性.但是,随着陶瓷填料体积分数的增加,会有一系列的问题出现,比如高的填充会导致复合材料的脆性增大,机械性能降低.此时,导致复合材料的介电常数和击穿强度变低的同时介电损耗增大.除了填料的种类,填料的微观形貌、在聚合物机体中的分散方式、表面处理和制备方法等,也对聚合物/陶瓷复合介电材料的介电性能有显著影响.

总的来说,尽管聚合物/陶瓷复合材料在嵌入式电容器中的应用已经做了大量研究,但在开发高介电常数、高击穿强度、高储能密度和低介电损耗的复合材料方面仍存在很大的问题和挑战.对于线性介质,能量密度(U)表示为U=1/2ε0εrEb2[13],其中ε0、εr和Eb分别表示真空介电常数、相对介电常数和击穿强度.对于介电常数随电场变化的非线性电介质,能量密度由U=ʃEdD得到[14],其中E是电场,D是电位移.显然,介电常数和击穿强度对于获得高能量密度都是至关重要的.文中结合本课题组的研究结果对高储能密度低损耗的聚合物/陶瓷复合材料,包括高介电常数、高击穿强度以及高温应用的研究进展进行了总结和分析.

1 聚合物/陶瓷复合材料介电常数的影响因素

1.1 陶瓷和聚合物的介电常数对复合材料介电常数的影响

陶瓷和聚合物各自的介电常数会影响到聚合物/陶瓷复合材料最终的介电常数.所以,选取具有高介电常数的聚合物基体和陶瓷填料是提高复合材料介电常数的一个很好的途径[15].在目前的研究中,聚合物基体中PVDF因较高的介电常数和击穿强度而被广泛应用;陶瓷填料中被广泛应用的包括BaTiO3(BT)、钛酸铜钙(CCTO)等.

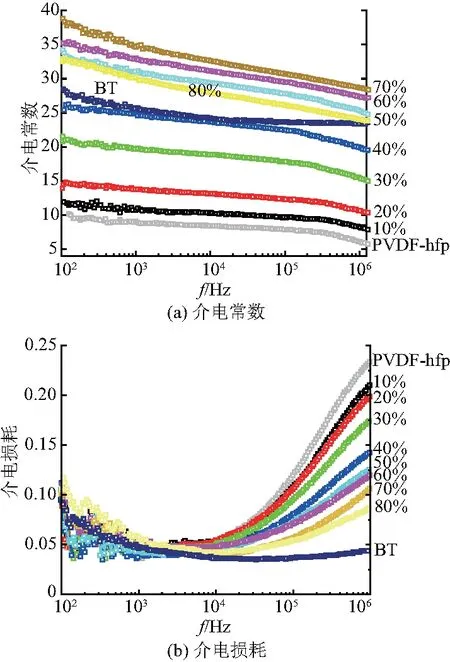

文献[16]将分散性良好和平均直径为6.9 nm的BT纳米粒子填充到PVDF-HFP中制备成了PVDF-HFP/BT复合材料,其介电性能如图1.在PVDF-HFP基体中引入BT纳米粒子填料,不仅可以提高纳米复合材料的介电常数,实现高的电位移,还可以降低纳米复合材料的介电损耗,使其更适合于快速充放电循环应用.

图1 PVDF-HFP/BT复合材料的介电常数和介电损耗

CCTO是一种巨介电常数的陶瓷填料,与常用的铁电材料不同,这种非铁电材料的介电常数在较高的频率和较宽的温度范围内高达104~105[17].文献[18]研究了P(VDF-TrFE)/CCTO复合材料的介电性能,如图2.显然,复合材料的介电常数随着CCTO含量的增加而增加.例如,当 CCTO的体积分数为50%时,复合材料在1kHz下的介电常数超过150,约为纯P(VDF-CTFE)共聚物的18倍.

图2 P(VDF-TrFE)/CCTO复合材料的介电常数

因此,在聚合物/陶瓷复合材料中,陶瓷和聚合物的介电常数都会影响到最终复合材料的介电常数.

1.2 陶瓷填料的形貌对复合材料介电常数的影响

近年来的研究表明,填料的微观形貌对提高复合材料的介电性能起着至关重要的作用.文献[19]将零维(0D)钛酸钡球形颗粒(BT NPs)作为陶瓷填料,制备了环氧树脂/钛酸钡复合材料,其介电特性如图3.结果表明,环氧树脂/钛酸钡复合材料的介电常数随钛酸钡粉末体积分数的增加而增大,比纯环氧树脂的介电常数(4.6)有了显著的提升,并且填料的微观尺寸对复合材料的介电性能也有一定的影响.但随着粉末添加量的增加,其体积百分数在50~60左右达到最大值,然后逐渐降低.这种减少可能是由于过量粉末添加所引入的孔隙或空隙所致.

图3 环氧树脂/BT复合材料的介电常数

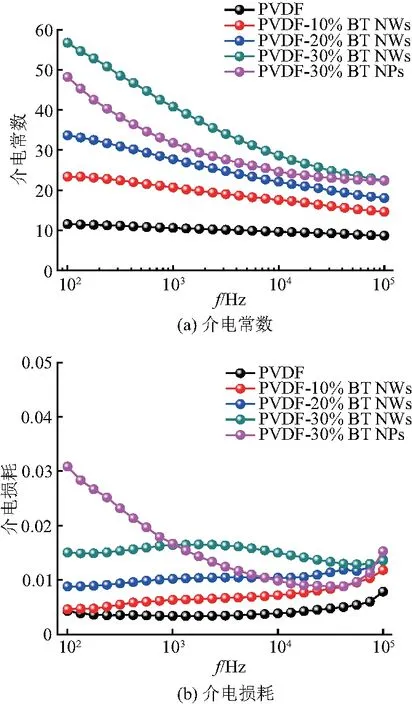

在聚合物基体中填充少量的一维(1D)陶瓷纳米结构可以更有效地提高复合材料的介电性能.选择具有较大长径比的介电陶瓷纳米线填料不仅能提高复合材料的介电常数,而且有利于改善复合材料的机械性能.相比于球形粒子,纳米线填料在较低的体积填充分数时,就能获得较高的介电常数.文献[20]研究了通过水热法合成的高长径比的钛酸钡纳米线和PVDF复合材料的介电特性,如图4.随着钛酸钡填充量的增加,在整个测试频率下,材料的介电常数呈增加趋势,这主要是由于高介电常数钛酸钡的加入,并且介电损耗较低.100 Hz时,BT体积分数为30%的纳米复合材料的介电常数为58,比纯PVDF(10.7)提高了5倍以上;同时也高于填充球形颗粒复合材料的介电常数.这说明纳米线形态的钛酸钡填料的性能要高于球形颗粒的.

图4 PVDF/BT NWs复合材料的介电常数和介电损耗

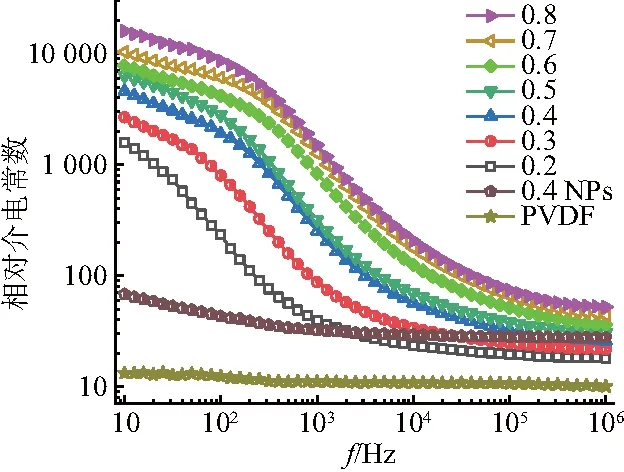

文献[21]利用水热法首次制备了三维花状钛酸钡陶瓷颗粒(BTFs),并于PVDF复合制备成复合材料,研究其介电性能如图5.在所有研究的频率下,复合材料的介电常数随BTFs的增加而增加.且PVDF/BTFs复合材料的介电常数在10~100 Hz的低频区域具有异常稳定的很高值.当BT填料呈花状形态时,界面极化[21-22]会大大增强,从而导致巨介电常数升高.在10 Hz下,当填料F-BT的体积分数为0.2、0.3、0.4、0.5、0.6、0.7和0.8时,介电常数分别为1 580、2 670、4 590、6 320、8 390、10 785和16 020,而0.4的球形填充颗粒的介电常数仅仅只有200,在不改变陶瓷成分的前提下,通过改变陶瓷颗粒的形貌就可以大幅度地提高复合材料的性能.

图5 PVDF/BT花状颗粒复合材料的介电常数

总之,通过在聚合物基体中加入高介电常数的陶瓷填料以及加入不同维度的陶瓷颗粒可以有效地提高复合材料的介电常数.但是复合材料的击穿强度会随着陶瓷填料比例增大而急剧减小.因此当前的聚合物/陶瓷复合材料研究中,单纯通过增大陶瓷填料的比例来提高复合材料介电常数对于提高储能密度而言并不是一项行之有效的手段.

2 聚合物/陶瓷复合材料击穿强度的影响因素

聚合物/陶瓷复合材料的电击穿主要与聚合物基体的电击穿相关,其击穿强度不仅受到聚合物基体击穿强度制约,而且还受到聚合物/陶瓷界面性质、复合材料多层结构设计等因素的制约.

2.1 陶瓷界面性质对复合材料击穿强度的影响

由于陶瓷颗粒与聚合物基体间巨大的介电常数差异,导致了聚合物/陶瓷复合材料内部局域电场分布的不均匀化,电场强度在低介电常数的聚合物基体中被局部增强,从而导致复合材料的击穿.为了减弱陶瓷填料和聚合物基体间由于介电常数巨大差异造成的电场局域增强,最有效方法的便是对陶瓷表面改性和在陶瓷填料的表面搭建核壳结构.填料粒子的表面处理对改善复合材料的介电性能有重要作用.通过表面改性,可以降低粒子之间的相互作用,改善分散性,另外还可以提高粒子与聚合物基体之间的界面相容性,降低由于粒子团聚等带来的缺陷,使得材料变得更加致密.

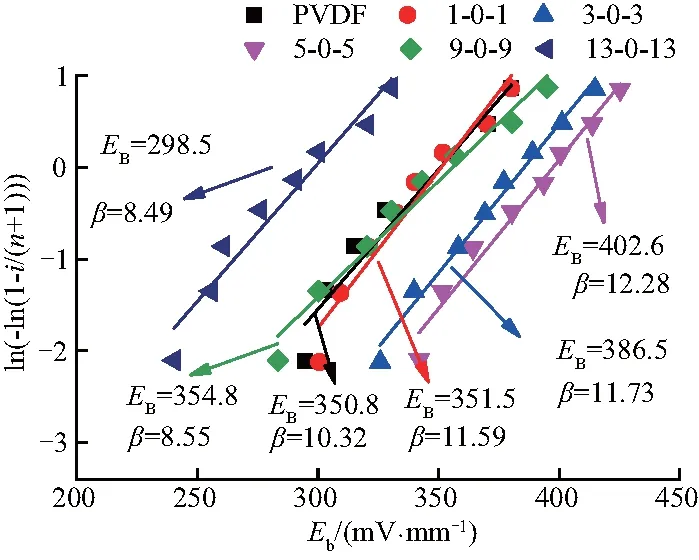

文献[7]人研究了PVDF-过氧化二异丙苯(DCP)/BT@γ―氨丙基三乙氧基硅烷(KH550)复合材料的介电特性.复合材料的Eb为430.7 MV/m,高于原始PVDF.文献[22]提出了一种提高PVDF纳米复合材料击穿强度的表面改性方法,经改性剂TC-2处理后,BT NPs表面形成了一层含有活性有机基团的包覆层(mBT),大大提高了纳米填料与基体的相容性.随着改性剂用量的增加,单分散mBT-2 NPs的击穿强度从纯PVDF的397 kV/mm提高到517 kV/mm,如图6[23].

图6 PVDF/BT复合材料的击穿强度

表面改性和核壳结构一方面改善了陶瓷填料与聚合物之间的相容性,另一方面有利于缓解陶瓷填料和聚合物基体间由于介电常数的差引起的局域电场过高以及屏蔽载流子路径的作用,已被理论和实验证实是一项能够有效提高击穿强度的技术方案.

2.2 复合材料多层结构的设计对复合材料击穿强度的影响

近年来,通过构建多层复合材料并调节陶瓷填料在不同层间的比例来进行结构设计,被用于增强聚合物-陶瓷复合材料的击穿强度.通过调整外层和中间层的填料含量,可以显著提高陶瓷/聚合物纳米复合薄膜的击穿强度.文献[23]制备了高纵横比2D NaNbO3,并将其作为填料加入到聚合物基体中.此外,还设计了三层三明治结构复合薄膜,外层为高介电常数NaNbO3/PVDF,中层为高击穿强度原始PVDF.实验结果表明[24],通过改变2D NaNbO3的含量,可以同时调节复合薄膜击穿强度,如图7.

图7 NaNbO3/PVDF复合材料的击穿强度

因此,与单层的复合材料相比,多层结构中具有较低陶瓷含量的层被认为能够提供有的载流子陷阱来抑制隧穿,从而提高复合材料的击穿强度、获得更高的储能密度.

3 结论

尽管近年来在聚合物/陶瓷复合介电材料方面的研究取得了重要进展,但仍然不能完全满足电子工业的发展对介电材料高储能密度、高介电常数、低介电损耗、低击穿强度、高柔性、轻量化和热稳定性的要求.目前主要研究了如何提高介电常数和击穿强度两个方面去提高储能密度.在实际中,同时提高介电常数和击穿强度不可兼得.所以研究制备能够满足应用于嵌入式电容器的陶瓷/聚合物电介质复合材料仍是今后的一个热点.可以通过在聚合物基体中填充具有高介电常数的陶瓷填料以及改变陶瓷填料的形貌增加复合材料的介电常数;以及通过陶瓷填料的表面改性和设计多层复合材料的结构提高复合材料的击穿强度等思路开发高储能密度的电介质材料.