一种基于SiP 技术的高性能信号处理电路设计

2023-10-07王庆贺郑利华

王庆贺,郑利华,顾 林,江 飞

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

0 引言

随着电子信息技术的发展,对集成电路的体积、质量和性能的要求越来越高。由于半导体工艺接近物理极限,多年来遵循传统摩尔定律的晶体管特征尺寸等比例缩小的发展趋势已放缓,难以满足电子信息产业发展的需求。而SiP 系统级封装技术在系统层面延续了摩尔定律,得到行业越来越多的关注[1-3]。SiP 技术是一种把裸芯片、微组件、阻容器件高度集成在一起的封装技术。它采用2D 平铺或者3D 堆叠的形式把裸芯片、电子元器件通过异构或者异质的方式封装在一起,组成一个实现特定系统功能的封装件。其优势主要是体积小、质量轻、密度大、性能高、可靠性强[4-6]。

针对信号处理模块小型化、高性能需求,本文设计了一款基于SIP 技术的高性能信号处理电路,该电路将多种不同的裸芯片、阻容器件集成在一个SiP 芯片中,其体积更小,质量更轻,性能更强。

1 系统功能结构

该高性能信号处理SiP 电路内部集成一颗6000 系列8 核DSP 作为处理核心,一颗NOR Flash 用于存储程序,一颗DDR3 微组件扩展系统内存,一颗千兆网PHY芯片实现千兆网通信,SiP 电路对外有多种高速和低速接口用于通信。该SiP 电路整体功能框图如图1所示。

图1 电路整体功能框图

2 电路设计

2.1 SiP 电路组成和外部接口

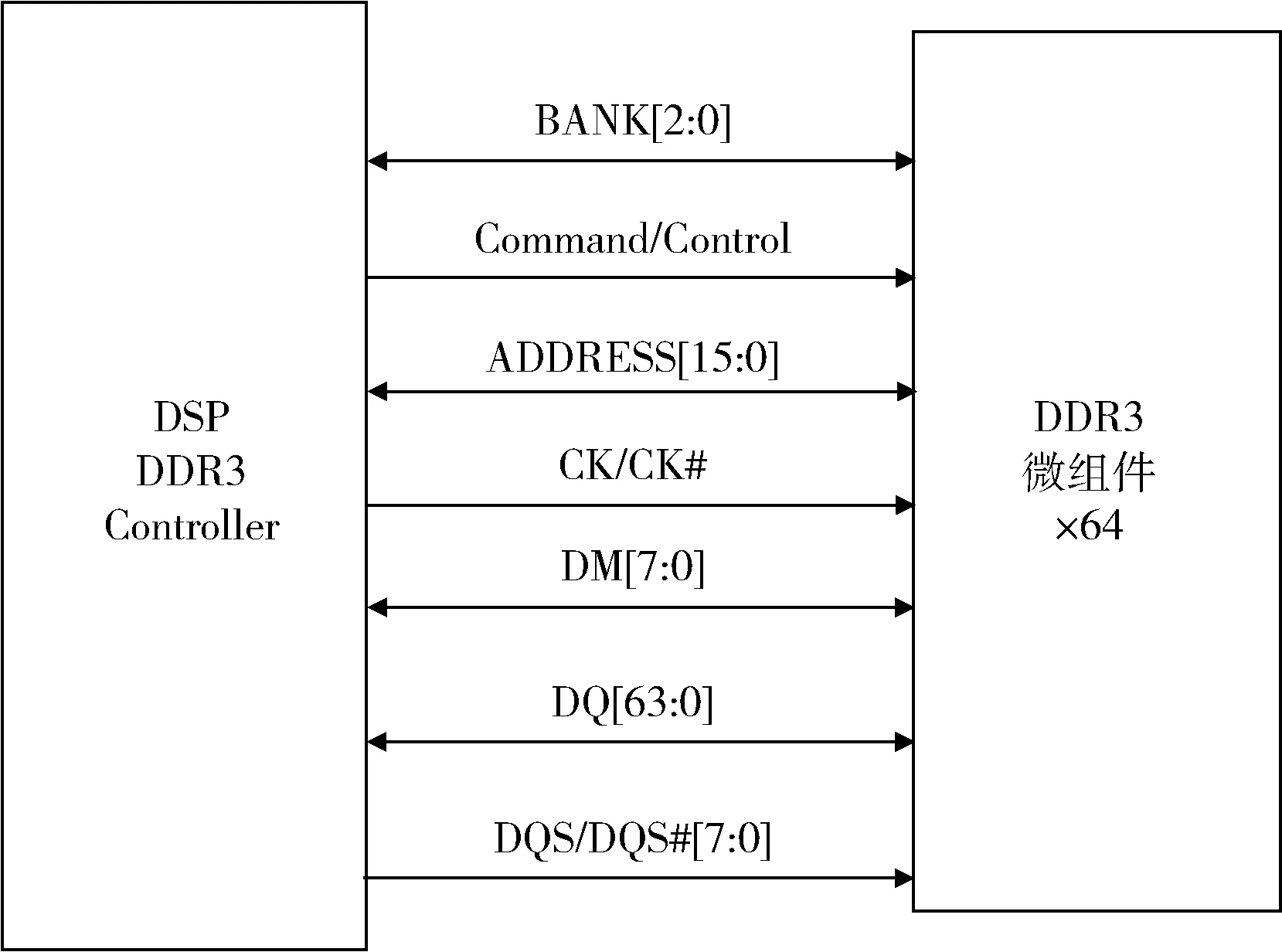

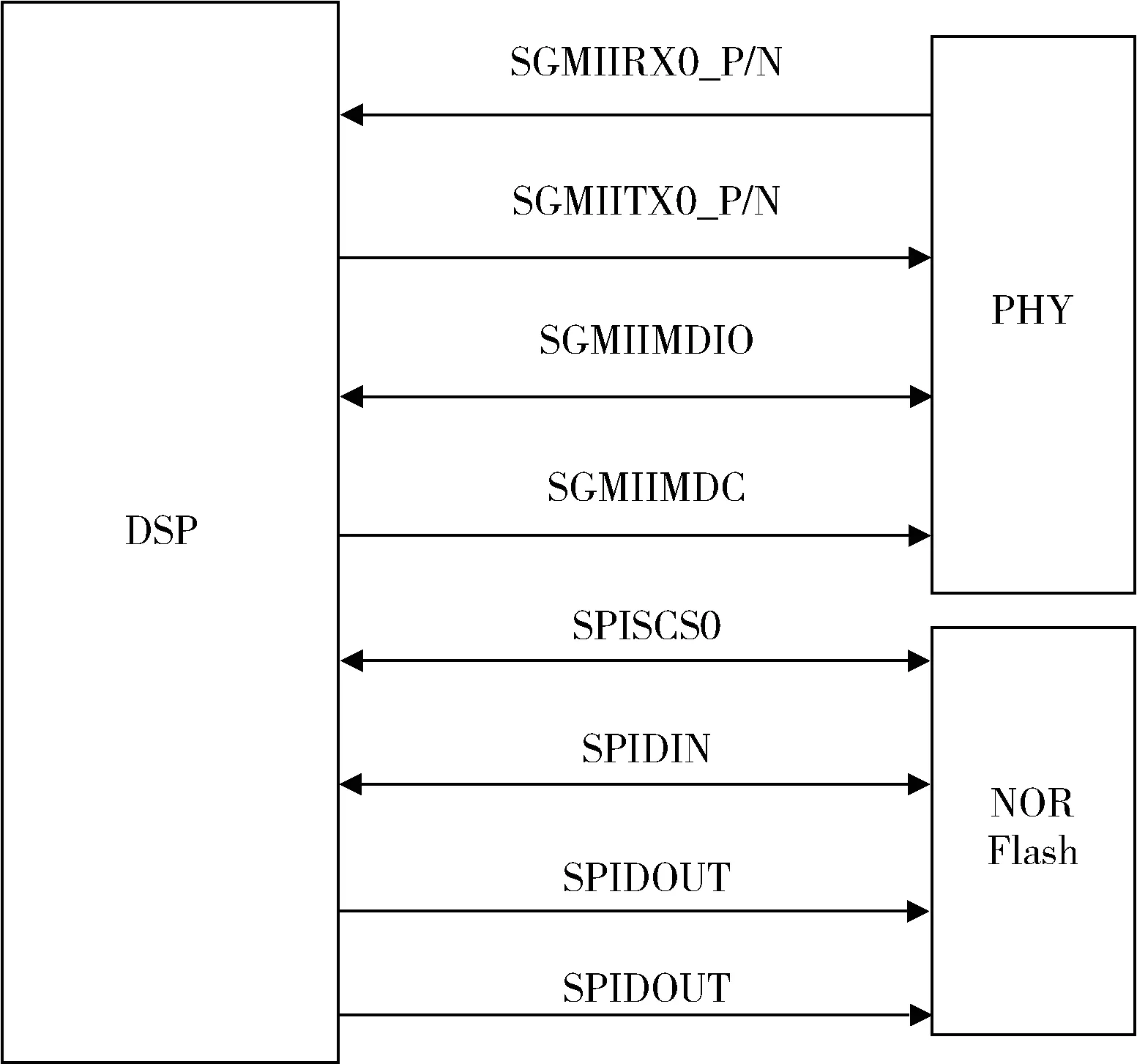

该高性能信号处理SiP 电路使用的DSP 为6000 系列高性能处理器,最大主频1 GHz,具有8 个处理核心;NOR Flash 的容量是128 MB;DDR3 微组件的容量是2 GB,位宽是64 位,DDR3 最高时钟频率为800 MHz;PHY 芯片支持10/100/1000 Mb/s 以太网通信。

SiP 电路中DSP 和DDR3 微组件连接的硬件设计框图如图2 所示;DSP 与千兆以太网PHY 芯片、NOR Flash芯片连接的硬件设计框图如图3 所示,DSP 通过SGMII接口与PHY 进行通信,通过SPI 接口访问NOR Flash芯片。

图2 DSP 和DDR3 微组件连接的硬件设计框图

图3 DSP 与PHY、NOR Flash 连接的硬件设计框图

该高性能信号处理SiP 电路有多种对外接口,接口类型和主要指标如下。

(1) RapidIO 总线接口:由DSP 引出两路RapidIO 接口,支持 RapidIO 协议V2.1,支持1×/4×数据传输模式,最大支持每Lane 3.125 Gb/s 传输速率。

(2) PCIE 接口:支持双模工作模式,既可作为根节点(RC 端),也可以作为端设备(EP 端),支持×1、×4 串行接口,每Lane 支持2.5 Gb/s 和5 Gb/s 传输速率。

(3)千兆网口:支持10/100/1 000 Mb/s 的数据传输速率。

(4) EMIF 接口:总线宽度32 位,支持同步、异步存储器,存储器宽度支持16、32 位。

(5) SPI 接口:支持SPI 串行协议,全双工通信,支持4 种通信模式。

(6) UART 接口:由DSP 引出一路UART 接口,UART接口的主要功能特点是支持查询和中断两种工作模式,典型速率为115 200 b/s,支持FIFO,FIFO 深度为32字节。

(7) I2C 接口:符合I2C 总线协议,支持8 bit 数据传输模式,可以选择10 位和7 位地址模式,数据传输速率范围是10 kb/s~400 kb/s,支持中断。

(8) GPIO 接口:DSP 引出16 路GPIO 接口,每个GPIO 都支持输入和输出模式。

2.2 软包封验证

在SiP 电路加工制作前,需要进行验证,由于SiP 软包封验证直接使用裸芯进行验证,相较于原型验证板(使用成品芯片)验证是一种更好的验证方式[7-8]。软包封验证时,首先需要整理裸芯信息,包括芯片大小、端口排布等,然后在PCB 板上进行裸芯片的键合,完成软包封封装,并将该软包封电路插在测试板上进行功能和性能测试,来确定裸芯片选的是否合适、布线是否正确。

2.3 封装与工艺设计

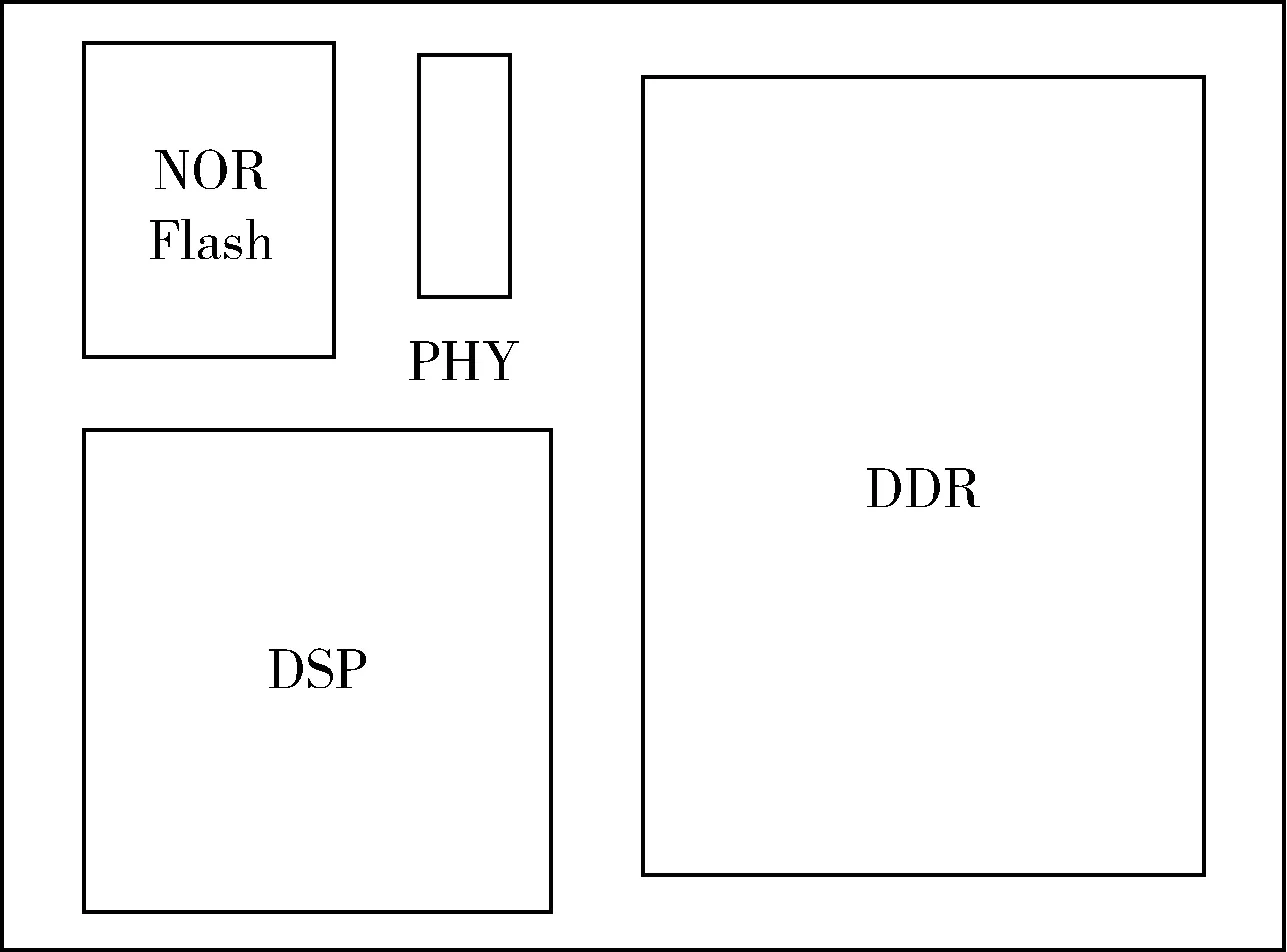

该SiP 电路采用塑封基板,基板一共6 层,其中信号层4 层,电源层2 层。采用塑料球栅阵列封装,外形为BGA713,整体尺寸为26.80 mm×19.40 mm×2.90 mm(不含植株)。基板上面主要包括一颗DSP 裸芯、一颗NOR Flash 裸芯、一颗千兆PHY、一颗DDR3 微组件以及若干阻容,采用塑封基板走线的方式,实现DSP 与NOR Flash、PHY 和DDR3 微组件以及少量阻容的内部互连。基板的结构示意如图4 所示,基板三维结构侧视图如图5 所示。

图4 基板结构示意图

图5 基板三维结构侧视图

根据DSP、NOR Flash、PHY、DDR3 微组件和阻容件的大小以及芯片叠层的技术要求,在塑封基板上组装这些裸芯片以及阻容器件,芯片空间、芯片间距及与基板的间距均符合封装工艺要求。DSP 裸芯、NOR Flash裸芯和DDR3 微组件采用FC 工艺直接焊接在基板上,PHY 芯片使用金丝键合工艺键合到基板上,采用先进的三维集成封装工艺实现。封装工艺流程为物料准备、基板处理、阻容装片、FC 芯片装片、回流焊、底部填充、清洗、填充固化、焊膏印刷、植球、清洗[9]。

2.4 电路部分仿真

在SiP 电路完成基板和管壳设计后,根据基板和管壳,进行了信号完整性和电源完整性仿真。

2.4.1 DDR3 信号仿真

对DDR3 的信号进行时域仿真,得到的控制和地址信号眼图以及数据线信号眼图如图6 和图7 所示,信号眼图质量较好,满足DDR3 信号质量要求。

图6 控制和地址信号眼图

2.4.2 电源仿真

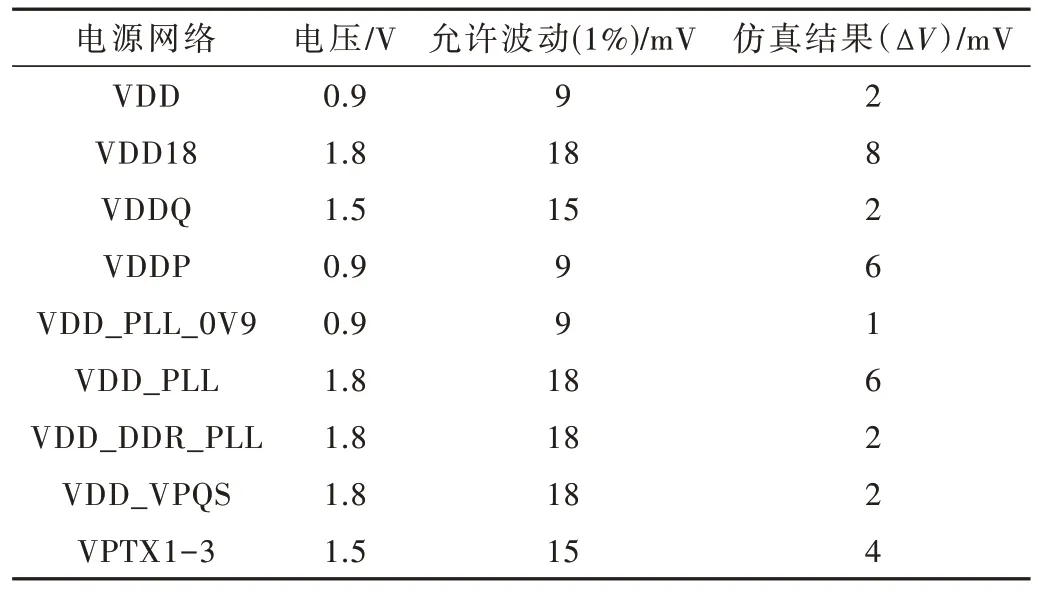

为确保SiP 电路各供电分区的电源品质,对关键电源信号进行电源完整性仿真,仿真结果如表1 所示。由表格可知,仿真的各个电压的波动值均在所要求的1%的范围内,直流压降满足要求。

表1 电源仿真结果

3 测试与验证

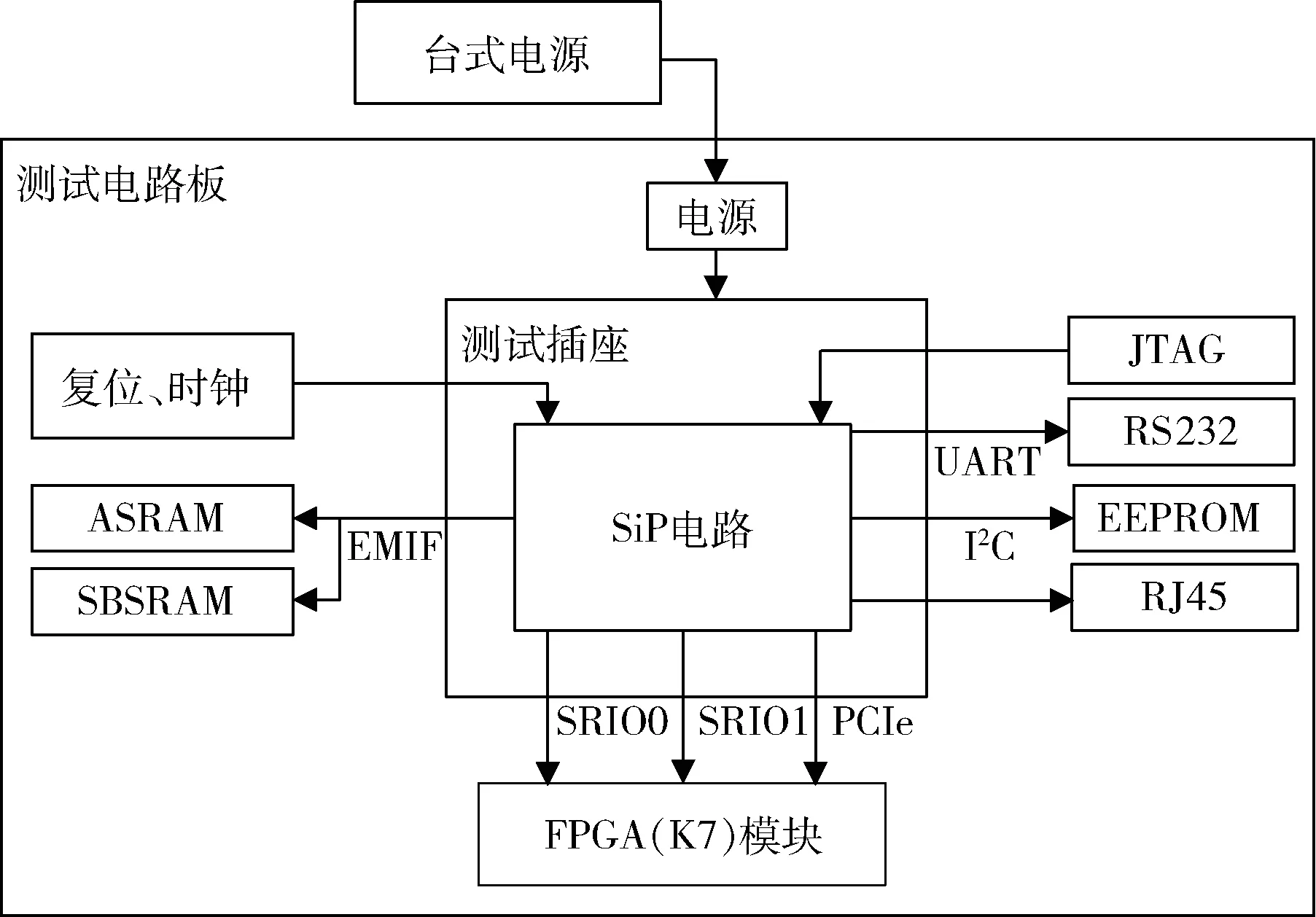

SiP 采用堆叠形式实现,最终成品率取决于各层良率,测试贯穿整个过程[10-11],主要包括裸芯片/圆片测试、组装过程测试和SiP 成品电路系统测试三个部分。SiP 电路测试方案如图8 所示。

图8 SiP 电路测试方案图

3.1 芯片/圆片测试

该SiP 的电路主要裸芯片包括:DSP、NOR Flash、DDR3 和PHY 芯片。DSP 是FC 芯片,NOR Flash、DDR3采用再布线技术(RDL)将WB 转换为FC,使用FC 封装技术键合到基板上,而千兆网口采用WB 工艺,使用金丝键合工艺键合到基板上。

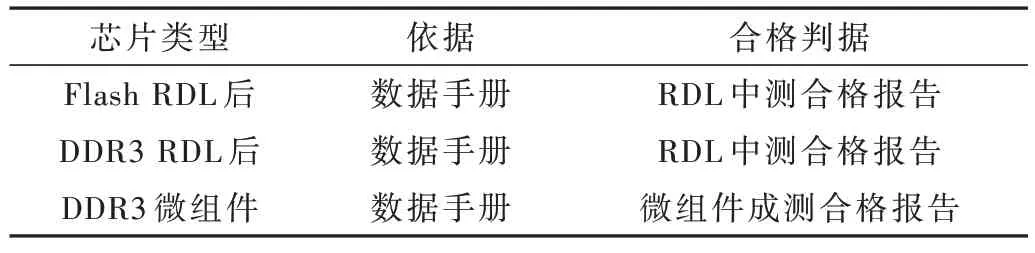

为保证SiP 成品电路的合格率,必须要确保装配到SiP 管壳的裸芯片都是合格的。需要根据数据手册进行测试,并出具中测合格报告,裸芯测试的依据和合格判据如表2 所示。

表2 裸芯测试表

3.2 组装过程测试

SiP 电路组装过程测试主要有探卡测试和KGD(Known Good Die)插座测试两种。中测探卡测试主要用于NOR Flash 和DDR3 RDL 后测试。KGD 插座测试用于DDR3 微组件测试。组装过程测试依据和合格判据如表3 所示。

表3 组装过程测试表

3.3 系统测试

SiP 成品电路的系统测试主要包括ATE 测试和实装板测试两个部分。ATE 测试需要制作ATE 测试电路板和测试插座,然后在ATE 测试机上进行成品电路的功能、性能和可靠性测试来检测SiP 电路在封装环节是否有异常,功能是否正常,在做了各项试验后是否仍然可以正常运行[12]。

实装板测试主要是对微系统成品电路的功能、性能和接口进行PCB 板级测试,该SiP 的实装板测试项主要包括处理器JTAG 连接测试、DDR3 读写测试、NOR Flash 读写测试、千兆网口测试、UART 接口测试、I2C 接口测试、PCIe 接口测试、SRIO 接口测试、EMIF 接口测试以及GPIO 测试等,通过最终的功能、性能测试,保证了SiP 电路的正确性。

该SiP 成品电路实装测试板框图如图9 所示,SiP 的各个对外接口都连接了外设,用于对每个接口的功能进行测试。在进行实装板测试时,实装测试板上FPGA 已下载测试用程序,将SiP 电路放置在测试插座中,并烧写DSP 程序,之后通过上位机下达指令进行实装测试,测试结果通过上位机显示,通过上位机软件一键自动化测试,十分方便。制作完成的SiP 成品电路和实装测试板如图10 所示。

图9 成品电路实装测试板框图

图10 SiP 成品电路和实装测试板

3.4 测试结果

一共研制了20 颗该型号的SiP 初样电路,测试重点关注了集成各芯片的电路功能,以及内部电路互联和对外扇出引脚特性,在三温(-40℃、25℃、85℃)下进行ATE 和实装功能测试,20 颗SiP 电路中ATE 测试项全部通过,实装板测试时,除了7 号、16 号SiP 的EMIF 接口测试项未通过外,其他SiP 的测试项都测试通过。

4 结论

本文给出了一种高性能信号处理SiP 电路的设计方案和测试方法,较详尽地叙述了该电路的系统组成、对外接口、封装设计、仿真和测试流程。使用系统级封装技术设计的高性能信号处理电路,相对于板级电路,其在性能和可靠性同样的状况下,体积、重量进一步降低,符合信号处理模块小型化的研制要求。