一种基于三管开关结构的改进型电荷泵设计

2023-09-23周运乐张豪哲

周运乐,张 瑛,张豪哲,殷 鹏

(南京邮电大学 集成电路科学与工程学院,江苏 南京 210023)

随着新能源汽车行业迅速发展,对汽车芯片的需求日渐增加, 低压差分信号(Low Voltage Differential Signaling,LVDS)数据传输接口电路是大多车载显示屏芯片中不可或缺的电路之一[1]。 在LVDS 接口电路中,通常需要锁相环电路产生低抖动的时钟信号以供数据传输使用,目前较为广泛使用的是电荷泵(Charge Pump,CP)锁相环(Phase-Locked Loop,PLL)。 在电荷泵锁相环中,由于CP的时钟馈通等非理想效应,PLL 的输出时钟会产生较大的抖动[2]。

目前已出现了多种优化技术以减弱电荷泵的非理想效应,其中全差分结构因其可将电荷泵的非理想效应带来的误差转化为共模噪声,从而大幅抑制非理想效应,被广泛应用于低抖动锁相环。 Zeng等[3]提出了一种正反馈结构的全差分电荷泵,提高了电荷泵的开关速度并且降低了电流的失配,但其电路结构较为复杂且占用大量版图面积;黄水龙等[4]利用放大器使输入有效跟踪输出,将杂散降低到-75 dBc,但其引入放大器增加了功耗并且限制了速度;王征晨等[5]利用共源共栅电流镜电荷泵,将锁相环参考杂散降为-56.9 dBc,但其对输出摆幅有较大限制。 以上研究都未能改善电荷泵中的时钟馈通效应。

本文主要对电荷泵中开关信号引起的时钟馈通等效应进行研究,提出了一种具有三管开关结构的全差分电流舵电荷泵,能够有效抑制电荷泵的时钟馈通效应,同时具备较小的电流失配、电荷共享和电荷注入等非理想效应,可应用于低抖动锁相环。

1 电荷泵对锁相环性能影响

1.1 电荷泵的基本原理

锁相环中的鉴频鉴相器(Phase and Frequency Detector,PFD)和CP 将输入时钟与输出时钟的相位差转化为电荷的输出或抽取,经过环路滤波器(Low Pass Filter,LPF),产生控制压控振荡器(Voltage Controlled Oscillator,VCO)的电压[6]。 图1 为一个简单电荷泵的结构以及原理示意图。

图1 电荷泵结构及工作原理示意图

传统CP 由两个开关以及两个电流源按照如图1(a)所示的结构组成,PFD 输出的UP 和DOWN信号控制上下开关对LPF 进行充放电,从而改变VCO 控制电压。 从图1 可以看出,电荷泵平均输出电流为

其中,Icp为电荷泵电流,φref为参考时钟的相位,φout为输出时钟的相位。

将电荷泵和鉴频鉴相器作为一个整体,其传递函数为

1.2 电荷泵的非理想效应

图2(a)所示为采用CMOS 电流镜及CMOS 开关管实现的传统CP,下面分析该电路中的非理想效应[7]。

图2 传统电荷泵的非理想效应

首先,由于实际电流源的有限阻抗、PVT 等因素,输出节点电压变化使电流源的电流并不完全保持不变,从而使电荷泵增益产生非线性;其次,由于MOS 管实际上存在寄生电容,会带来电荷共享效应,MOS 管沟道电荷也会导致电荷注入效应,这些都会带来电流的失配;此外,由于开关MOS 管频繁地开关,也会产生严重的时钟馈通效应。

1.3 由电荷泵误差造成的锁相环抖动

电荷泵的时钟馈通等非理想效应通过锁相环的闭环反馈,会在鉴频鉴相器输入端产生静态相位误差。 即使在锁相环处于锁定状态时,这些误差使CP在每个参考时钟周期向LPF 注入或者抽取的电荷并不为零,这会使VCO 的控制电压产生纹波,PLL输出时钟产生抖动[8]。

理想情况下,锁相环处于锁定状态时LPF 上的总电荷量应当保持不变,而当总电荷量发生变化时,必然会产生静态相位误差,由此可以计算出电荷泵的非理想效应所导致的锁相环静态相位误差。 其中电荷泵产生误差的几个主要机理如图3 所示。

图3 电荷泵误差造成的静态相位误差

如图3(a)所示,时钟馈通导致充放电电流产生波动,从而导致环路滤波器上的电荷量发生变化,并且电荷泵开关频率越高,影响越大。 以CP 充电为例,假设时钟馈通电流为Ip(t),馈通时间持续t0,产生的误差电荷为

锁相环处于锁定状态时,为了保持LPF 上的电荷量保持不变,需要在PLL 输入端产生一个负静态相位差φserr,表现出来为DOWN 导通时间比UP 导通时间长,从而抵消上述机制产生的误差电荷。 对应的静态相位误差为

其中,Tref为参考时钟周期,Icp为电荷泵理想的充放电电流。

如图3(b)所示为电流失配效应,将UP 和DOWN 同时导通的时间定义为电荷泵导通时间Ton。在电荷泵导通时间里,若充电电流比放电电流低p%,则一个周期注入LPF 的额外电荷为

同理可以求出该静态相位误差为

由式(6)可以看出,静态相位误差与电荷泵导通时间和充放电电流误差成正比。

CP 与LPF 也会产生一定的静态泄漏电流,如图3(c)所示。 这些电流也会造成静态相位误差。假设静态泄漏电流为Ileak,则在一个参考周期内,所有的泄漏电荷为

同理可以求出此机制对应的静态相位误差为

上述所有静态误差加大了VCO 控制电压的电压波动,进而增加了锁相环输出时钟的抖动。

在整数锁相环中,当环路带宽相对参考频率较高时,电荷泵的非理想性对输出时钟抖动的增加是非常显著的。 在数据传输中,时钟抖动太大会严重增加误码率[9]。

2 低抖动的全差分电荷泵设计

本文所提出的改进型全差分电荷泵电路结构如图4 所示,其中两个差分输出端分别接到一个跨导放 大 器( Operational Transconductance Amplifier,OTA)的差分输入端,从而产生压控振荡器的控制电压。

图4 差分电荷泵电路结构

在全差分电荷泵电路中,通常很难实现PMOS电流源电流Ip与NMOS 电流源电流In大小完全相同,假设PMOS 电流源的内阻等效为rp,NMOS 电流源的内阻等效为rn。 两个电流的差值流过等效输出阻抗,会使输出电压产生大小为(Ip - In)(rp‖rn)的变化,因为(rp‖rn) 很大,即使(Ip - In) 很小,对输出电压的影响也会很大,会驱使电流源进入线性区。 电流源进入线性区将会使充放电电流失配非常大。 为使输出共模电平得以确定,从而使电荷泵充放电MOS 管电流源均工作在饱和区,需要采用共模负反馈电路,本文采用传统的四输入管共模反馈电路[10]。

电荷泵的非理想效应会对OTA 的输入产生共模扰动,这些共模扰动会体现在输出电压上,从而影响锁相环的参考杂散以及抖动。 由于设计高共模抑制比的OTA 具备一定难度,所以减少输入端的共模扰动也就是电荷泵输出电压扰动,是非常必要的。

单个电荷泵电路结构如图5 所示,其中M7 与M12 分别为该电荷泵的充电、放电电流源,M8 与M10 分别为充电与放电的MOS 开关。 为了抑制CP的时钟馈通效应,提出了一种三管开关结构,图5 中的M1~M3,M4~M6,M15~M17,M18~M20 每3 个MOS 管构成一个三管开关。 以M4~M6 为例,当IN1 信号为高电平时,M4 管子截止,此时M5 与M6构成一条通路,M5 的栅极电平可使M8 开关管导通;反之,当IN1 信号为低电平时,M4 管子导通,此时M4 与M6 构成一条通路,M5 相当于被短路从而截止,其栅极电平可使M8 开关管断开,从而实现开关管的导通与关断。 M6 的偏置电流应大于电荷泵主通路的电流很多,以确保当M5 导通时M8 也导通。 令VTH为MOS 管的阈值电压,Vdd为电源电压,引入此结构后, 由于M8 在导通时的栅压由0 变成Vdd-VTH,使MOS 开关管在状态切换时的栅压变化减小,从而开关频繁切换所导致的时钟馈通效应被有效抑制,使式(3)中Ip(t)极大降低。 同时,该结构采用互补型开关实现电流舵,当IN1 为低电平时,M8 管关断,IN1B 为IN1 的互补信号,通过开关控制结构使M16 截止,M15 导通使M9 导通。 此时,M7、M9、M13 三个管子构成一条通路,保持充电MOS 管电流源始终导通,使式(7)中Ileak降低,抑制了泄漏电流以及电流失配效应,同时也增加了电荷泵的导通关断速度,由此降低了PMOS 管电流源与NMOS管电流源之间的失配对整体电路的影响。

图5 单个电荷泵结构图

3 仿真结果

将所提出的电荷泵与传统电荷泵分别放入锁相环[11]中进行仿真,该锁相环系统结构如图6 所示,其中参考时钟频率Fref为40 MHz。 LPF 采用二阶低通滤波器结构,VCO 增益KVCO为200 MHz/V。

图6 电荷泵锁相环系统拓扑图

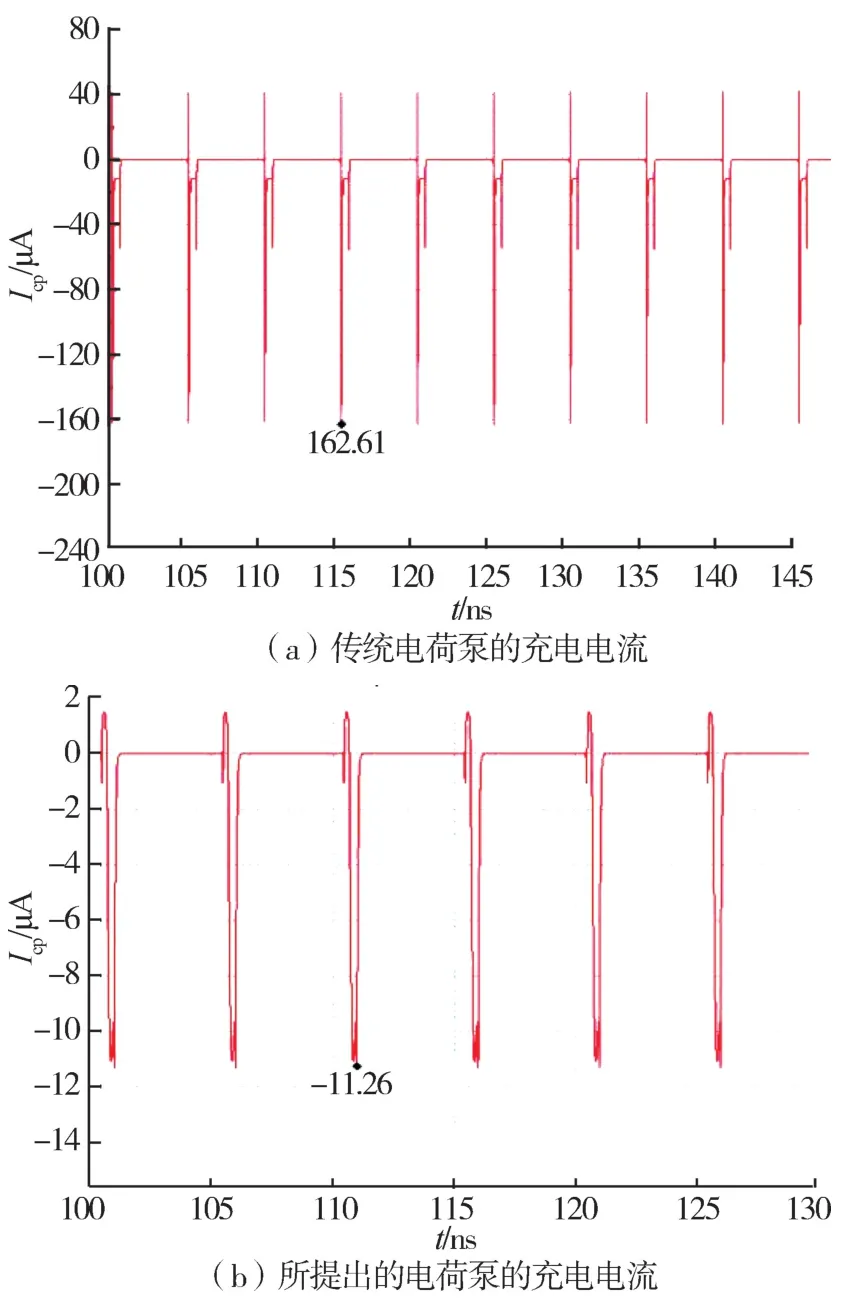

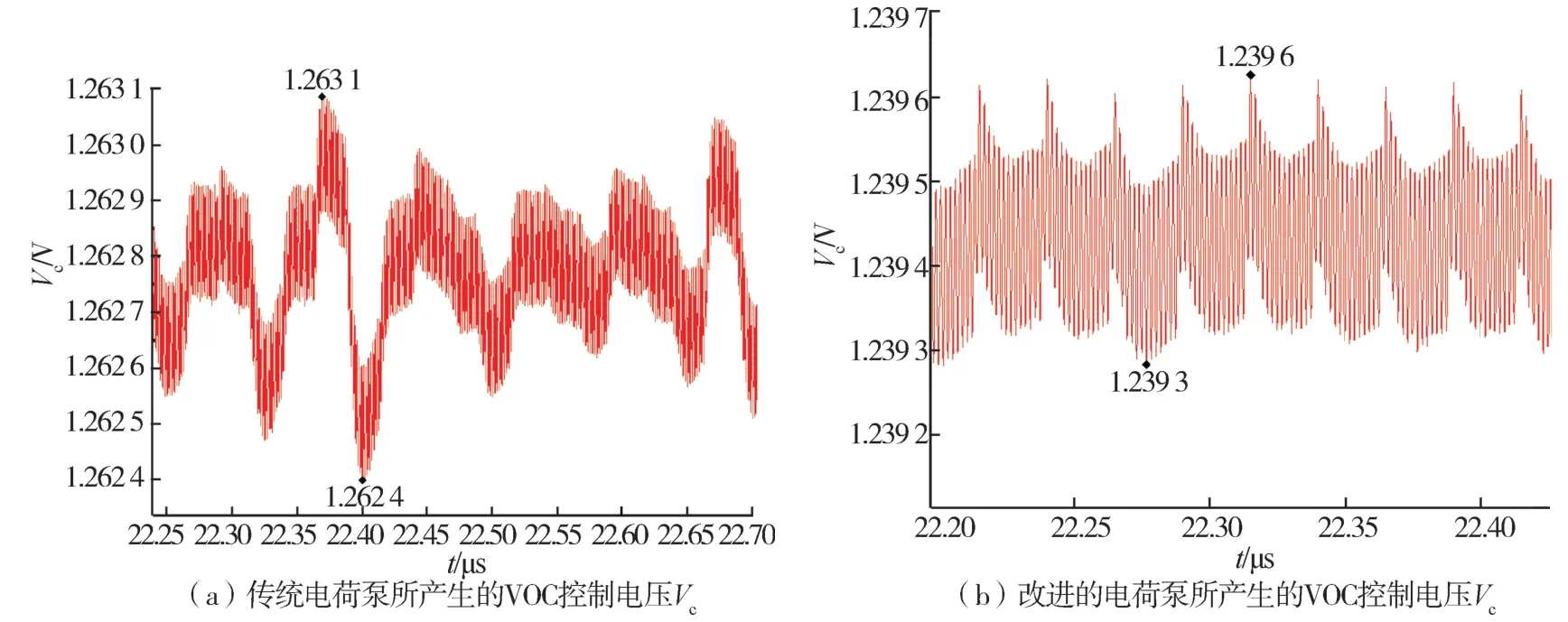

基于28 nm CMOS 工艺进行电路原理图和版图设计,并通过Hspice 进行仿真实验。 图7 为两种电荷泵的充电波形图,可以看出传统的电荷泵在每周期充电时电压都会出现1 mV 左右的抖动,而改进的电荷泵几乎无抖动。 图8 为两个电荷泵在PLL稳定状态下充电电流波形图,可以看出当充电电流为10 μA 时,传统电荷泵的时钟馈通尖峰电流最大可达到162.6 μA,根据式(3)和式(4)可计算得到,因时钟馈通产生的静态相位误差φserr约为0.56π,本文结构可以将时钟馈通尖峰电流最大值减小到11.2 μA左右,同理可算得时钟馈通效应导致的静态相位误差约为0.1π。 图9 为全差分电荷泵产生的压控振荡器的压控电压Vc,可以看出Vc的波纹从0.7 mV 减小到0.3 mV 左右。 锁相环参考杂散一般表示为

图7 传统电荷泵(Vt)与改进的结构(Vn)的充电电压波形

图8 传统电荷泵与所提出电荷泵的充电电流

图9 两种电荷泵产生的VCO 控制电压Vc

其中,Vm为Vc上的纹波幅值。 可以得到优化后的结构参考杂散约为-68.5 dBc。

实验结果表明,所提出的改进型电荷泵结构极大地减弱了时钟馈通等非理想效应,使得PLL 的输出时钟在40 MHz 时的抖动从约118 ps 降低到了约36 ps。

图10(a)为所提出的电荷泵电路的版图,整个版图的面积仅为48 μm×62 μm。 仿真得到的输出电压(Vc)波形如图10(b)所示,可以看出电压纹波为0.5 mV,相对传统电荷泵产生的电压依然有很大的改善。 本文与其他文献所涉及的电荷泵参数对比如表1 所示,与文献[3,5]相比,本文结构在电路复杂度以及参考杂散抑制上皆有改进;文献[4]在采用运放的情况下虽然能够较好地抑制参考杂散,但提高了设计的复杂度;文献[12-13]在实际应用中杂散抑制能力一般且电路复杂。 而本文所提出的电荷泵采用了三管开关以及全差分结构,在降低电路复杂度的同时也能较好地抑制参考杂散。

表1 本文与其他文献电荷泵参数对比

4 结束语

本文在分析目前锁相环中电荷泵技术缺陷的基础上,提出了一种三管开关结构,将其与全差分电流舵电荷泵电路相结合,在减小了电荷泵的开关时钟馈通效应等非理想效应的同时,也兼顾了电荷泵的充放电速度。 该结构能够有效抑制电荷泵锁相环输出时钟的抖动。 仿真实验结果表明,电荷泵输出电流为10 μA,锁相环在输出时钟频率为40 MHz 时,参考杂散为-68.5 dBc,输出时钟抖动只有36 ps,达到了低抖动锁相环的设计目的。 本文所提出的改进型电荷泵可应用于诸多数据传输电路中的时钟模块。