基于轻量级分组密码算法的SoC安全存储器设计

2023-09-18曾祥义

刘 伟,曾祥义,肖 昊

(合肥工业大学 微电子学院,安徽 合肥 230009)

随着信息产业的不断发展和物联网(Internet of Things, IoT)产品的大规模应用,嵌入式片上系统(SoC)作为物联网的硬件基础设施,其安全性直接影响整个物联网系统的安全。SoC由嵌入式微处理器、存储器模块以及外部通讯接口等模块组成,恶意攻击者可以使用侵入式和半侵入式分析的方法窃取或篡改高价值信息。

冷启动攻击是一种针对RAM存储器数据的半侵入式攻击。RAM中的数据可能包含敏感信息,例如密钥、证书等。动态随机存储器(Dynamic Random Access Memory,DRAM)断电后,其存储单元的电容充电状态会保持一段毫秒级的时间,若将DRAM置于低温环境,断电后电容充电状态的保持时间将大幅延长。冷启动攻击利用DRAM的数据剩余特性,将DRAM存储器置于低温状态并断电保存内存关键数据,然后利用相关技术将内存中的数据转存到其他计算机上,恢复内存中的关键数据[1]。研究表明,在低温情况下,DRAM中的数据在断电后可保留几分钟甚至数十分钟,便于攻击者在断电后恢复DRAM中的敏感数据。而除了DRAM,冷启动攻击也可有效攻击静态随机存取存储器(Static Random-Access Memory, SRAM)。在温度低于-20 ℃时,SRAM的数据断电后可以保存几分钟甚至几十分钟[2]。冷启动攻击的出现对物理接触难度较低的物联网设备安全带来了较大威胁。除了冷启动攻击外,攻击者还可以通过局部加热攻击来获取存储器的敏感数据[3]。

探针攻击是针对存储器的一种侵入式攻击,攻击者对芯片进行物理分解,并通过微型探针直接与内部组件进行电子连接,监听芯片内部存储器的数据[4]。攻击者还可以通过电子显微镜和激光扫描显微镜研究存储器的介质,进而解析出存储器的数据[5]。

针对上述攻击手段,为了保证SoC的存储器(RAM、Flash)的敏感数据不泄漏,存储器的数据必须以密文的形式进行存储,因此对RAM、Flash等所存储的信息进行加密,确保存储器数据即使被攻击者窃取也无法被解读出敏感内容[6-8]。此外,加密方案还不能对计算性能造成较大损失。文献[9]使用软件实现RAM虚拟内存管理器,将关键数据加密后存储到RAM中。由于物物联网SoC资源受限,不搭载完整的分时操作系统,而是运行轻量级的实时操作系统,因此该方案不适用于物联网SoC。文献[10]提出使用AES(Advanced Encryption Standard)算法对内存数据进行加密,基于FPGA进行硬件设计,在50 MHz下数据带宽为35 MB·s-1。文献[11]使用国密算法SM4在CPU与存储器总线之间设计加密控制器模块。传统的分组密码算法AES具有高安全性,但其也增加了硬件设计的开销,且加密延时较高,影响了计算性能。为此,本文提出一种基于轻量级分组密码算法的安全存储器架构,使用轻量级分组密码算法LBlock-s对存储器数据加密,并在硬件实现上减少加密时序,提高数据吞吐量。

1 安全存储器结构

1.1 安全存储器结构

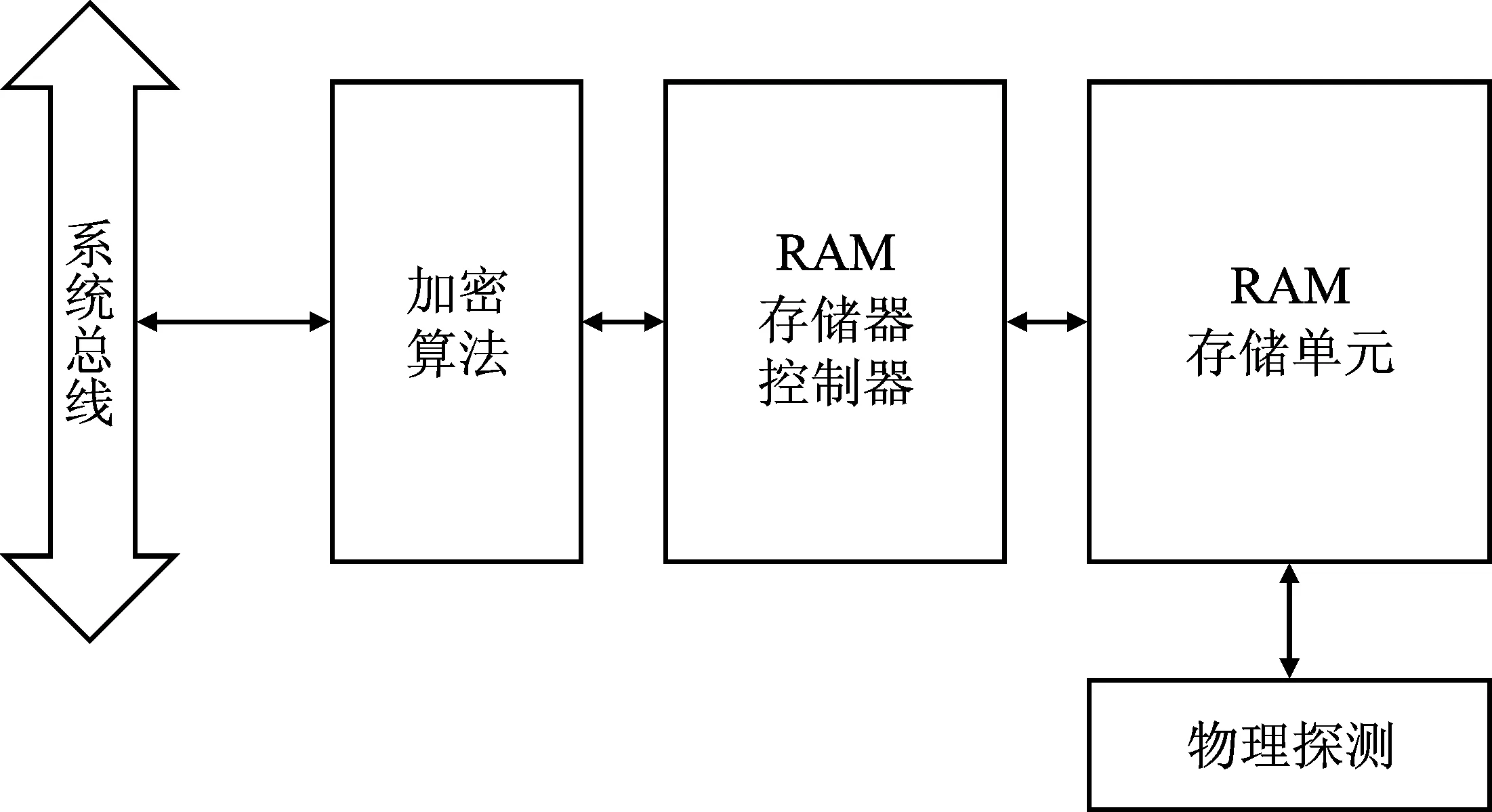

存储器面临攻击者使用物理方式对存储器的存储介质进行分析从而提取敏感数据的安全威胁。本文在传统的存储器控制器中加入硬件加密算法模块,当CPU往存储器写入数据时,来自总线的数据经过加密算法模块后存放在存储器中,当CPU从存储器读取数据时,存储器的密文数据经过解密后恢复成明文,如图1所示。这使得数据始终以密文的形式存储在存储器中,即使数据被攻击者窃取,也无法解析出敏感信息。为进一步提高数据安全性,在数据加密存储的前提下,加入地址加扰模块,对读、写操作的地址进行扰乱。此外,在进行布局布线时,应将存储器控制器的逻辑与其他数字逻辑混淆。

图1 安全存储器Figure 1. Secure memory diagram

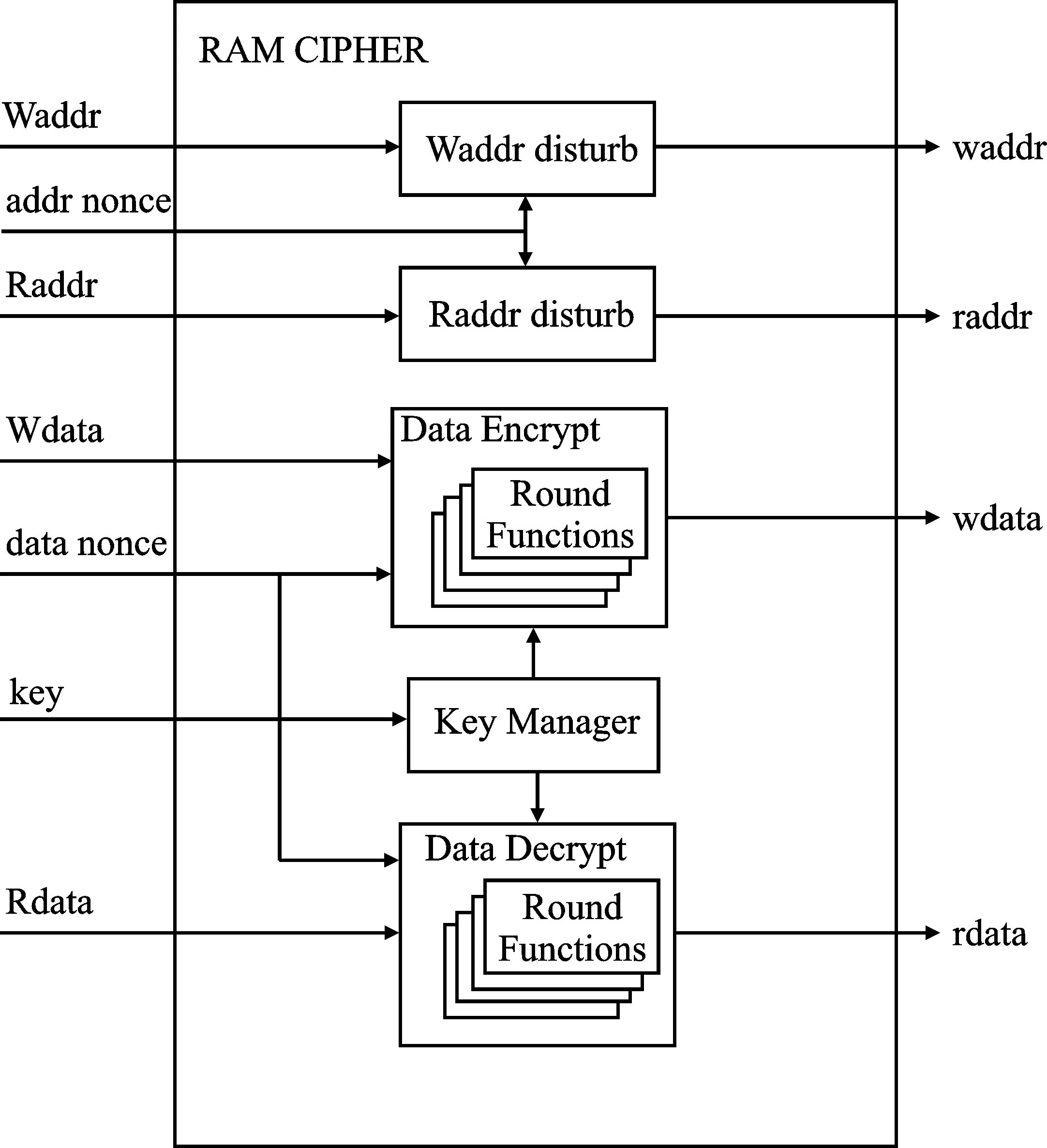

加密算法的结构如图2所示,主要分为加密和加扰部分。使用随机数对读地址信号Raddr和写地址信号Waddr进行加扰。对写数据Wdata加密后的密文数据wdata进行存储,读数据Raddr信号会先将密文rdata解密后输出明文。密钥存储在加密电路内部,在芯片的布局布线时将其隐藏在逻辑电路内部,保证密钥不会泄露。在本文中,data nonce信号和addr nonce信号还可以使用随机数将不足64位的地址和数据填充至64位,以适配不同的总线位宽。

图2 存储器加密控制器Figure 2.Memory cipher controller

1.2 轻量级分组密码算法LBlock-s

轻量级分组密码算法作为―种特殊的分组密码算法,在硬件实现、加密速度、运行功耗等方面与AES等高强密码算法相比具有明显优势,更适合物联网微型计算设备使用。近年来,轻量级分组密码算法发展迅速,多种轻量级分组密码算法已经被设计出来,比较典型的有使用SPN结构的PRESENT、LED、PUFFIN、KLEIN[12-13]等算法,以及使用Feistel结构的有HIGHT、PICCOLO、LBlock、TWINE等算法。轻量级分组密码采用了与一般分组密码相同的设计结构,可以分为Feistel结构和SPN结构。不同的设计结构都有各自的优点,如果密码算法的设计采用Feistel结构设计,则具有更容易保证在加解密算法设计过程一致的优点;如果采用SPN结构设计,则密码的扩散速度更快。

本文选择一种类Feistel结构的轻量级分组密码算法。相较于SPN结构,该算法加解密算法过程具有一致性的优点,只需要增加较少的芯片面积即可实现解密结构。

LBlock-s是LBlock[14]的精简版,在LBlock的基础上降低了软硬件实施的成本。密码算法为类Feistel结构,分组为64 bit,密钥长度为80 bit,加/解密迭代32轮。在LBlock-s中,LBlock算法中的10个不同的4 bit的S-Box被替换为1个相同的4 bit的S-Box。此外,LBlock-s改进了密钥扩展算法,避免了8位平台上29 bit的实现限制,提高了密钥扩展算法的扩散效果和对相关密钥攻击的抵抗效果[15]。

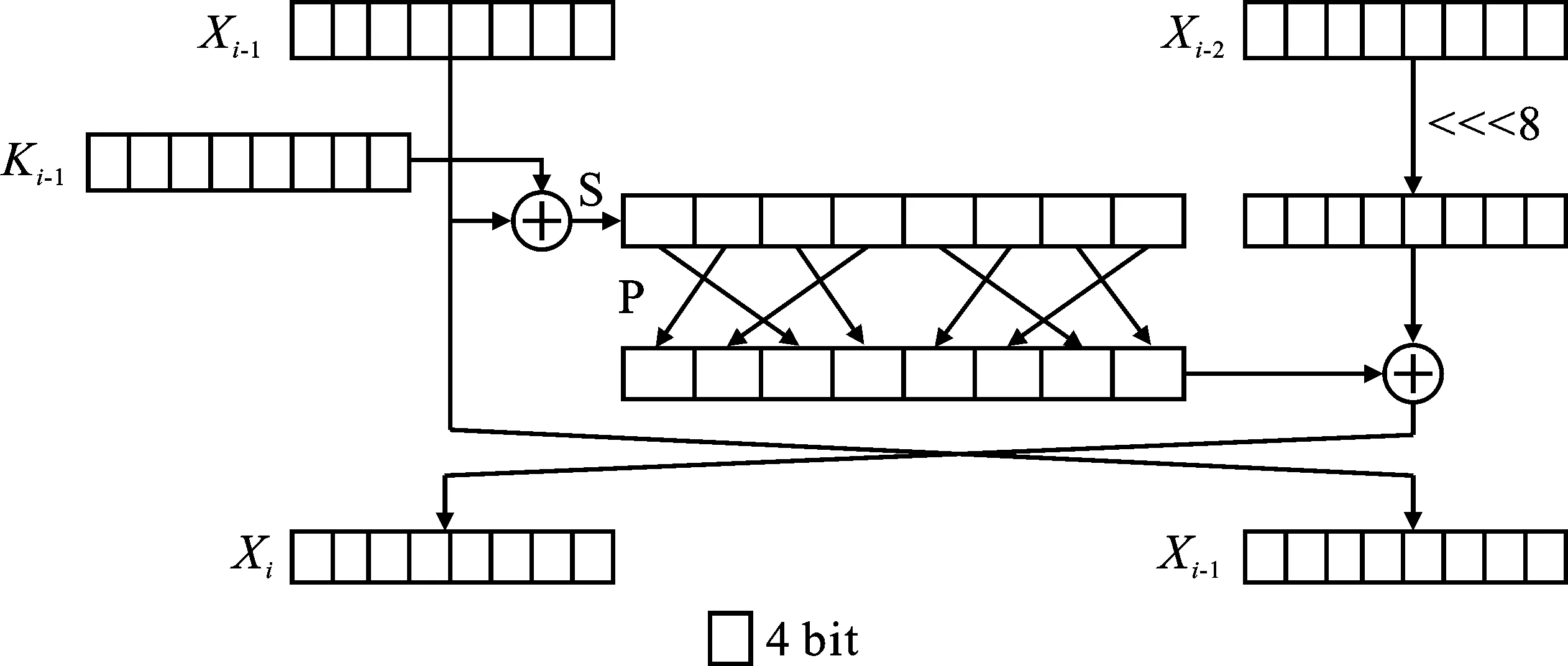

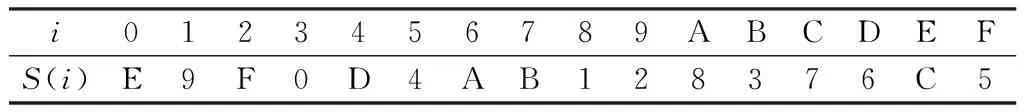

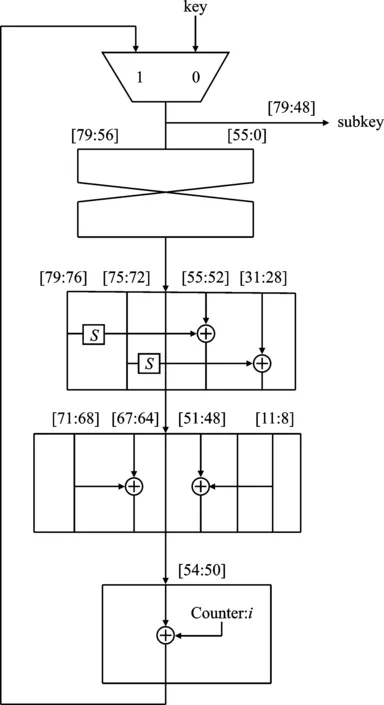

LBlock-s算法的轮函数如图3所示,轮函数由轮密钥异或、S盒替换、P盒混淆组成。S盒为4 bit输入和4 bit输出,定义如表1所示。

图3 LBlock-s算法的轮函数Figure 3. Round function of LBlock-s

表1 LBlock-s算法的S盒Table 1. S-Box of LBlock-s

LBlock-s的64 bit输入分为X1和X0两个32 bit的部分,在相同的轮函数中迭代32轮,得到X33和X32两个32 bit共64 bit的密文输出。加密过程为

Xi=P(S(Xi-1⊕Ki-1))⊕(Xi-2<<<8),

i=2,3,…,33

(1)

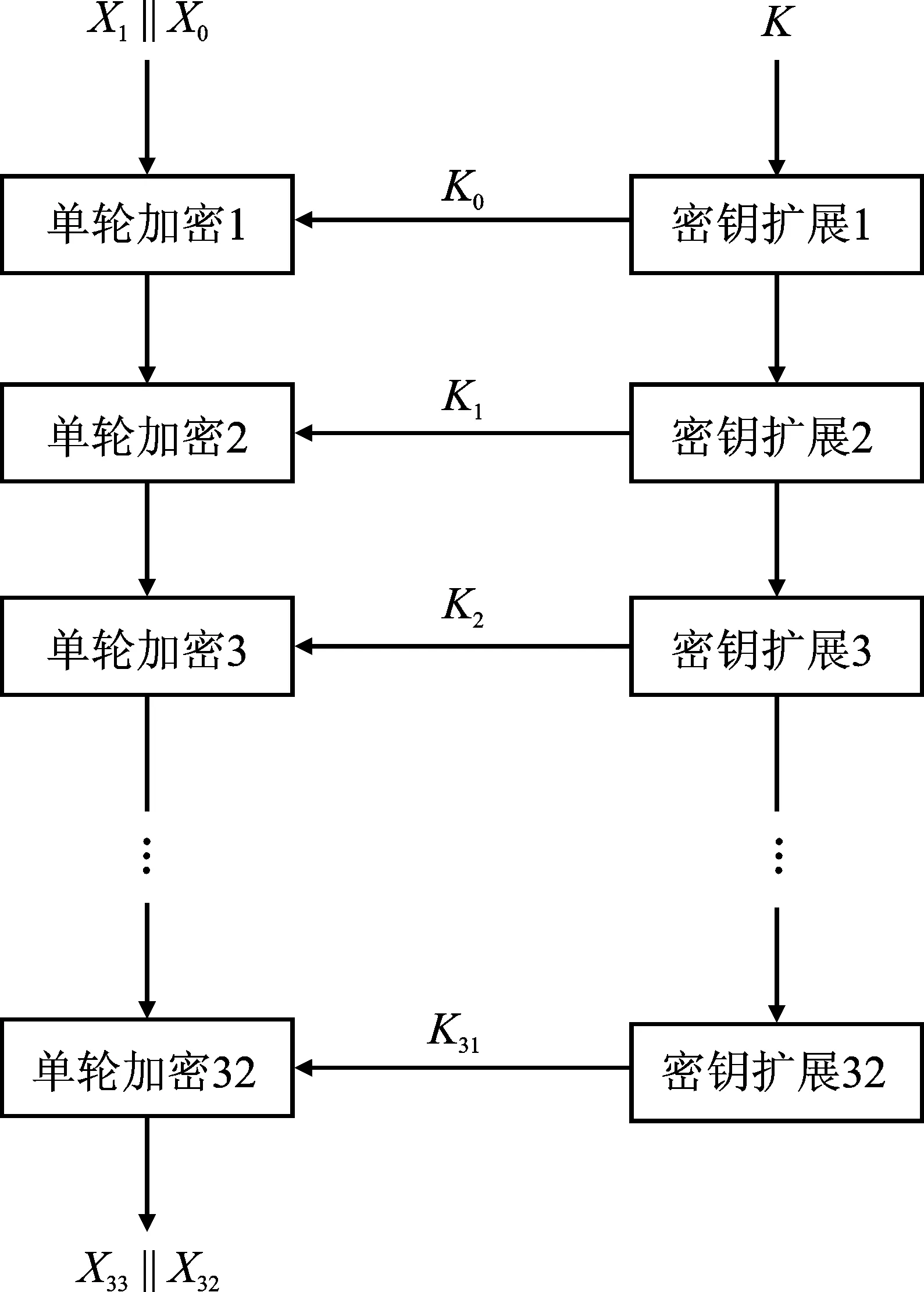

LBlock-s的密钥扩展算法为:由80 bit的主密钥K扩展为32轮迭代过程中每一轮的子密钥,即K1,K2, … ,K31,子密钥长度均为32 bit。首先将80 bit的主密钥K的高32 bit作为第一轮迭代的子密钥K1输出,然后每一轮的子密钥按如下步骤进行密钥扩展:

步骤1K<<<24;

步骤2执行

[k55k54k53k52] =S[k79k78k77k76]⊕[k55k54k53k52]

[k31k30k29k28] =S[k75k74k73k72]⊕[k31k30k29k28]

[k67k66k65k64] = [k71k70k69k68]⊕[k67k66k65k64]

[k51k50k49k48] = [k11k10k9k8]⊕[k51k50k49k48]

步骤3[k54k53k52k51k50] = [k54k53k52k51k50]⊕[i]2,i= 1, 2, … , 31。

执行完上述步骤后,输出高32 bit作为第i+1轮的轮密钥Ki+1,然后循环上述步骤,直至输出K32。轮密钥扩展过程如图4所示。

图4 LBlock-s算法的密钥扩展Figure 4. Key scheduling of LBlock-s

2 安全性分析

在现代分组密码算法中,最常见的攻击技术有差分密码分析和线性密码分析技术,以及在此基础上扩展大量的攻击方法,例如不可能差分分析、相关密钥分析、截断差分分析等。文献[16]首次引入差分密码分析来分析DES(Data Encryption Standard)分组密码。差分分析适用于包含SP结构的分组密码算法,自提出以来一直作为分析分组密码算法最有效的方法之一。随着现代分组密码算法的不断发展,密码算法抵抗差分分析的能力逐渐成为分组密码算法安全性设计的一项基本要求。对分组密码算法抵抗差分分析的安全性评估通常是寻找这个密码算法的活跃S盒的数量的下界,活跃的S盒数量的下界越大,密码算法安全性能越好。

寻找密码算法的最小活跃S盒的数量通常有两种方法:一种是根据密码算法的结构用理论证明活跃S盒数量的下界,另一种是通过算法自动计算活跃S盒数量的最小值[17]。文献[14]证明任何16轮加密迭代至少有35个活跃的S盒。

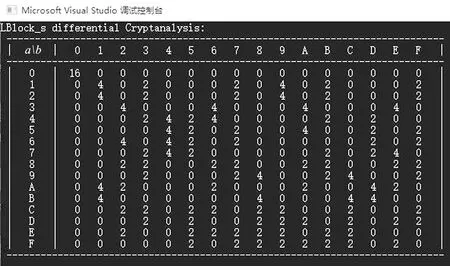

对于S盒的每一个4 bit的输入,计算S盒的输入差分和输出差分,将每个S盒的每种输入差分对应的输出差分出现次数进行统计,并将得到S盒的输入输出差分分布表。使用Visual Studio 2017环境编程实现自动输出差分分布如图5所示,其中a为S盒的输入差分,b为输出差分。

图5 LBlock-s算法S盒的差分分布Figure 5. Differential distribution of LBlock-s S-Box

根据LBlock-s算法的S盒的差分分布表可知,最大的差分概率为(4/16)=2-2。由于16轮LBlock-s算法至少包含35个活跃的S盒,因此16轮LBlock-s的差分概率小于(2-2)35= 2-70,低于64位分组穷举攻击所需要的概率2-64。结果表明该算法具有良好的抵抗差分分析的能力,完整的迭代32轮加密算法具有良好的安全性冗余。

3 算法实现结构

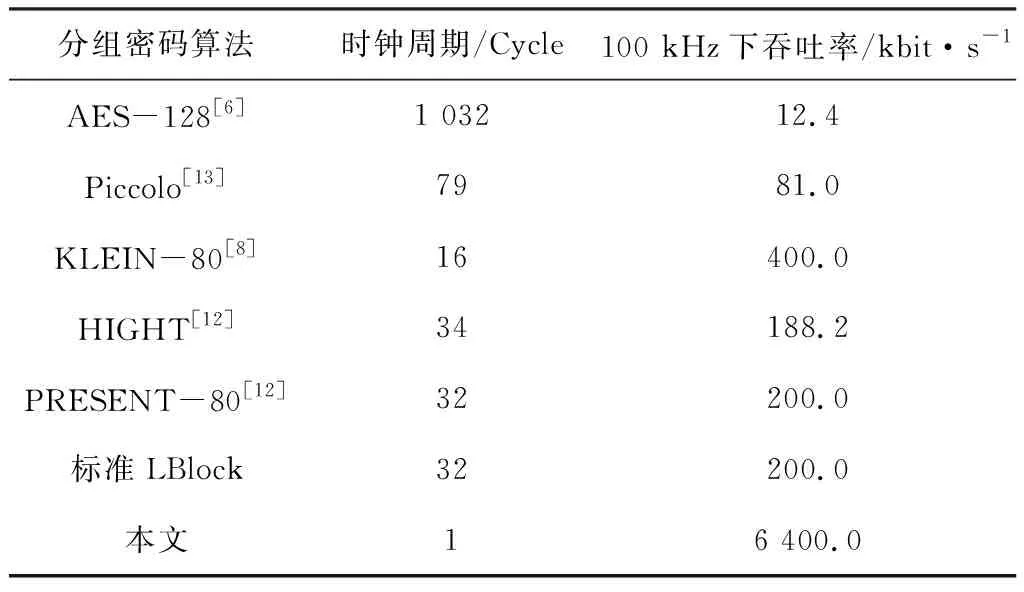

LBlock-s算法的标准硬件实现为32个时钟周期设计,每个时钟周期完成一轮轮密钥扩展与数据加/解密,将给存储器总线带来较大延时,影响存储器总线的实时性和SoC的性能[18]。本文将标准的32轮展开为1个周期,使用组合逻辑设计电路,加密电路结构如图6所示。

图6 加密算法结构Figure 6.Encryption structure

4 验证

本文的验证平台选用Quartus Prime Pro 18.1,FPGA选用Intel A10系列,CPU核心选用ARM Cortex-M0内核,系统总线基于AHB-Lite高级高性能总线协议,并加入SM系列国密算法协处理器和真随机数发生器模块,SoC总线位宽为32位。由于主流的物联网SoC多采用32位及以下总线位宽,若采用32位分组加密算法,则易通过穷举攻击破解密码算法,因此本文将总线的32位进行填充至64位再进行加密。对于无法填充对齐的数据,使用真随机数将其填充至64位。SoC设计与验证平台中采用Synopsys VCS仿真工具。

经过SoC的集成设计和FPGA原型验证,SoC的各部分模块功能正常,存入安全存储器的数据经过RAM存储器控制器加密后存入RAM存储单元中,解密后被读取。本文将LBlock-s算法时序展开到1个时钟周期,占用芯片面积的部分主要为S盒和按位异或,扩散层通过简单的布线来实现。在综合实验结果中,用等效门数GE(Gate Equivalences)来衡量面积资源,1 GE相当于一个双向与非门。在0.18 μm CMOS工艺下,S盒和按位异或约占用面积为260 GE,且算法为类Feistel结构,解密电路可复用加密部分电路,因此总体硬件成本较低。相比于其他方案,本文所提方案在硬件实现代价相对较低的前提下,显著缩短了对RAM存储器读取的延时,提高了SoC的性能。

表2 不同加密方案的性能对比Table 2.Performance comparison of different encryption schemes

5 结束语

本文设计了一种基于轻量级分组密码算法的RAM存储器控制器,在通用的存储器控制器中添加轻量级分组密码LBlock-s算法模块以及随机数加扰模块。密码分析和验证结果表明,本文所设计的密码强度符合安全性的需求,实现了对数据的密文形式安全存储,且存储器的数据吞吐率大幅度提升。该方案适用于物联网安全SoC芯片的RAM存储器和Flash存储器以及片外存储器控制器,能有效避免攻击者使用物理攻击的手段窃取敏感数据。