基于GaAs工艺的Ku波段高增益低噪声放大器

2023-08-28贾瑞林王云秀段寅龙

贾瑞林 王云秀 段寅龙 樊 琴

基于GaAs工艺的Ku波段高增益低噪声放大器

贾瑞林1王云秀1段寅龙2樊 琴1

(1.西华师范大学电子信息工程学院,四川 南充 637009;2.西华师范大学物理与天文学院,四川 南充 637009)

文章采用0.13 μm GaAs PHEMT工艺技术设计了一款MMIC低噪声放大器(LNA),该低噪声放大器工作频段为13~17 GHz,采用了双电源供电的两级放大结构,偏置电路采用电感加并联电容的滤波结构来隔离直流信号与射频信号,在第二级放大器的栅极和漏极之间引入负反馈网络来增加电路的稳定性、拓展放大器的带宽和改善增益平坦度。仿真结果表明:在13~17 GHz频带范围内,低噪声放大器的噪声系数小于1.8 dB,增益大于23 dB,增益平坦度为±1.4 dB,输入驻波比小于1.58 dB,输出驻波比小于1.45 dB,芯片面积仅为1.8 mm×1.2 mm。

GaAs PHEMT;微波单片集成电路;低噪声放大器

引言

在毫米波通信系统中,作为接收器前端的核心部分,低噪声放大器的作用是放大天线接收的微弱信号并抑制噪声。良好的噪声性能可提高接收机的灵敏度,增益可保障放大微弱的接收信号并且抑制后级链路的噪声,较宽的工作频带可扩大接收机的动态范围[1],所以研究高增益宽频带的低噪声放大器芯片具有广泛的应用前景。

韩克锋等[2]研制了14~18 GHz的低噪声放大器,该LNA增益大于17 dB,噪声系数小于1.3 dB,输入输出驻波比小于1.8,芯片面积为2 mm×1.6 mm;刘昊等[3]设计了一款12~18 GHz的低噪声放大器,在工作频带内增益大于20 dB,噪声系数小于2.9 dB,输入驻波比小于2,输出驻波比小于1.8;Murthy等[4]研制的13~16 GHz低噪声放大器采用三级级联的源退化技术,仿真结果显示增益大于22.83 dB,输入驻波比小于1.6,输出驻波比小于1.7噪声系数小于1 dB。

本文主要基于0.13 μm GaAs PHEMT工艺设计了一款Ku波段的低噪声放大器。对器件工艺、低噪声放大器设计理论和拓扑结构进行分析,总结了相关文献中低噪声放大器的指标,并与本文的结果进行对比。该低噪声放大器增益大于23 dB,增益平坦度小于1.4 dB,输入驻波比小于1.58,输出驻波比小于1.45,芯片面积为1.8 mm×1.2 mm,该芯片具有噪声低、增益高、增益平坦度好、芯片面积小等优点。

1 工艺说明

设计低噪声放大器要结合工作频带、性能、噪声系数来选择合适的工艺。砷化镓(GaAs)作为衬底材料设计的芯片具有高电子迁移率、频率特性良好、噪声性能低等优点,已经在微波射频器件得到广泛应用[5]。

赝配高电子迁移率晶体管(PHEMT)为高电子迁移率晶体管(HMET)的改进型,主要解决了HEMT中铝(Al)分子的深电子陷阱问题,采用了非掺杂的砷化铟钾层(InGaAs)代替非掺杂的GaAs层作为沟道构成,该工艺的外延材料结构如图1所示。在半绝缘的GaAs衬底使用MBE技术连续生长出GaAs缓冲层、未掺杂的InGaAs层、未掺杂的AlGaAs层、N型AlGaAs层、N型GaAs层。电子在N型AlGaAs层产生,然后向下层移动,由于InGaAs的能带较小,所以自由电子主要聚集在未掺杂的InGaAs层内,并且与未掺杂的AlGaAs层的交界面形成二维电子气,同时,In浓度的增加可以提高InGaAs层内的自由电子迁移率,使PHEMT具有更好的高频性能[6]。N型GaAs层则主要作为源极和漏极的接触层。

图1 PHMET外延材料结构示意图

2 设计理论

2.1 稳定性

在某些特定的工作频率和终端条件下,射频电路可能会产生“自激”[7],导致放大器不能正常工作甚至损坏,所以在放大器设计过程中,电路在工作频段内绝对稳定是设计前提,只有在绝对稳定的状态下,放大器的其他性能指标才有意义。判断电路绝对稳定的条件为:

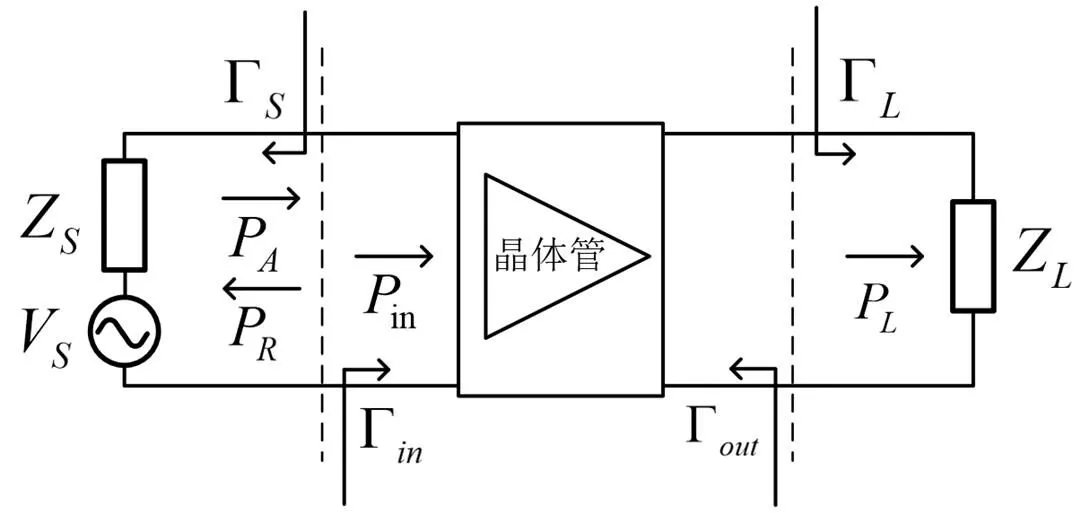

2.2 噪声系数

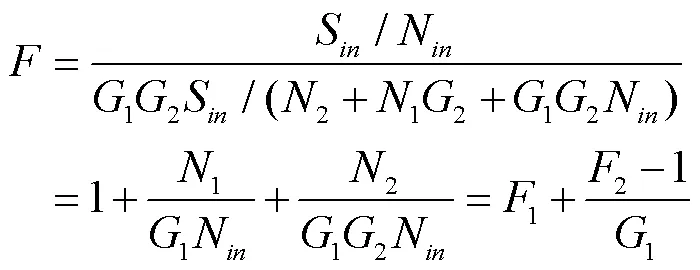

低噪声放大器噪声系数定义为输入信号信噪比与输出信号信噪比的比值:

设计的晶体管采用二级级联结构,同理对于二级级联放大器,噪声系数公式可推导如下:

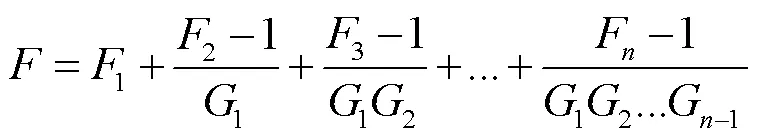

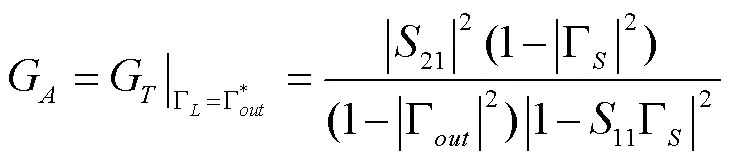

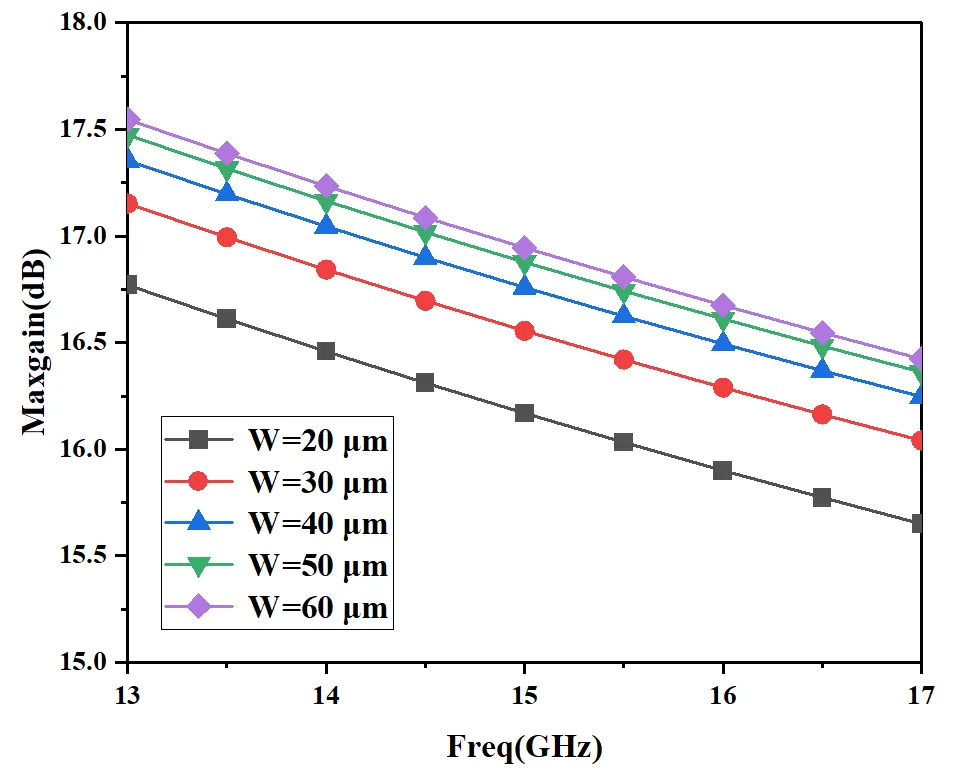

可以看出,多级低噪声放大器的噪声主要来源于第一级放大器,因此选择第一级晶体管的尺寸时要以最小噪声为主[9]。晶体管不同栅宽对应的噪声和增益也不同,在设计过程中需要根据实际情况进行选择。对该工艺在相同状态下不同栅宽的晶体管进行仿真得到栅宽与最小噪声系数NFmin的关系[6],如图2所示,随着栅宽的增加,最小噪声系数也逐渐变大。

图2 不同栅宽的晶体管与NFmin的关系

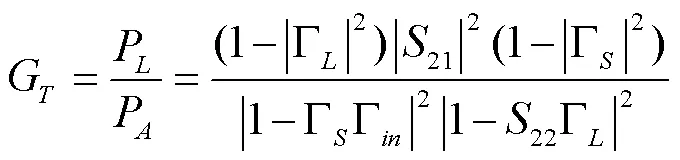

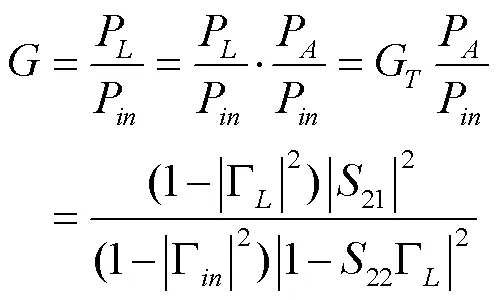

2.3 增益与增益平坦度

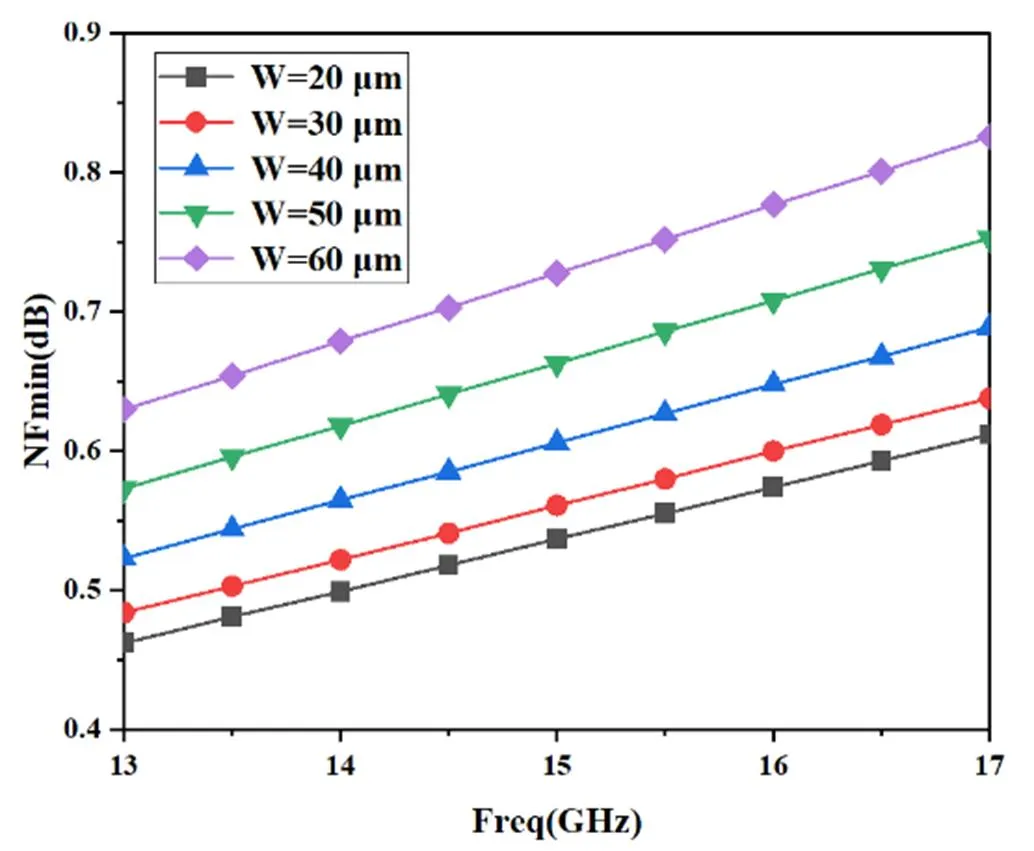

放大器的增益有多种定义,常用的有转化功率增益、资用功率增益和实际功率增益三种。转换功率增益的表达式是导出其他功率增益关系的基础,下面通过单级放大器简化电路图来分析这三种功率增益,如图3所示。

图3 单级放大器简化电路图

图4 不同栅宽晶体管与MaxGain的关系

2.4 驻波比

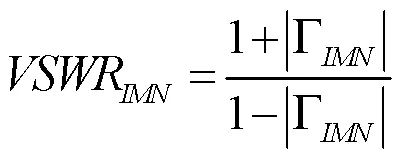

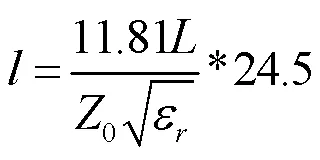

电压驻波比一般简称为驻波比(VSWR),当对放大器的输入输出端口进行测量时,其驻波比必须小于特定值,因为当阻抗失配时,电磁波会产生反射,反射波中会出现驻波,造成能量传输效率低。如图5所示的电路系统等效网络。

图5 电路系统等效网络

电路系统输入输出端口的驻波比为:

3 LNA设计

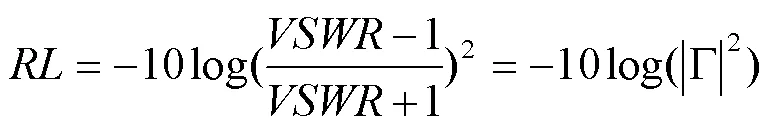

本次设计的LNA采用两级级联的拓扑结构,两级放大电路使用相同的栅漏电压,第二级晶体管采用栅极漏极局部并联的负反馈结构,来改善放大器的稳定性和增益平坦度。LNA的电路原理图和各元件优化后的具体参数如图6所示。

图6 低噪声放大器电路图

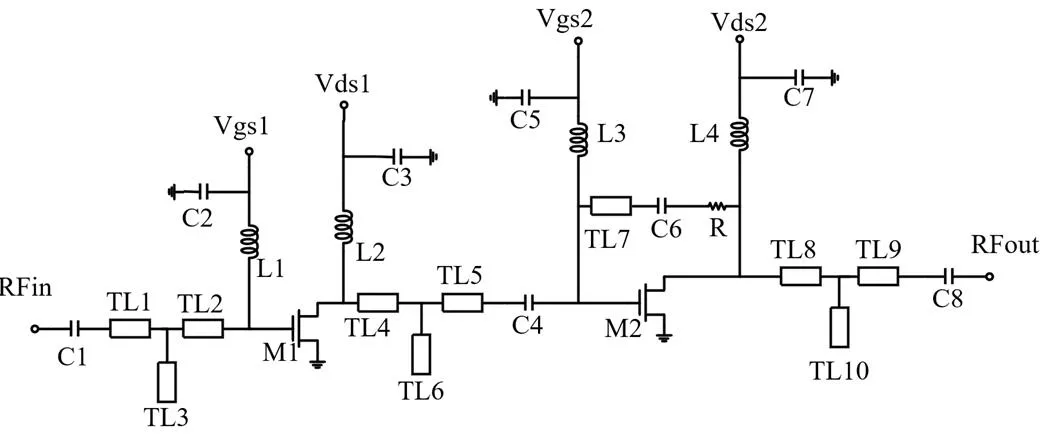

低噪声放大器设计首先要考虑的是电路的稳定性,本设计采用了在第二级放大器的栅极和漏极之间引入电阻电容电感的并联负反馈结构,同时该反馈网络也可以满足增益平坦度的要求,为了便于布版,采用了微带线代替螺旋电感,因为在特定频率条件下,可用微带线模拟电感特性,微带线的宽度由工作频率和特征阻抗决定,微带线的长度和电感值可以相互转化,转化公式为:

偏置电路的作用是在特定的工作条件下为放大器提供适当的静态工作点,以确保放大器工作特性的恒定。同时,应尽量降低偏置电路的复杂度,因为太复杂的偏置网络会引入非常多的噪声,导致噪声系数恶化。为了简化设计,第一级和第二级放大电路使用了相同的偏置结构,由于传输的是射频信号,若要保证直流电路与射频电路良好的隔离性,则要尽量降低信号对直流电路的影响,因此必须隔断射频信号。采用扼流电感加旁路电容的滤波结构可以保证直流信号能从偏置电路通过而隔断射频信号,同时通过调谐和优化设计也能使放大器处于在所需要的工作状态。

根据前面的分析可知,噪声主要来自第一级放大电路,所以对第一级放大电路做输入匹配设计时要以最小噪声为主,根据等噪声系数圆确定有最小噪声系数时的输入端阻抗,完成共轭输入匹配和最小噪声匹配。同时,对第二级放大电路做输入匹配时要以最大增益为主,以此来使LNA的噪声来源都集中在第一级放大器,通过增益圆图确定第二级放大器有最大增益时的输入阻抗,完成共轭匹配。输入输出和级间匹配结构均采用微带线组成的T型匹配网络进行设计,T型匹配网络可以看成是L型匹配网络的串接组合,具有阻抗变换的作用和阻抗补偿特性[12]。考虑到螺旋电感占用面积较大且高频时各元件之间的寄生效应会造成电路性能恶化,全部采用了微带线匹配进行设计,通过调节微带线的尺寸减小输入输出驻波比和信号在级间传输时的损耗。

4 版图设计

在对电路原理图进行仿真时得到的结果往往是不准确的,因为原理图仿真是在理想状态下对理想元器件进行的仿真,没有考虑到各元件的寄生效应和元件之间的电磁耦合,频率越高,寄生效应和电磁耦合作用越强,所以原理图仿真会与真实结果存在偏差,甚至是错误的,且原理图中各元器件的位置分布比较理想化,不涉及版图的布局规则,转化为版图时可能会出现元件尺寸过大、距离太近、重叠的情况,因此版图的设计十分重要。

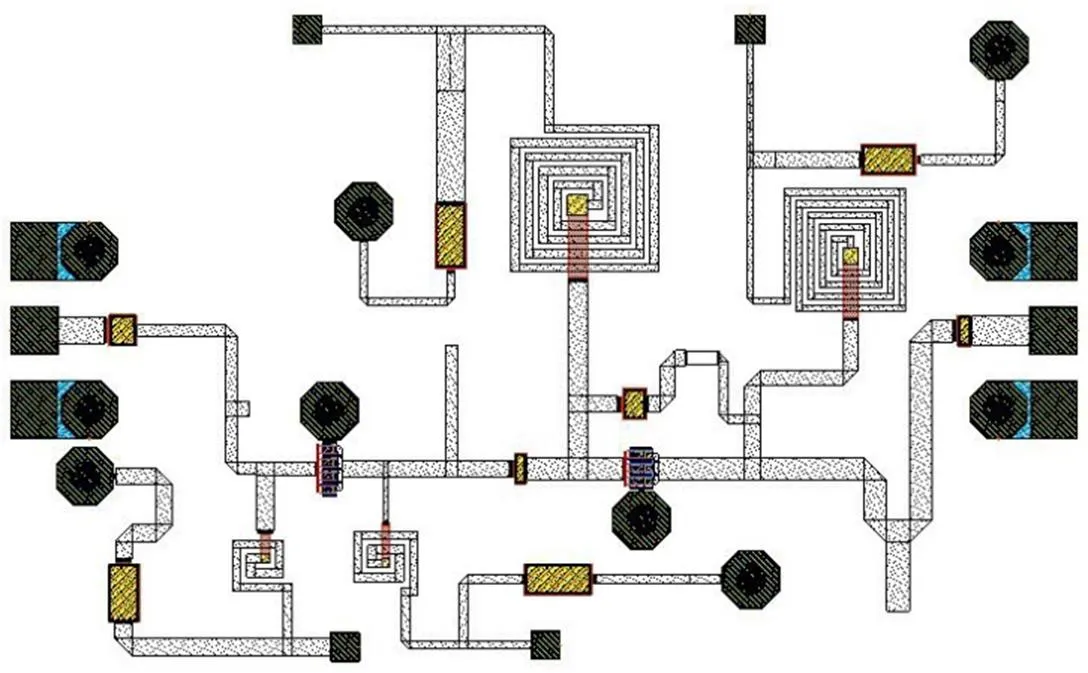

版图设计要以原理图为基础,通过调整元器件尺寸和各元器件之间的距离消除重叠,通过对微带线进行弯折来提高芯片面积的利用率,同时还要遵守该工艺的版图规则,如微带线的尺寸必须为0.5 um的整数倍,否则无法导入版图。版图布局完成后,对整体版图进行电磁仿真,电磁仿真考虑了元器件的电磁特性,接近真实的仿真环境,其仿真结果更接近芯片的性能指标,该过程需要进行多次修改和优化,最终得到的低噪声放大器芯片版图如图7所示,版图大小为1.8 mm×1.2 mm。

图7 低噪声放大器版图

5 结果分析

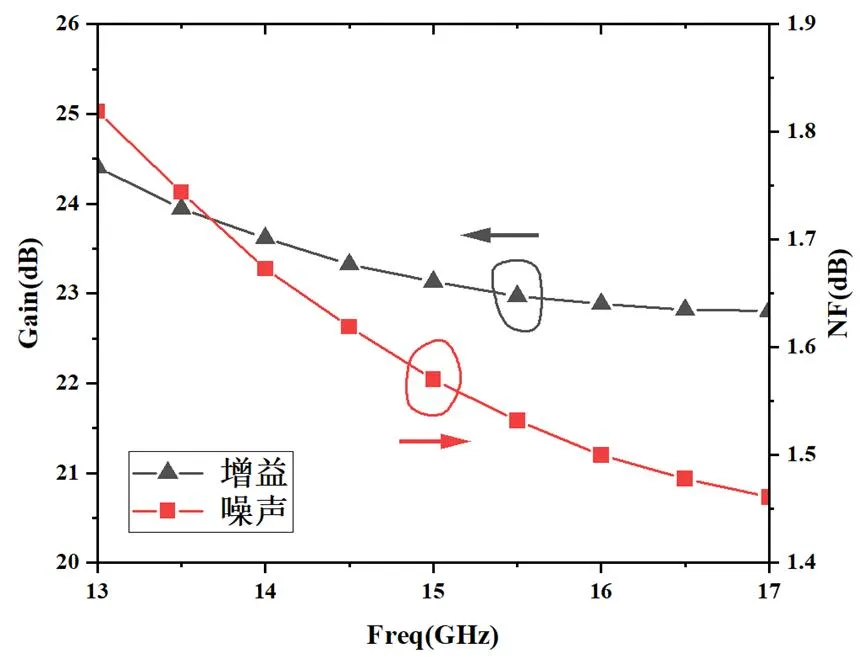

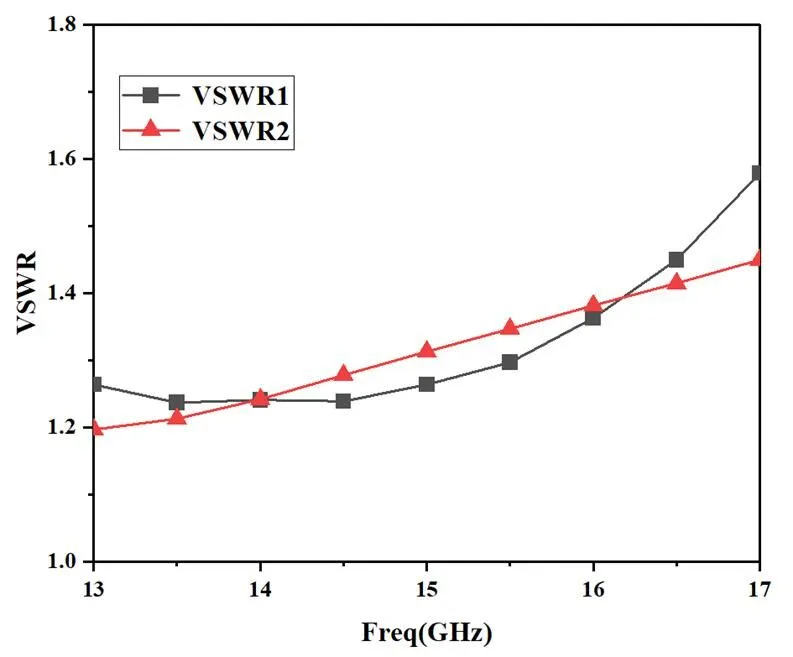

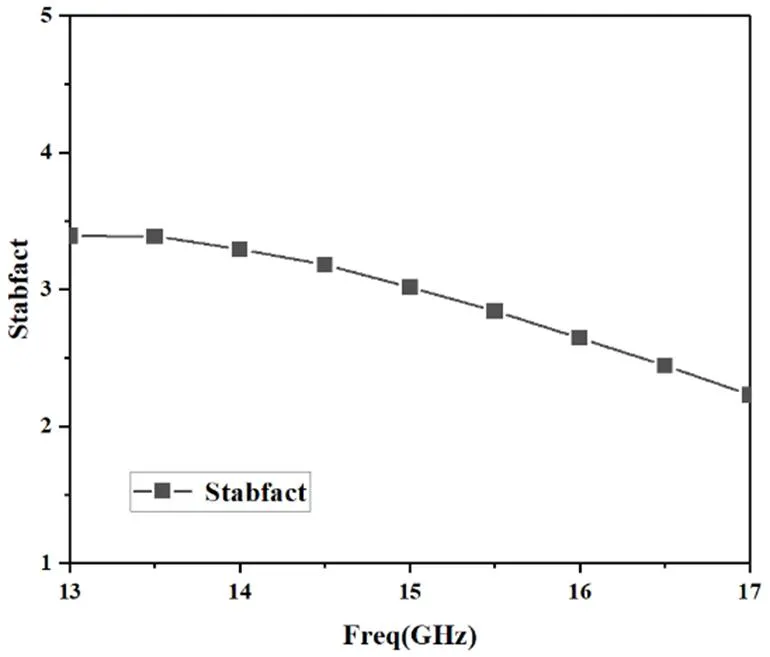

版图设计完成后对版图进行联合仿真,得到低噪声放大器在工作频段内的噪声系数、增益、输入输出驻波比及稳定性,仿真结果如图8、图9、图10所示。

图8 LNA芯片增益和噪声系数

图9 LNA芯片驻波比

图10 稳定性系数

图8显示的是噪声系数和增益随频率变化的仿真曲线图,该低噪声放大器在13~17 GHz的工作频带内,噪声系数小于1.8 dB,在17 GHz时,噪声系数最小为1.46 dB。增益在13 GHz使最高达24.4 dB,在17 GH处最低为23 dB,工作频带内增益平坦度为±1.4,表明该低噪声放大器具有良好的噪声和增益性能。图9表示的是驻波比随频率变化的曲线图,仿真结果显示,在13~17 GHz频带内,输入驻波比小于1.58,输出驻波比小于1.45,表明输入输出端口实现了良好的匹配。图10的仿真结果显示,该低噪声放大器在整个工作频带内,稳定系数StabFact大于1,确保了放大器在整个频带范围内的绝对稳定。

与表1中其他文献对比,本次设计的低噪声放大器的增益、输入输出驻波比等指标优于其他文献中的典型Ku波段低噪声放大器,具有很好的应用前景。

表1 低噪声放大器性能对比

文献工作频带/GHz增益/dB噪声/dB驻波比 [2]14~18>17<1.3<1.8 [3]12~18>20<2.9<2 [4]13~16>22.8<1<1.7 本文13~17>23<1.8<1.58

6 结论

本文基于0.13 μm GaAs PHEMT工艺设计了一款工作频段为13~17 GHz的低噪声放大器,整体采用双电源供电的两级放大结构,用电感加并联电容的滤波结构来隔离直流信号与射频信号,第二级放大器的栅极和漏极之间加入了负反馈网络来增加稳定性、拓展带宽和改善增益平坦度。仿真结果显示,本文设计的低噪声放大器在工作频段内增益大于23 dB,增益平坦度为±1.4,噪声系数小于1.8 dB,输入驻波比小于1.58,输出驻波比小于1.45,芯片面积为(1.8×1.2) mm2,具有高增益、低噪声、面积小等优点,可应用于高性能的卫星通信收发前端。

[1]张博,张帅,吴昊谦. 一款高增益宽带低噪声放大器的设计[J]. 电子元件与材料,2022,41(3): 266-272.

[2]韩克锋,李建平. 一款Ku波段GaAs PHEMT低噪声放大器[J]. 微波学报,2017,33(4): 80-84.

[3]刘昊,彭龙新,牛超,等. Ku波段GaN单片低噪声放大器的研制[J]. 电子与封装,2017,17(6): 27-30,35.

[4]MURTHY B, SINGH N K, JHA R, et al. Ultra low noise figure, low power consumption Ku-Band LNA with high gain for space application[C]. 2020 5th International Conference on Communication and Electronics Systems, 2020: 80-83.

[5]刘如青,吴洪江,高学邦,等. Ku波段单片功率放大器设计与制作[J]. 半导体技术,2011,36(6): 470-473.

[6]祝智韬. 收发前端MMIC放大器的研究与设计[D]. 成都: 电子科技大学,2018.

[7]路德维格. 射频电路设计: 理论与应用[M]. 王子宇,译.北京: 电子工业出版社,2013.

[8]刘贤栋. 毫米波宽带低噪声放大器的研究与设计[D]. 杭州: 杭州电子科技大学,2020.

[9]管钰,李军,张大为. Ka频段GaAs MMIC低噪声放大器设计[C]. 2021年全国微波毫米波会议论文集(下册),2021: 221-223.

[10]朱丹. X波段单片低噪声放大器的研究[D]. 南京: 南京理工大学,2006.

[11]李海鸥,朱蒙洁,谢仕锋,等. 2 GHz~4.2 GHz MMIC低噪声放大器设计[J]. 中国电子科学研究院学报, 2021,16(9): 851-855,868.

[12]汪荣昌. 5G移动通信用氮化镓功率放大器的研究[D]. 南京: 南京邮电大学,2021.

Ku Band High Gain Low Noise Amplifier Based on GaAs Technology

In this paper,a MMIC low noise amplifier (LNA) is designed by using 0.13μm GaAs PHEMT technology. The operating frequency band of the LNA is 13 to 17 GHz. A two-stage amplifier structure with dual power supply is adopted. The bias circuit adopts a filter structure of inductance and parallel capacitor to isolate the DC signal from the RF signal. A negative feedback network is introduced between gate and drain of the secondary amplifier to increase circuit stability, expand amplifier bandwidth and improve gain flatness. The simulation results show that in the 13 to 17 GHz frequency band range, the noise figure of the low noise amplifier is less than 1.8 dB, the gain is greater than 23 dB, the gain flatness is ±1.4 dB, the input standing wave ratio is less than 1.58 dB, the output standing wave ratio is less than 1.45 dB, and the chip area is only 1.8 mm×1.2 mm.

GaAs PHEMT; microwave monolithic integrated circuit; low noise amplifier

TN722.3

A

1008-1151(2023)07-0001-05

2022-10-12

四川省教育厅重点项目(16ZA0172)。

贾瑞林(1998-),男,西华师范大学电子信息工程学院硕士研究生,研究方向为射频微波电路。

王云秀(1967-),女,西华师范大学电子信息工程学院教授,研究方向为射频微波电路。