基于FPGA 和ARM 内核的无线SoC 设计

2023-05-29魏继清

魏继清

(电子科技大学 电子科学与工程学院,四川成都,611731)

0 引言

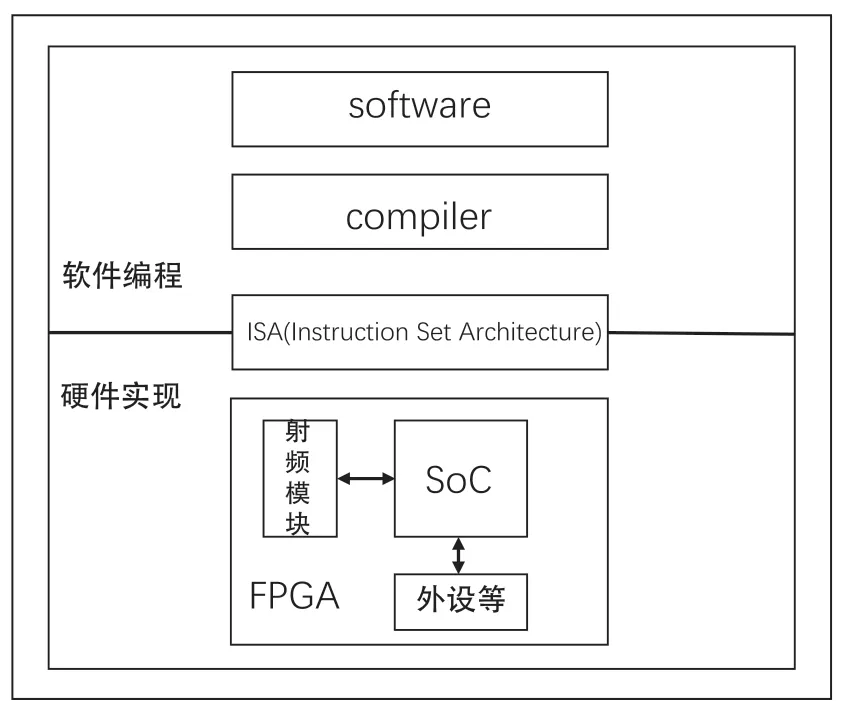

无线SoC 已成为物联网产业发展的基础,在现代信息社会中占有越来越重要的地位。但由于课程体系等多方面的原因,同时熟悉无线通信和SoC 设计的人才极为稀缺。本文基于ARM Cortex-M0 处理器在FPGA 上构建具备无线通信基带信号处理的片上系统,配合控制外围扩展电路实现FM 通信信号的调制解调等处理。在此基础上增加适当的功能以满足特定的物联网应用,使系统具有实用性、可演示性和创新性,同时兼顾了系统灵活性、可移植性、通用性的要求[1]。该系统的总体设计框图如图1 所示。

图1 无线SoC 系统框图

1 无线SoC 系统

由图1 可知,将ARM Cortex-M0 内核移植到FPGA上并在FPGA 上构建好硬件系统后,再与射频扩展模块、FPGA 板载外设模块相连接即可构成无线SoC 系统的硬件部分,还需软件和硬件协同,即可构成完成的无线SoC,二者之间通过指令集架构搭建起桥梁,如图2 所示。

图2 软硬件开发层次

整个系统的开发流程为:

(1)将ARM Cortex-M0 软核移植到FPGA 芯片上;

(2)使用Verilog 硬件描述语言搭建SoC 系统,包括搭建外设驱动、编写基带信号处理IP、连接射频扩展模块与外设模块等;

(3)在集成开发环境keil 中编写软件代码,生成十六进制机器码;

(4)将机器码下载至FPGA 中的ARM 内核中,进行仿真;

(5)烧录到FPGA 中并调试。

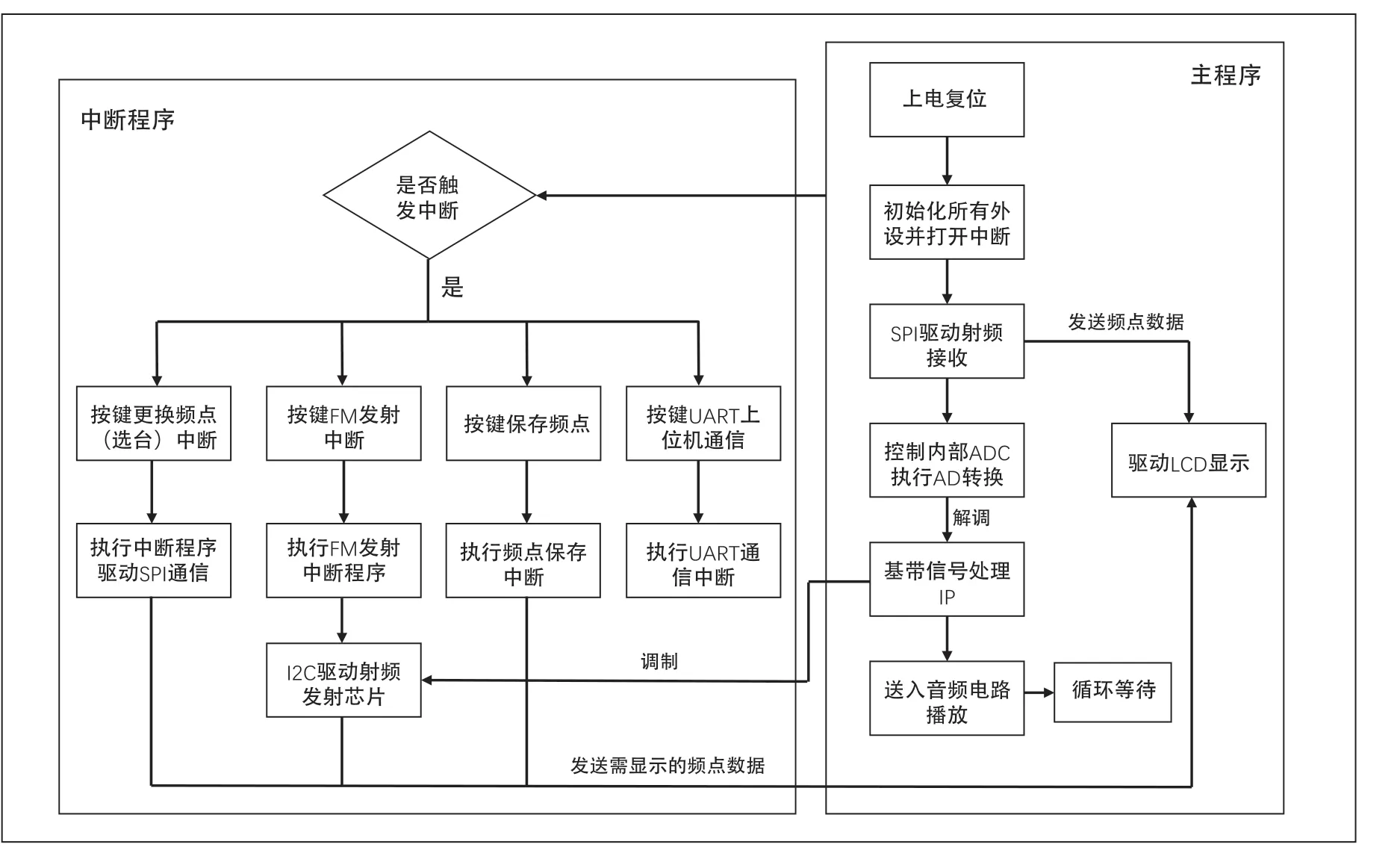

其中的软件控制流程为:该系统上电复位以后,初始化所有外设并打开中断,然后通过SPI 模块与射频接收芯片通信,来选择接收的频点,接着将接收到的FM 模拟信号送入AD 模块转换为数字信号,在基带信号处理IP 中进行FM解调,将解调后得到的数字信号经DA 转换后送入音频输出电路播放;在程序的执行过程中,随时可以通过GPIO 按键触发中断,执行对应的中断程序,中断程序的功能有:可以通过按键更换接收的频点、可以通过按键发射FM 信号、可以通过按键保存频点、可以通过按键与上位机UART 通信,将接收的频点信息发送给上位机等。软件系统控制流程如图3 所示。

图3 软件系统执行流程

2 FPGA 片上无线系统电路

2.1 ARM 内核模块

ARM 处理器采用精简指令集(RISC)处理器架构,Cortex-M 系列在低功耗、微控制系统领域应用广泛,且使用keil 集成开发环境,可迅速完成软件应用程序开发,以及实现设计代码的重用,具有极大优势[2]。Cortex-M0 微处理器包括:处理器核、嵌套向量中断控制器(NVIC)、调试子系统、唤醒中断控制器、AHB-Lite 总线接口以及连接这些单元的内部总线系统。处理器核对数据进行处理,包含内部寄存器、算术逻辑单元(ALU)、数据通路和控制逻辑,取指、译码和执行的指令通道采用三级流水结构,显著提高处理器指令通道的吞吐量和运行效率。嵌套中断向量控制器包含32 个中断请求信号,以及一个不可屏蔽中断。调试子系统用于管理调试、程序断点,以及数据监控点。唤醒中断控制器用于低功耗应用,通过关闭大部分元件,使微处理器进入休眠模式,当检测到中断事件时,通知电源管理单元上电,使处理器从休眠状态进入到正常工作状态。AHB-Lite 总线系统也与传统的总线相同,包括地址总线、控制总线和数据总线,总线用于处理器核和其他模块之间的通信,处理器核为主机,其他所有模块都为从机。该项目的FPGA 片上无线系统电路如图4 所示。

图4 FPGA 片上系统框图

2.2 基带信号处理IP 模块

基带信号处理IP 包括两个部分,一是将ADC 送过来的数字FM 调制信号进行解调;二是将麦克风电路输入的语音模拟信号经AD 转换后进行FM 调制。

2.2.1 FM 数字正交解调

软件无线电一般采用数字正交解调法,实际工程中,一般调制都能用正交调制法进行,实质上调制不外乎用调制信号去控制一个载波的某一个或几个参数,让这个给参数按照调制信号的规律变化,载波可以是正弦波或脉冲序列,以正弦信号作为载波的调制叫做连续波调制,FM 是一种连续波调制,且是对载波信号的频率进行调制的方法。对于连续波调制,以调信号的数字表达式如公式所示:

将上式和差化积后得到公式:

式中:

由于我们的射频接收芯片已经将I、Q 两路信号得出,所以我们只需要AD 转换后进行解调算法的编写即可。利用相位差分计算瞬时频率f(n)时,由于计算相位要用到除法和反正切运算,这对于非专用数字处理器来说是较复杂的,在用软件时,也可以用下面的方法来计算瞬时频率f(n):

这种方法只有乘法和减法[3],计算起来简便,最后我们仿真将其实现,如图5 所示,可知经过I、Q 两路信号解调出来的信号(倒数第二行波形)有些许高频噪声,再加上低通滤波器去除高频噪声得到最后一行波形,即解调出来的波形。

图5 FM 解调并滤波得到原信号

2.2.2 FM 数字调制

FM 调制模块有两个比较重要的概念:中心频率和频偏。频偏即与中心频率的差值。假设中心频率为5MHz,频偏为:-75kHz~75kHz,输入信号位宽为12 位。当输入调制信号幅度为0 时,输出的FM 已调信号频率为5MHz,即载波频率;当输入调制信号幅度最大(即+2^11)时,输出的FM 已调信号频率为5.075MHz(5M+75K);当输入调制信号幅度最小(即-2^11)时,输出的FM 已调信号频率为4.925MHz(5M-75K),使用DDS 控制模块可以实现FM 调制[4]。将其仿真得到如图6 所示的结果,可知送入的信号以频率为调制,即完成FM 调制。

图6 FM 调制

2.3 外设模块

搭载的外设有UART、SPI、I2C、LCD;其 中UART用于与上位机串口通信;SPI用于与射频接收芯片通信,控制接收的频段与频点等;I2C用于与射频发射芯片通信,控制发射;LCD 用于显示接收和发射的频点。

2.3.1 UART 模块

通用异步接收发送器(UART)用于实现两个设备间的异步串行通信;UART 一帧数据由起始位开始,紧跟着八位数据位(由低到高)、奇偶校验位(可选)、停止位结束。将UART 驱动连接到AHB-Lite 总线上,就可以实现SoC 与上位机之间的UART通信,硬件架构搭建完毕并成功仿真以后,在Keil 上进行软件程序的编写,编写的软件程序生成十六进制治理文件下载到Cortex-M0 内核中运行,从而可以控制UART 的发送与接收,仿真结果如图7 所示。

图7 UART 串行通信

2.3.2 SPI 模块

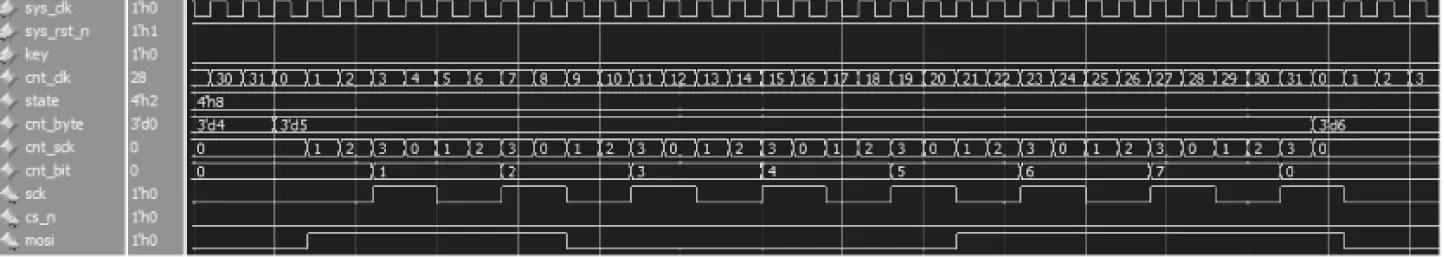

串行外围设备接口(SPI)通讯协议,是一种高速、全双工、同步通信总线,只需要四根线来控制数据传输,SPI通讯协议包含 1 条时钟信号线、2 条数据总线和 1 条片选信号线,时钟信号线为 SCK,2 条数据总线分别为 MOSI(主输出从输入)、MISO(主输入从输出),片选信号线为 CS;SPI 的优点是支持全双工通信、速率较快,缺点是没有应答机制,在数据可靠性上有一定缺陷;我们使用的射频接收芯片是MSI001,其数据格式是24bits,20bits 是数据,4bits 是寄存器地址,我们通过SPI 发送24bits 数据,控制相应的寄存器配置成不同的值,就可以选择频段与频点等;仿真结果如图8 所示。

图8 SPI 同步通信

2.3.3 I2C 模块

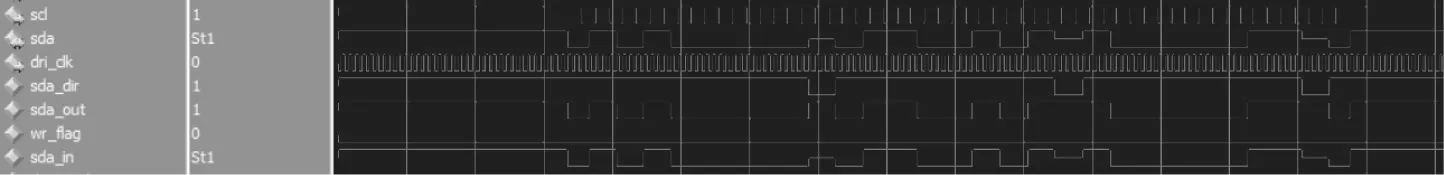

I2C 通信协议是双向二线制同步串行总线,支持一主多从,总线通过上拉电阻连接到电源,当I2C 设备空闲时,输出高阻态;当所有设备都空闲,都输出高阻态时,由上拉电阻把总线拉成高电平;每一个从机都有一个独立的地址,主机利用这个地址访问不同的设备;I2C 总线只有两条线,一条串行时钟线(SCL)用来提供时钟同步,同步数据的收发;一条串行数据线(SDA)用来读写数据,具有三种传输速率:标准模式传输速率为100kbit/s,快速模式为400kbit/s,高速模式可达3.4Mbit/s。SoC 通过I2C 控制发射芯片QN8027,将输入的模拟音频信号发射,I2C 仿真结果如图9所示。

图9 I2C 通信

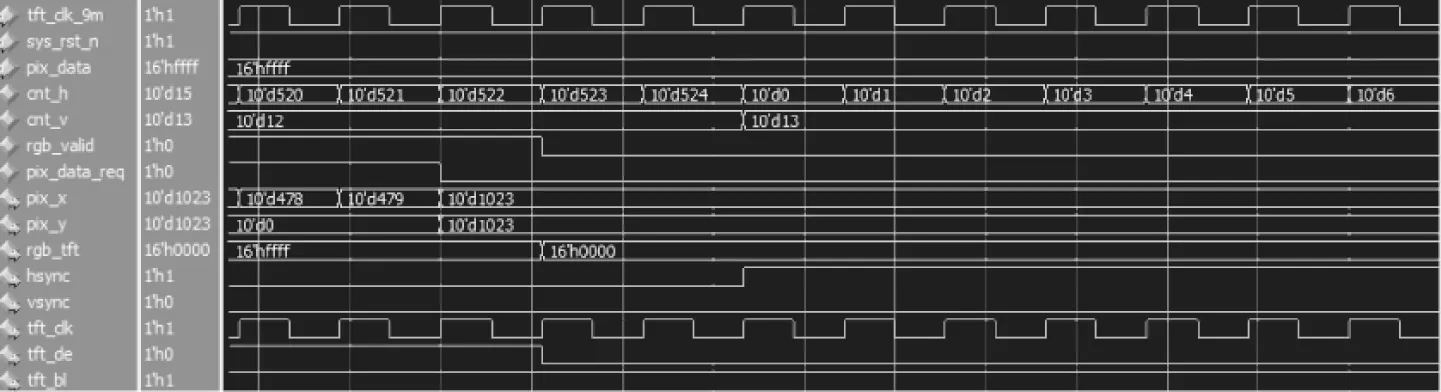

2.3.4 LCD 模块

TFT-LCD 即薄膜晶体管液晶显示器,它在液晶显示屏的每一个像素上都设置一个薄膜晶体管,可有效克服非选通时的串扰,提高了图片质量。本文使用到的2.4 寸LCD 屏采用的驱动芯片是ILI9341,且使用8080 16 位总线接口,可直插FPGA;LCD 模块使用的基本原理是,主机通过引脚向驱动芯片发送一系列指令和数据,之后驱动芯片会根据这些指令和数据刷新LCD 屏幕并进行显示。LCD 的仿真测试结果如图10 所示。

图10 LCD 模块

3 射频扩展模块

射频扩展模块使用的是DMZ_FMSDR 开发板,可以和FPGA 开发板配合使用;DMZ_FMSDR 内部包含了50MHz~120MHz,400MHz~1000MHz 射 频 接 收 电 路,76MHz~08MHz 的FM 频道发射电路,麦克风电路,音频输出和功放电路,可以通过编程实现FM 收音机、FM 发射机、FM对讲机以及其他频段的接收机。

(1)射频接收电路模块可以接收多个频段的信号,广播信号FM 在VHF 频段(64~108MHz),可以通过配置MSI001 寄存器的值来选择;经过MSI001 芯片的处理后,下变频产生I、Q 两路信号,送到FPGA 的AD 接口;

(2)FM 频道发射电路模块发射频率覆盖76MHz~108MHz,支持立体声或单声道,输出接拉杆天线,通过配置QN8027 的寄存器来配置发射频点、时钟选择、音频信号处理等,其他可用默认值,实现FM 发射;

(3)麦克风电路模块在射频板上有3.5mm 接口的麦克风输入插口,从而可以实现模拟音频信号的输入;

(4)音频输出和功放电路模块,可以外接音箱、耳机或喇叭(右声道)即可实现音频的输出。

将射频扩展模块开发板的各个模块与FPGA 片上系统相应的接口相连后,就可以通过软件下载到FPGA 片上系统上控制射频扩展模块,从而实现FM 射频接收与发射、音频播放、麦克风输入等功能。

4 结语

本文设计了一款基于ARM 处理器的无线SoC,该系统将Arm Cortex-M0 内核移植到FPGA,能够实现FM 广播信号接收、FM 信号调制解调、FM 广播信号播放、FM 信号发射(对讲)、LCD 显示频段频点、与上位机串口通信等功能。此外,因为FPGA 的可编程性,电路具有很强的扩展性,可以增加许多功能模块,比如存储频道、手动选台、实时以太网传输、实时USB 传输、录音存储等功能。